安捷伦科技公司(NYSE:A)在DesignCon上展示增强的PCI Express® 3.0 接收机特性测试解决方案。

Agilent PCIe® 3.0 接收机特性测试解决方案可以提供完整、精确的接收机容限测试结果,同时最大程度地减轻研发人员的工作量。新型J-BERT 软件(版本7.40)在对PCIe 3.0 接收机设计进行测试时,可以调整128b/130b 编码后的填充符的长度(又称为SKP 有序集,用于补偿收发端的时钟差异)。

借助安捷伦测试仪,半导体和计算机领域中的设计与测试工程师能够精确地表征和验证在ASIC、插卡和主板中的PCIe 接收机端口是否符合标准。

自从PCI Express 版本3.0 发布以后,8 GT/s 接口被应用到多个计算机平台。PCIe 设计一般使用公共参考时钟,但是越来越多的设计现在要求使用具有独立扩频时钟(SSC)的参考时钟体系结构,例如通过电缆连接的PCIe 链路。当使用独立的参考时钟时,设计人员需要对发射端和接收端之间的时钟速率差值进行补偿,以避免缓冲区溢出。即使主板上是使用公共参考时钟,当存在SSC 或使用乘法锁相环时,也需要进行时钟补偿。根据PCI Express 标准的规定,是通过在正常的SKP 有序集中添加(或移除)SKP 符号来实现这种补偿。

在接收端测试中,当环回模式中的被测器件改变了SKP 有序集长度时,新型Agilent J-BERT N4903B 高性能串行比特误码率测试仪软件仍可以执行接收机测试。J-BERT 误码检测器在统计误码数量时可以忽略SKP 有序集,即使有序集的长度不符合码型发生器发出信号里的初始长度。在做调试时,工程师还可通过误码仪里的误码检测器来监测SKP 有序集的计数。

安捷伦数字光学测试部门的战略产品规划师Michael Fleischer-Reumannr 表示:“安捷伦解决方案能够处理PCIe 3.0 SKP 有序集在接收机抖动容限表征过程中的长度变化,这一优势填补了PCIe 3.0 芯片组和电路板设计人员的需求空白。J-BERT 提供灵活的体系结构,融合了安捷伦在PCI Express 接收机测试方面的专业经验,使我们足以应对新兴的测试挑战。”

借助这个增强型解决方案,安捷伦进一步完善了其完整、精确的PCIe 3.0 接收机测试解决方案,使其根据基本规范和卡机电规范进行表征。

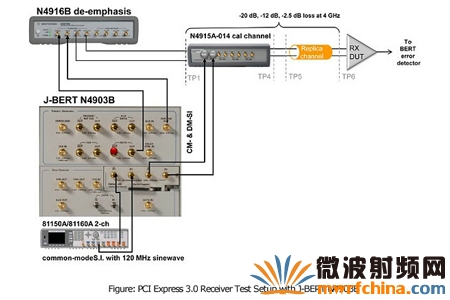

安捷伦接收机测试解决方案包括J-BERT N4903B 高性能串行BERT、N4916B 去加重信号转换器、N4915A-014 PCIe 3.0 一致性校准通道、81150A 或81160A 脉冲函数任意噪声发生器、Infiniium 90000 或90000 X 系列高性能示波器、N5990A-101 和N5990A-301 测试自动化和链路训练软件。N4880A 参考时钟倍频器可用于主板测试。

Agilent PCIe 3.0 接收机表征解决方案的优势在于:

• 在统计误差数量时可以忽略SKP 有序集的长度变化,从而对具有公共参考时钟和单独参考时钟的PCIe 接收机进行测试。

• 通过启用压力信号校准软件、可调节的前光标和后光标去加重、J-BERT 内置PCIe 3.0 一致性抖动和正弦干扰源、周期抖动扫描功能、100-MHz 参考时钟倍频器以及PCIe 3.0 一致性校准通道,可获得精确且可重复的接收机测试结果。

• PCIe 3.0 压力信号校准和接收机自动化测试软件以及PCIe 3.0 链路训练套件能够控制J-BERT 中的码型序列发生器,使被测器件进入环路模式,从而提高研发效率。

• 通过扩展,可对多种Gbit量级的总线应用进行精确特性测试(例如USB、SATA、MIPI M-PHY、TBT 和QPI),从而能够保护您的投资。

安捷伦将在DesignCon 2013 上展示PCI Express 3.0 增强型接收机表征解决方案(展位201)。本届展会于1 月28 日至31 日在圣克拉拉会议中心举办。安捷伦将提供广泛的高速数字解决方案,其中一些主要工具可用于查明问题、优化器件并且交付设计与仿真结果。

安捷伦数字测试标准计划

安捷伦数字测试标准计划的专家积极参加各个国际标准组织,其中包括电子器件工程联合会、PCI-SIG®、视频电子标准协会、串行ATA 国际组织、串行连接SCSI(T10)、USB 应用厂商论坛、MIPI 联盟、以太网标准(IEEE 802.3)、光互联论坛等等。安捷伦积极参与这些标准组织的活动,以便安捷伦能够在客户需要时将适当的解决方案推向市场。

粤公网安备 44030902003195号

粤公网安备 44030902003195号