射频和无线产品领域可以使用非常广泛的封装载体技术,它们包括引线框架、层压基板、低温共烧陶瓷(LTCC)和硅底板载体(Si Backplane)。由于不断增加的功能对集成度有了更高要求,市场对系统级封装方法(SiP)也提出了更多需求。

引线框架基板封装技术在过去的几年中得到了巨大的发展,包括刻蚀电感、引脚上无源器件、芯片堆叠技术等等。框架基板是成本最低的选择,但是更高的功能性要求更多的布线和更多的垂直空间利用,因而,框架封装很少用在RF集成解决方案中。

LTCC因其具有多层结构、高介电常数和高品质因子电感,已经被证明是一种能提供高集成度的高性能基板材料。LTCC方案中实现了无源器件的嵌入,如独立RCL或包含RCL的功能块,使SMT器件所需平面空间最小,同时提高电性能。集成度是LTCC的优点,然而翘曲、裂纹、基板的二级可靠性、以及整个供应链结构(基板在封装过程中的传送)等等对LTCC的局限,使之无法成为流行的载体基板选择。

硅底板载体,如STATS ChipPAC的芯片级模块封装(CSMP:Chip Scale Module Package),已经广泛地使用于需要高集成度、卓越电性能和小外形系数的无线解决方案中。CSMP是一种全集成解决方案的理想封装形式,可以包括RFIC和基带IC。然而,这样的集成度并不是成本最低的,而且也不是所有的射频和无线设备都需要的。

这些原因将我们引向层压基板,一种在射频模块封装中应用最广泛的载体。该方法结合了传统的层压基板技术与无源器件集成技术(IPD:Integrated Passive Device),成为一种在成本、尺寸、性能与灵活性诸方面能达到最佳平衡的双赢解决方案。本文对带IPD器件的层压基板的应用进行讨论,同时通过两个例子来进一步阐述研究。

IPD与SMD 和LTCC分立器件电路的对比

射频模块需要用到独立的RCL或组合的RCL,来实现诸如滤波器、天线分离滤波器(diplexer)、不平衡变压器(balun)等的功能块,这些RCL通常为SMD(Surface Mount Devices表面贴装器件)形式或IPD形式。

传统的层压基板不能很好地适用于嵌入式无源器件,而高介电材料层压又受到很大成本限制。螺旋电感可以设计在层压基板的内部,但是电感值却有限。因此,在使用层压基板时,更倾向于结合SMT器件和IPD,这样具有成本、外形尺寸和性能等等方面的优势。

对于何时使用表面贴装器件、何时将特定的无源器件设计成IPD更合理,需要进行权衡。例如,当需要大于100.0pF的电容器设计时,使用SMT器件就具有尺寸与成本的优势。

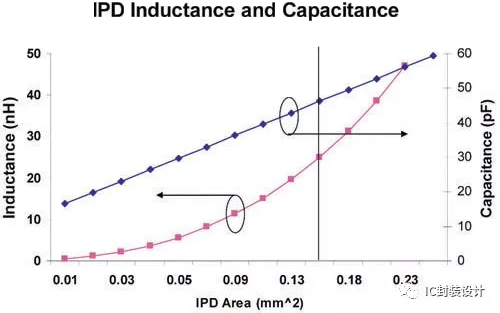

另外,当设计中需要比较少量的解耦电容器或独立电感和电阻时,通常推荐使用SMT无源器件方式。表面贴装器件可以充分利用所占空间的Z方向,而IPD则主要利用XY方向,后者对Z高度方向的空间利用很有限,因此,当IPD器件表面面积超出可利用的空间,使用表面贴装元件就比较明智。为了找到在IPD和SMT器件之间最佳平衡,我们研究出可以描述器件值与IPD需要的面积关系的曲线(图1)供设计参考。

图1、在硅基板上制作的IPD的电感和电容

使用硅基IPD技术,一个0201 SMD器件的面积(0.15mm2)内可以产生25.0nH的电感,或者50.0pF的电容。换言之,对于容量小于25.0nH的电感或小于50.0pF的电容,IPD器件/电路方案的外形尺寸比0201器件更小。

当涉及到射频功能块时,IPD方案常常会胜出,其中有多种原因。首先,尽管硅基IPD制成的电感也必须使用螺旋形式,但它可以使用更小的线宽和隔离空间。另外,高电阻的硅基片上允许制成具有更高品质因子的电感。因而,一个IPD电感的质量和外形系数可以与SMD器件媲美;第二,电容尤其是小容量电容(RF应用中)更容易建在IPD中;最后,与PCB上连接SMD器件,或者LTCC内部连接相比较,硅基板上的互连路径更短。

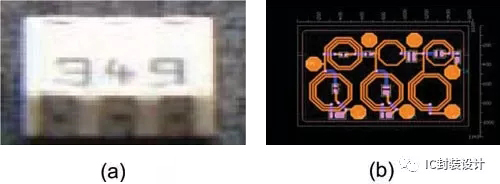

这里有一个例子,对于一个超宽频(UWB)应用滤波器,现有的LTCC滤波器尺寸是3.2mm×2.5mm×0.8mm,如果在IPD中使用相同的布局来实现,尺寸将会是1.6mm×1.0mm×0.5mm(图2)。IPD滤波器除了具有更薄的外形以外,尺寸缩小了5倍。

图2、LTCC滤波器(a)和IPD滤波器(b)尺寸比较

我们也对其它情况进行了比较,总而言之,对于滤波器(比如LPF 或BPF),IPD可以获得小五倍的外形,对于不平衡变压器,使用IPD的外形可小两倍。

另外还有一种方法,通过使用嵌入式电感(层压板内部)和SMT电容来制作滤波器这类功能块。这样做的结果是,除了占用面积超过LTCC或IPD以外,在性能方面也有局限。此外,由于组装一个整体的集成功能块的过程被拆分成两部分(PCB电感和SMT电容),封装要获得好的良率就必须对组装工艺提出更严格的要求。

SMT器件具有大小不同的尺寸。在射频模块应用中,当前最常用的是0201。更小尺寸的01005器件刚刚出现,但是它们通常比较昂贵而且器件值也有限。这些SMT器件的贴放通常使用高速贴片机,然后通过回流焊接在层压板上。

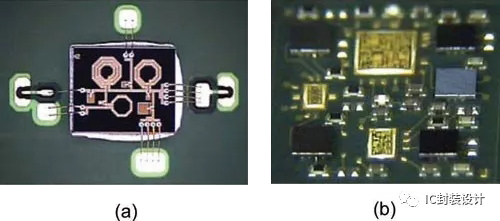

图3、一个RF模块中,IPD键合在层压基板上(a),或IPD倒装在基板上

IPD可以是裸芯片形式或凸点器件,然后通过引线键合或倒装焊接到基板上(图3)。凸点IPD芯片可以和SMT器件一起使用高速贴片机进行贴放,贴装完成后,其它芯片可以通过引线键合直接放到基板上。

示例研究#1——GSM匹配电路

在一个RF接收器中,需要使用一些匹配电路,来提高PA和LNA这些有源电路的性能。这些匹配电路包括RCL器件。由于考虑成本和性能,这些RCL器件可以从芯片中去除,并通过SMD或IPD形式实现。

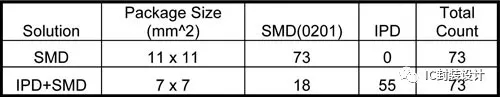

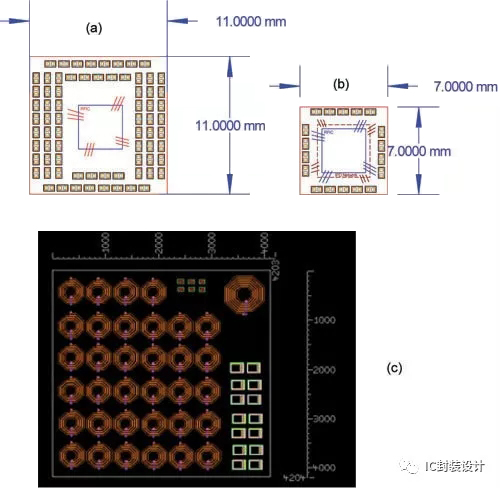

我们对一个客户的GSM传送模块使用片外匹配器,并进行了对比研究。在该模块中,有73个用于匹配电路和DC解耦的无源器件,如果只使用SMD元件(假设所有器件可选用0201),封装尺寸将是11mm×11mm。然而,如果某些器件用IPD形式实现,模块的尺寸可以得到明显的缩小(表1)。

表1、SMD和IPD方案封装尺寸的比较

对于这些GSM的低频(860MHz)和高频(1800MHz)匹配器,IPD方法非常适合。除了一些大容量的解耦电容,55个RCL可以制作在一个尺寸更小的IPD网络中,封装大小可以达到7mm×7mm。为了简化,布线的复杂度在所有的示例中没有考虑。

应当注意到,IPD网络是被当作一个集成芯片来对待的,因为它的外形系数和厚度都与一个集成电路相近。IPD网络与传送芯片堆叠,虽然增加了模块的厚度,但由于IPD仅仅0.25mm厚,对厚度的增加没有明显的影响。因此,IPD封装堆叠节省了空间,并可以通过引线键合或者倒装焊的形式,堆叠在另外一个芯片的上方或下方。

示例研究#2 ——GSM不平衡变压电路(Balun Circuits)

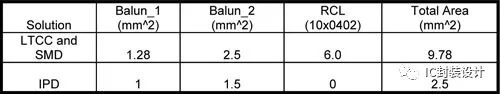

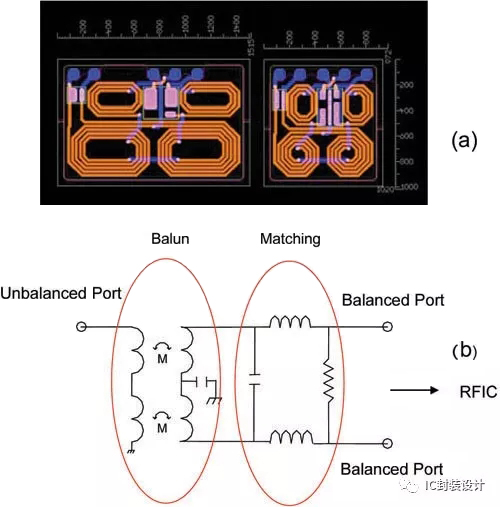

为了抑制噪声和提高PA性能,常常对PA采用微分输出设置,因而,需要一个变压器,来将单步端转换到微分端。然而,业界能提供的变压器具有固定的阻抗变压比,例如50.0~100.0Ω变压器或50.0~200.0Ω变压器。大多数的PA具有低的输出阻抗,以传送高功率。这就需要在变压器和PA之间设置一个匹配电路,如图5(b)所示。在该例中,功率放大器(PA)输出匹配电路和变压器功能块,被用来展示使用IPD技术的功效。

图4、两种方案的封装比较

应用中有GSM低频(860MHz)和GSM高频(1800MHz)电路。对每个频带,有一个匹配电路和一个变压器,将一个微分功放输出转换到单步端输出(50.0Ω)。该产品现有形式中,客户使用了标准芯片多层LTCC变压器,尺寸分别为2.0mm×1.25mm×0.95mm和1.6mm×0.8mm×0.6mm。由于标准的变压器有50.0~200.0Ω阻抗转换,和特定的功放输出阻抗不匹配,该模块需要一个独立的匹配电路(4 RCL器件)在功放和变压器之间。现有的LTCC+SMD的解决方案如表2所示。

表2、使用IPD和分离器件的面积比较

由于可以设计一个IPD变压器来匹配任何的功放输出阻抗,因此没有必要使用独立的匹配电路(每个频带4个RCL)。换言之,匹配功能可以嵌入到Balun变压器中。IPD方案的整体尺寸为2.5mm2,大约比现有的LTCC+SMD方案的尺寸小四倍。除此之外,IPD匹配器和变压器电路只有大约0.25mm高,这也比离散的LTCC器件薄。

图5、(a)GSM高低频段中的IPD Balun。尺寸为1.5mmX1.0mm和1.0mmX1.0mm。匹配的功能已经嵌入在Balun变压器中;(b)输出匹配电路和变压器功能块解决方案示意

该IPD解决方案完全去除了在匹配器和变压器模块中使用SMD器件,它不仅使面积缩小了四倍,而且大大降低了封装过程的成本。由于其集成在一个IPD模块中,而非使用一个LTCC分离器件Balun变压器和四个RCL,良率和工艺变化的影响都得到改善。

结论

关于射频封装的理想解决方案近年来有许多研究,最重要的是要在成本、体积和性能需求之间谋求平衡。尽管引线框架技术中已取得显著的进展,而LTCC基板性能也已经得到提升,但是,在绝大多数的应用中,使用IPD集成和层压基板的技术还是最好的整体解决方案。

层压基板低成本、灵活性高、具有成熟的供应链和快速的制造周期。IPD可以制作出卓越的射频功能块,并能够象芯片或SMT器件一样方便地贴装在层压基板上。将层压基板和IPD结合在一起,为射频解决方案提供了一个非常广阔的范围。本文中所研究的两个GSM应用实例,仅仅在于说明典型的尺寸缩减,该技术同样可以应用在移动电视、GPS、WLAN和WiMax等设备的射频电路应用中。

作者:Kai Liu, Eric Gongora,STATS ChipPAC

粤公网安备 44030902003195号

粤公网安备 44030902003195号