йҡҸзқҖйӣ·иҫҫе’Ңж— зәҝйҖҡдҝЎзі»з»ҹдёӯзҡ„дҝЎеҸ·еӨ„зҗҶд»ҺжЁЎжӢҹиҪ¬еҗ‘ж•°еӯ—пјҢе·Із»ҸдёәејҖеҸ‘е…Ҳиҝӣзҡ„жіўжқҹеҪўжҲҗжҠҖжңҜе®һзҺ°ж–°зҡ„еә”з”Ёд»ҳеҮәдәҶе·ЁеӨ§зҡ„еҠӘеҠӣгҖӮеҝ«йҖҹеӮ…з«ӢеҸ¶еҸҳжҚўжҳҜжңҖеёёи§Ғзҡ„дёҖз§ҚдҪҝз”Ёж•°еӯ—ж–№жі•зІҫзЎ®еј•еҜјжіўжқҹиғҪеҠӣзҡ„ж–№жі•пјҢиҝҷеҜјиҮҙйӣ·иҫҫе’ҢйҖҡдҝЎзі»з»ҹзҡ„и®ҫи®Ўж–№ејҸеҸ‘з”ҹдәҶйҮҚеӨ§еҸҳеҢ–гҖӮ

жіўжқҹжҲҗеҪўжҠҖжңҜеҸҜеҲҶдёәиҮӘйҖӮеә”жіўжқҹжҲҗеҪўе’ҢеҲҮжҚўжіўжқҹжҲҗеҪўжҠҖжңҜгҖӮеңЁеҲҮжҚўжіўжқҹжҲҗеҪўдёӯпјҢдҫӢеҰӮпјҢйҖҡдҝЎеҹәз«ҷд»Һйў„и®ҫзҡ„жіўжқҹдёӯйҖүжӢ©жіўжқҹпјҢжҜҸдёӘжіўжқҹеҹәдәҺжҺҘ收дҝЎеҸ·зҡ„ејәеәҰжқҘжҢҮеҗ‘зү№е®ҡж–№еҗ‘гҖӮеҪ“з”ЁжҲ·зӣёеҜ№дәҺеӨ©зәҝйҳөеҲ—移еҠЁж—¶пјҢдҝЎеҸ·иў«еҲҮжҚўеҲ°йҳөеҲ—дёӯзҡ„е…¶д»–йҳөе…ғдёҠпјҢиҝҷдәӣйҳөе…ғеҸҜд»ҘжӣҙеҘҪең°еңЁзү№е®ҡж–№еҗ‘дёҠжҸҗдҫӣжӣҙејәзҡ„дҝЎеҸ·гҖӮ

иҮӘйҖӮеә”жіўжқҹжҲҗеҪўжҠҖжңҜеңЁеҸҰдёҖж–№йқўдҫқиө–дәҺе®һж—¶и®Ўз®—пјҢиҝҷжҳҜдёҖз§Қе…Ғи®ёеҹәз«ҷеңЁзӣ®ж Үз”ЁжҲ·зҡ„ж–№еҗ‘дёҠеҸ‘йҖҒжӣҙиҒҡз„Ұзҡ„жіўжқҹпјҢеҗҢж—¶еҮҸе°‘е…¶д»–ж–№еҗ‘дёҠзҡ„иҫ“еҮәпјҢд»ҺиҖҢеӨ§еӨ§еҮҸе°‘йҳөе…ғй—ҙе№Іжү°гҖӮ

иҮӘйҖӮеә”жіўжқҹжҲҗеҪўи®ҫи®ЎйңҖиҰҒжӣҙй«ҳзҡ„еӨ„зҗҶеёҰе®ҪпјҢжҜҸз§’еҝ…йЎ»жү§иЎҢж•°еҚҒдәҝж¬Ўд№ҳжі•е’ҢзҙҜеҠ иҝҗз®—гҖӮеӣ жӯӨпјҢе®ғеңЁжҺҘ收з«ҜжҠ‘еҲ¶еҷӘеЈ°жәҗе’Ңе№Іжү°ж–№йқўеҸҳеҫ—йқһеёёйҮҚиҰҒгҖӮеҗҢж—¶пјҢеҝ…йЎ»дҝқжҢҒеӨ©зәҝйҳөеҲ—дёӯжҜҸдёӘйҳөе…ғзҡ„е®һж—¶ж–№еҗ‘жҺ§еҲ¶гҖӮдёәдәҶе®һзҺ°иҝҷдёҖзӮ№пјҢжңүеҝ…иҰҒдҪҝз”Ёйҳөе…ғзә§еӨ„зҗҶжқҘеҚ•зӢ¬ең°е’ҢеҗҢж—¶ең°еҜ№жҜҸдёӘеӨ©зәҝйҳөе…ғжҺҘ收зҡ„дҝЎеҸ·иҝӣиЎҢж•°еӯ—еӨ„зҗҶгҖӮ

з”ұдәҺйңҖиҰҒеӨ§йҮҸзҡ„и®Ўз®—иҙҹиҚ·пјҢдј з»ҹзҡ„CPUе’ҢDSPеңЁиҮӘйҖӮеә”жіўжқҹжҲҗеҪўеә”з”ЁдёӯеҸҜиғҪдјҡиҝ…йҖҹиҙҹжӢ…иҝҮйҮҚгҖӮ然иҖҢпјҢз”ұдәҺе…¶еөҢе…ҘејҸDSPжЁЎеқ—пјҢ并иЎҢеӨ„зҗҶжһ¶жһ„е’Ңеўһејәзҡ„еӯҳеӮЁеҷЁеҠҹиғҪпјҢе…·жңүжӣҙй«ҳжҖ§иғҪзҡ„FPGAйқһеёёйҖӮеҗҲиҝҷйЎ№д»»еҠЎгҖӮ

е…ЁзҗғеҜ№з§»еҠЁе®ҪеёҰж•°жҚ®е’ҢиҜӯйҹіжңҚеҠЎйңҖжұӮзҡ„дёҚж–ӯеўһй•ҝпјҢдҝғдҪҝж— зәҝзҪ‘з»ңиҝҗиҗҘе•ҶйңҖиҰҒдёҚж–ӯжү©еұ•е’ҢеҚҮзә§д»–们зҡ„зҪ‘з»ңпјҢд»ҘжҸҗдҫӣжӣҙеӨҡе®№йҮҸгҖӮиҝҗиҗҘе•ҶжӯЈеҠӘеҠӣе°ҶжҜҸдёӘж— зәҝеҹәз«ҷеҸҜж”ҜжҢҒзҡ„з”ЁжҲ·ж•°йҮҸжңҖеӨ§еҢ–зҡ„еҗҢж—¶пјҢйҷҚдҪҺеҹәзЎҖи®ҫж–ҪжҲҗжң¬пјҢ并дёәз”ЁжҲ·дҝқжҢҒжһҒе…·еҗёеј•еҠӣзҡ„д»·ж јзӮ№гҖӮ

з”ұдәҺеҸҜз”Ёж— зәҝйў‘и°ұзҡ„ж•°йҮҸжңүйҷҗпјҢиҝҷз§ҚеҠӘеҠӣеҸҳеҫ—еӨҚжқӮпјҢеӣ жӯӨеўһеҠ зҡ„жөҒйҮҸдјҡдә§з”ҹжӣҙеӨҡзҡ„е№Іжү°пјҢ并且з”ұдәҺеӨ©зәҝжҠҖжңҜзҡ„йҷҗеҲ¶пјҢе‘јеҸ«иҙЁйҮҸйғЁеҲҶдјҡеҸ—еҲ°еҪұе“ҚгҖӮе…Ёеҗ‘еӨ©зәҝйҖҡеёёз”ЁдәҺиңӮзӘқеЎ”дёҠзҡ„еҸ‘е°„е’ҢжҺҘ收гҖӮ然иҖҢпјҢеңЁиҝҷз§Қдј з»ҹзҡ„ж–№жі•дёӯпјҢеӨ©зәҝе……еҪ“жҚўиғҪеҷЁпјҢе°Ҷз”өзЈҒиғҪиҪ¬еҢ–дёәз”өиғҪпјҢж•ҲзҺҮдҪҺпјҢ并且еҸ—еҲ°й«ҳеәҰе№Іжү°зҡ„еҪұе“ҚпјҢз”ұдәҺеҚ•дёӘеЎ”дёҠеӯҳеңЁеӨҡз§ҚдҝЎеҸ·пјҢжүҖд»Ҙе№Іжү°дјҡйҷҚдҪҺж•ҙдҪ“иҝһйҖҡжҖ§гҖӮ

йҖҡиҝҮдҪҝз”ЁеңЁеҗҢдёҖеЎ”дёҠз»„еҗҲеңЁдёҖиө·зҡ„е®ҡеҗ‘жүҮеҪўеӨ©зәҝпјҢеҸҜд»ҘеҮҸиҪ»иҝҷз§Қе№Іжү°гҖӮиҝҷдәӣиҮӘйҖӮеә”йҳөеҲ—еӨ©зәҝжҲ–жҷәиғҪеӨ©зәҝе·Іи¶ҠжқҘи¶ҠеӨҡең°з”ЁдәҺз”өдҝЎзҪ‘з»ңдёӯпјҢд»Ҙж”№е–„ж— зәҝиҝһжҺҘиҙЁйҮҸ并жҸҗй«ҳж•ҙдҪ“е®№йҮҸгҖӮ

иҝҷжҳҜйҖҡиҝҮжіўжқҹжҲҗеҪўжҠҖжңҜе®һзҺ°зҡ„пјҢиҜҘжҠҖжңҜйҖҡиҝҮдҪҝз”Ёе…Ҳиҝӣзҡ„ж•°еӯ—дҝЎеҸ·д»Һеҗ„дёӘз”ЁжҲ·зҡ„еҹәз«ҷеј•еҜјжіўжқҹеӨ„зҗҶгҖӮжіўжқҹжҲҗеҪўи°ғж•ҙжҜҸдёӘиҫ“е…Ҙе’Ңиҫ“еҮәдҝЎеҸ·зҡ„еҠҹзҺҮе’ҢзӣёдҪҚпјҢд»Ҙдә§з”ҹжІҝзү№е®ҡж–№еҗ‘дј ж’ӯзҡ„жіўжқҹпјҢеҗҢж—¶еҮҸе°‘йқһеҝ…иҰҒиҫ“еҮәгҖӮиҝҷеҮҸе°‘дәҶеҗ„дёӘдҝЎеҸ·зӣёдә’д№Ӣй—ҙзҡ„е№Іжү°пјҢ并жҸҗй«ҳдәҶжүҖжңүиҝһжҺҘзҡ„иҙЁйҮҸгҖӮ

еҲӣж–°зҡ„иҮӘйҖӮеә”жіўжқҹеҪўжҲҗз®—жі•зҡ„еҮәзҺ°еҜјиҮҙжө®зӮ№иҝҗз®—еңЁдҝЎеҸ·еӨ„зҗҶдёӯзҡ„дҪҝз”ЁеўһеҠ пјҢд»ҺиҖҢйҖҡиҝҮе®һзҺ°зӣ®ж Үзҡ„е®һж—¶и·ҹиёӘжқҘжңҖе°ҸеҢ–е№Іжү°е№¶жҸҗй«ҳйӣ·иҫҫе®№йҮҸгҖӮиҝҷжҳҜйҖҡиҝҮдҪҝз”ЁиҜёеҰӮQRеҲҶ(QRD)е’ҢжқғйҮҚеҸҚеҗ‘жӣҝжҚў(WBS)зҡ„з®—жі•еҗҢж—¶еҗҢж—¶еҲӣе»әеӨҡдёӘзӮ№жіўжқҹжқҘе®һзҺ°зҡ„гҖӮ

иҝҷдәӣз®—жі•жңүеҠ©дәҺиҮӘйҖӮеә”ең°еҪўжҲҗжіўжқҹпјҢеҗҢж—¶йҷҚдҪҺеҷӘеЈ°е’Ңе№Іжү°пјҢдҪҶе®ғ们жҜҸз§’йңҖиҰҒиҝӣиЎҢеӨ§йҮҸзҡ„жө®зӮ№ж“ҚдҪңгҖӮ

з”ұдәҺи®ёеӨҡйӣ·иҫҫзі»з»ҹзҡ„е°әеҜёпјҢйҮҚйҮҸе’ҢеҠҹзҺҮеҸ—еҲ°йҷҗеҲ¶пјҢдҪҝз”Ёдј з»ҹзҡ„CPUжҲ–GPU并дёҚжҳҜжңҖдҪіж–№жі•пјҢеӣ дёәжү§иЎҢжө®зӮ№и®Ўз®—жүҖйңҖзҡ„硬件数йҮҸеўһеҠ гҖӮз”ұдәҺйңҖиҰҒжӣҙеӨҡзҡ„еӯҳеӮЁеҷЁпјҢеҠҹзҺҮе’Ңз©әй—ҙпјҢеӣ жӯӨдҪҝз”ЁеӨҡдёӘCPUеҜ№йӣ·иҫҫзі»з»ҹзҡ„и®ҫи®Ўе…·жңүйҮҚеӨ§еҪұе“ҚпјҢжӣҙдёҚз”ЁиҜҙжӣҙй«ҳзҡ„жҲҗжң¬пјҢжӣҙеӨҚжқӮзҡ„зі»з»ҹи®ҫи®Ўе’Ңжӣҙй•ҝзҡ„йӣҶжҲҗж—¶й—ҙгҖӮеҹәдәҺCPUзҡ„иҝӣдёҖжӯҘи®ҫи®ЎеҸ—еҲ°жңүйҷҗеҶ…еӯҳе’ҢжҺҘеҸЈйҖүжӢ©зҡ„йҷҗеҲ¶гҖӮ

FPGAйҮҮз”Ёе…Ҳиҝӣзҡ„ж•°еӯ—жіўжқҹжҲҗеҪўжҠҖжңҜпјҢеҸҜд»ҘйҷҚдҪҺжҲҗжң¬пјҢеӨҚжқӮжҖ§пјҢеҠҹиҖ—е’ҢдёҠеёӮж—¶й—ҙпјҢеӣ жӯӨдёҺйҮҮз”Ёе…Ҳиҝӣж•°еӯ—жіўжқҹжҲҗеҪўжҠҖжңҜзҡ„йӣ·иҫҫзі»з»ҹдёӯзҡ„CPUе’ҢGPUйҖүйЎ№зӣёжҜ”е…·жңүе·ЁеӨ§зҡ„дјҳеҠҝгҖӮз”ұдәҺFPGAе…·жңүеңЁиҮӘйҖӮеә”жіўжқҹжҲҗеҪўеә”з”ЁдёӯеӨ„зҗҶй«ҳеәҰ并иЎҢжө®зӮ№иҝҗз®—зҡ„еҚ“и¶ҠиғҪеҠӣпјҢеӣ жӯӨFPGAеҸҜд»ҘжҸҗй«ҳз®—жі•жҖ§иғҪпјҢеҗҢж—¶жҳҫи‘—йҷҚдҪҺеҠҹиҖ—гҖӮ

FPGAд№ҹжҳҜдёҖз§Қжӣҙжңүж•Ҳзҡ„йҖүжӢ©пјҢеӣ дёәеҚ•дёӘеҷЁд»¶йҖҡиҝҮеӨ©зәҝйҳөдёӯжҜҸдёӘйҳөе…ғжҚ•иҺ·зҡ„дҝЎеҸ·еңЁPCIeе’ҢдёІиЎҢRapidIOзӯүI / Oж ҮеҮҶдёҠжҺҘ收е’ҢеӨ„зҗҶеӨ§йҮҸж•°жҚ®пјҢйҷӨдәҶжҸҗдҫӣжӣҙй«ҳжҖ§иғҪзҡ„еӨ„зҗҶд№ӢеӨ–пјҢиҝҷж ·зҡ„зі»з»ҹиҝҳж¶ҲйҷӨдәҶеҜ№йңҖиҰҒи¶…иҝҮ1000з“ҰеҠҹзҺҮзҡ„VPXжңәз®ұдёӯе®№зәізҡ„еӨ§йҮҸиҖ—з”өпјҢеӨҡж ёCPUжқҝзҡ„йңҖжұӮгҖӮз®ҖеҢ–зҡ„еҚ•FPGAи®ҫи®ЎиҝҳеҸ—зӣҠдәҺеӨ–йғЁеӯҳеӮЁеҷЁе’ҢеҚ•жқҝдёҠзҡ„е…¶д»–йўқеӨ–еҠҹиғҪпјҢеҠҹиҖ—дҪҺдәҺ80з“ҰгҖӮ

ж•°еҚҒе№ҙжқҘеңЁеҶӣдәӢе’ҢеӣҪйҳІеә”з”ЁдёӯпјҢеёёи§Ғзҡ„жҷәиғҪеӨ©зәҝе’ҢиҮӘйҖӮеә”жіўжқҹжҲҗеҪўзҡ„дҪҝз”ЁеңЁе•ҶдёҡиңӮзӘқзҪ‘з»ңдёӯ并дёҚе№ҝжіӣпјҢзӣҙеҲ°зӣёеҜ№жңҖиҝ‘пјҢз”ұдәҺдёҺе№ҝжіӣйғЁзҪІзӣёе…ізҡ„иҝҮй«ҳжҲҗжң¬гҖӮ йҡҸзқҖдҪҺжҲҗжң¬FPGAе’ҢDSPзҡ„е…ҙиө·пјҢиҮӘйҖӮеә”жіўжқҹжҲҗеҪўеңЁ2000е№ҙд»Јж—©жңҹиҝӣе…Ҙ3G移еҠЁеҹәзЎҖи®ҫж–ҪпјҢиҜҘжҠҖжңҜзҺ°е·Іе№ҝжіӣз”ЁдәҺжү©еұ•4GзҪ‘з»ңгҖӮ

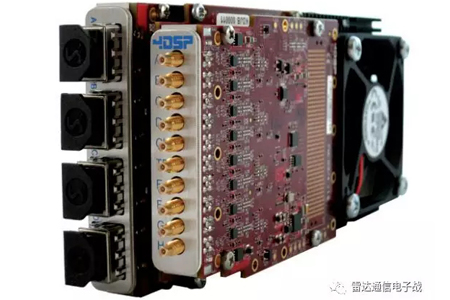

дҪҝз”ЁдёҺFPGAжқҝеҚЎзҙ§еҜҶиҖҰеҗҲзҡ„й«ҳжҖ§иғҪжЁЎжӢҹ收еҸ‘еҷЁ (еҰӮ4DSPеҹәдәҺXilinx Virtex-7зҡ„FM788) дёә硬件пјҢfrmwareи®ҫи®Ўдәәе‘ҳејҖиҫҹдәҶеҸҜд»ҘеңЁе•Ҷдёҡе’ҢеӣҪйҳІеә”з”ЁдёӯдҪҝз”ЁжіўжқҹжҲҗеҪўж–№жі•зҡ„ж–°зҡ„жңәдјҡгҖӮ

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·