摘要:给出了一种基于多相滤波的数字信道化接收机的实现方法,系统的处理带宽为875 MHz,解决了高速ADC与FPGA处理速度之间的矛盾。为了克服信道化接收机的接收盲区,采用信道重叠的方法,连续覆盖瞬时带宽。在信道化处理后接测频模块,可以消除虚假信号的输出和提高测频精度。整个接收机在单片FPGA中实现,能够检测同时到达的两个信号,并实时输出脉冲描述字(PDW),经FPGA时序仿真结果验证了算法模型的正确性和有效性。

关键词:数字信道化接收机;多相滤波;参数估计;FPGA

0 引言

信道化接收机是在并行多通道接收机基础上提出的全概率频分信道化接收机,它克服了多部接收机并行工作、多通道下变频等方案具有的设备复杂,各通道性能不一致和可靠性差的缺点。数字信道化接收机具备大的瞬时带宽、较高的灵敏度、大的动态范围,能够检测和处理同时到达的信号、准确的参数测量能力和一定的信号识别能力。直接信道化接收机的运算量大且输出速率与采样速率相同,实现困难,后续处理的压力很大,高速ADC与慢速信号处理器(FPGA,DSP)是一个“瓶颈”;基于多相滤波的信道化接收机抽取在滤波之前,运算量小,且输出速率低,便于FPGA实现,这使得在一片FPGA中实现数字信道化成为可能。本文利用信道频率重叠的方法连续覆盖整个瞬时带宽,然后利用Rife算法测频,根据信道重叠的特点,消除虚假信号。系统带宽为875 MHz(62.5~937.5 MHz),可以处理两个同时到达的信号,并实时给出PDW。

1 宽带数字接收机的结构

1.1 数字信道化原理

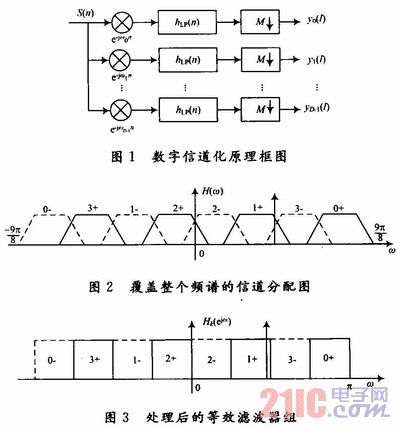

信道划分的基本思想是把信号按频率均匀地分成D个子频段(即信道),每个信道的中心频率为ωk,然后分别移到零中频,再通过低通滤波器滤出。由于子信道的带宽远小于系统瞬时带宽,因此可以采用抽取的方法来降低信号的输出速率,降低后续处理的压力。图1中,hLP(n)为低通滤波器;M↓表示对经过低通滤波器的信号M倍抽取。对于实信号而言,在侦察接收机中,各信道输出经过M=D倍抽取后,会产生频谱混叠,如图2所示。各个信道的中心频率为 ,覆盖整个频域范围。但是这种接收机存在信道的虚假输出。由图2中可以看出,当输入信号位于某一信道时,靠近这一信道的相邻信道会产生虚假输出。图2中实线表示实信道,虚线表示镜像信道。在信道化接收机的输出端接瞬时测频模块,可以消除虚假信号,同时还能提高频率精度。推导计算出混叠部分频率的点数,在固定的某一信道,将重叠部分的点只取一次,删除多余的点数,即消除虚假信号,得到如图3所示的等效滤波器组。

1.2 实信号无盲区信道化接收机数学模型

由图1可得第k路信号的输出为:

2 宽带数字接收机的FPGA硬件实现

2.1 系统模块实现

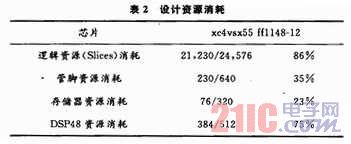

设计在Xilinx公司的XC4VSX55单片FPGA上实现,包括串并转换模块、多相滤波模块、信号检测模块、数据选择模块、瞬时测频模块以及PDW形成模块,如图8所示。

(1)串/并转换模块主要功能是降低数据速率,进行并行处理,原始采样速率为2 000 MSPS,分成D=16路并行数据,每路数据速率变为125 MSPS。

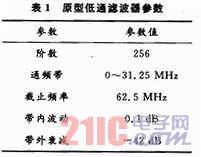

(2)多相滤波模块的功能是实现高效的多相滤波结构。它由两级乘法器、有限冲击响应滤波器(FIR)和16点并行FFT组成。其中,第一级乘法系数随着数据的先后次序,并按1,1,-1,-1的顺序变化来改变相应数据的符号。FIR滤波器采用全并行结构设计,原型低通滤波器的性能见表1。将原型滤波器分成16路,每相滤波器16阶。第二级乘法器为一复数乘法。16点全并行FFT,采用流水线结构,可以在一个时钟节拍内完成FFT运算的功能。

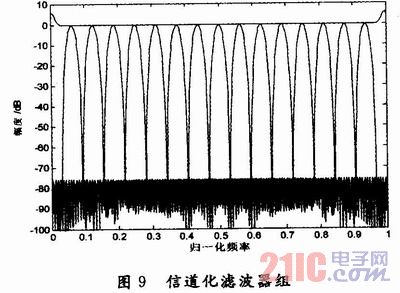

(3)信号检测模块的功能是对某一信道是否有信号进行判断。多相滤波出来的信号为复数,可以对其取模,利用幅度进行门限检测,同时可以测量到达时间和脉冲宽度。由于滤波器的暂态特性,脉冲信号通过滤波器组会产生“兔耳效应”,为了消除兔耳效应以及噪声的影响,在每个信道门限检测的后面加了一个最小脉宽检测电路,把兔耳效应和噪声引起的窄脉冲剔除掉,如图9所示。

(4)数据选择模块功能是将有信号信道的数据选出来,为后面的测频做准备。不必在每个信道后面都接一个测频模块以减少后面的测频模块,节约芯片资源。

(5)瞬时测频模块功能是运用Rife算法估计检测到信号的瞬时频率,并消除镜像信号的影响。根据门限检测的到达时间,选取N点数据做FFT,左右各删除N/4点,只取中间的N/2。对这N/2点做Rife插值,若最高谱线大于某固定值时,可以判断该信道存在真实信号,否则为虚假信号。

(6)脉冲描述字形成模块是将上述截获的脉冲信号的到达时间、脉冲宽度和瞬时频率的参数编码信息用PDW的形式输出。

2.2 仿真验证

经过在ISE中编译、综合、布局布线得到FPGA资源使用报告如表2所示;数字信道化接收机实现参数如表3所示。

3 结语

将理论算法和FPGA实现结合起来,分析了数字信道化的原理,提出了一种基于多相滤波的信道化接收机与Rife瞬时测频相结合的方法。这种方法实现了大带宽的全概率接收,可以消除虚假信号,同时提高测频精度。整个接收机在单片FPGA中实现,采用并行和流水线操作,可实现实时检测,生成脉冲描述字(PDW)。在信道化接收机的数字化、软件化和小型化发展方面具有重要的现实意义。

粤公网安备 44030902003195号

粤公网安备 44030902003195号