前言

为了提高现代无线设备的灵敏度和可选择性,需要尽可能地减小相位噪声和参考杂散,并缩短锁定时间。本文中所述电路可以改善本振(LO)的所有这些性能。

相位噪声是对LO信号的纯度的一种量度。相位噪声是载波功率相对于给定的频率偏移处(频率合成器通常定义1kHz 频率偏移)1-Hz的带宽上的功率。其计算结果以dBc/Hz为单位表示。

由于频率合成器内部的开关切换,输出信号中会出现杂散(spurs)。在整数N分频的合成器中,它们一般是由于鉴相器(PFD)的工作频率点上的信号分量所引起的;在小数N分频中,它们是由合成器本身架构的特点所造成的。在整数N分频锁相环(PLL)中,它们被称为参考杂散(reference spurs)。

锁定时间是指输出从一个频率切换到另一个频率所需要花费的时间——这对于许多系统来说是一个重要的指标。一般说来,当输出稳定到所期望的最终频率附近、差异在某一百分比[或者以百万分之一(ppm)衡量]之内,或是相位锁定在所需要相位度数的附近,此时我们说,输出被切换到或者锁定到新的频率上了。

传统的接收机实现方式

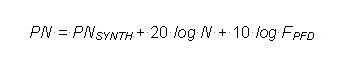

图1所示的是最通用的的接收机架构的功能框图(超外差接收机)。这里所示出的系统是满足DCS1800移动电话标准接收机的典型结构。在该标准中,接收(Rx)频段是1805MHz~1880MHz。

图1中,RF输入信号先流经一个RF滤波器,接下来再经过一个低噪声放大器(LNA)。随后,信号在混频器中与一个可调谐的LO输入进行混频,变换到中频段(IF)。混频后的信号接受进一步的滤波,在通过一个最终的混频器,与一个固定频率的LO信号混频,从固定的IF频段下变频到基带信号频段上。

可调谐的RF LO信号是利用一路干净和稳定的参考频率信号来生成的,该基准信号输入至ADF4106 PLL合成器和一个压控振荡器(VCO)中后最终形成LO信号。参考频率信号可以由温补晶振(TCXO)、压控晶体振荡器(VCXO)或者恒温晶体振荡器(OCXO)来产生。 在整数N分频系统中,PLL合成器的R分频器将该参考信号变换成为一个频率等于信道间隔的信号——或者,在小数N分频系统中,将信号频率变换成信道间隔的倍数。PFD则对环路输出FVCO除以N后的结果与R分频器的输出进行比较,然后,环路驱动VCO,使得FVCO = FPFD × N,以使PFD输出归零。可以通过改变N来改变LO输出频率,从而对无线电路进行调谐。

LO的相位噪声取决于多方面的因素:参考信号噪声、合成器中的噪声(R分频、N分频、PFD和电荷泵),N值,以及PFD的工作频率。

LO的相位噪声(dB)可以用如下的公式来表示:

式中

PNSYNTH是合成器对相位噪声的贡献(在数据手册中给出,单位是dB)

20 logN是合成器中的N值所带来的附加噪声

10 logFPFD是合成器的PFD频率所产生的噪声分量

*欲获得更多详情,请参阅“Design a Direct 6-GHz Local Oscillator with a New, Wideband, Integer-N, PLL Synthesizer”(Analog Dialogue, Volume 35, No. 6, November-December, 2001)

参考杂散取决于如下因素:PFD设计,PFD电路中电荷泵的漏电,PLL环路带宽,VCO灵敏度。锁定时间取决于PFD频率和PLL环路带宽。

在接收机中, 如果IF选定为230MHz,经过调谐的RF信号将在2035~2110MHz范围内变化(使用高端注入),步进为200kHz。如果使用整数N分频架构来实现的话,则需要使用200kHz的PFD频率,而N值将从10175(2035MHz)变化为10550(2110MHz)。

在商业应用系统中所期望的带内相位噪声为-85.6 dBc/Hz,采用适合的锁相环,如ADF4106,系统的典型基准寄生为-88dBc @ 200kHz和-90dBc @ 400kHz。

图1 传统的超外差接收机的系统框图

如果环路带宽选取为20kHz,则相位差小于10度时对应典型的锁定时间将为250µs。

接收机的另一种可替代方案

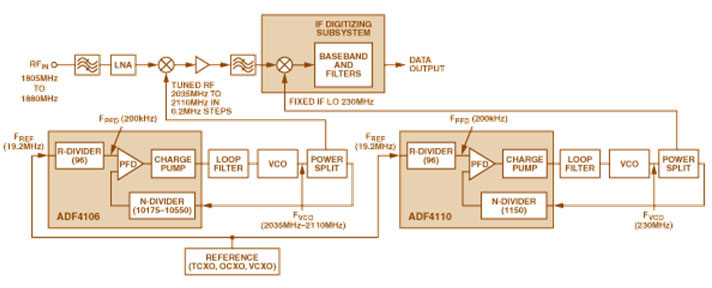

ADI公司目前提供一种新的宽带宽PLL合成器——ADF4107。其RF级可以在高达7.0GHz的频率下工作,而PFD频率可以高达104MHz。这样的宽带宽工作能力可以用于实现新颖的接收机架构,如图2所示。在该结构中,每一级的LO都可以从一路频率为所需频率的整数倍的信号变换得到。此外,调谐是在IF部分完成的。这就容许系统采用非常高的倍率,以便改善总的相噪声和锁定时间性能。

固定频率的RF电路

在图2中,一个频率固定的RF LO将信号向下变频到IF频段,而信道的调谐在IF中完成。仍以DCS1800为例,我们可以选择频率固定为1520MHz的RF LO。这可以从一路6080MHz的信号通过÷4分频来获得。

图2 替代性的接收机框图

RF LO 的相噪声为:

–219 + 20 log 950 + 10 log (6.4 × 106) – 20 log 4

= –219 + 59.5 + 68 – 12

= –103.5 dBc/Hz

参考杂散将出现在偏离载波6.4MHz的频率上,量值很小(<-90dBc),这是因为(a)4分频电路对应12dB的衰减,以及(b)——由于这是固定频率的LO——环路带宽可以变得很小(例如20kHz)。简单地施加一路20dB/十倍频程的衰减,将可以进一步衰减寄生分量。

在200kHz、400kHz、600kHz和800kHz处将不存在参考杂散,而锁定时间也不成问题,因为在频率固定的RF电路中无需进行任何调谐操作。

调谐作用的IF电路

我们继续讨论DCS1800实例,图2示出了一种可调谐的IF电路,其调节范围从285MHz到380MHz,步进为200kHz。为了实现此功能,PFD频率选用为3.2MHz ,相应产生的初始LO信号可以从4560变化到5760MHz,调谐的步进为3.2MHz。对这些频率进行16分频,就可以获得所需要的285MHz~360MHz、步进为200kHz的信号。

可调谐的IF电路在最差情形下的位相噪声为:

–219 + 20 log 1800 + 10 log (3.2 × 106) – 20 log 16

= –219 + 65 + 65 – 24

= –113 dBc/Hz

参考杂散将出现在偏离载波3.2MHz处。通过选择500kHz的环路带宽, 在3.2MHz的杂散将低于-90dBc。在一个DSC系统中,参考杂散件小的的重要频率点是200kHz、400kHz、600kHz和800kHz。不过在我们所提出的配置中,这些频率点上并不存在寄生分量,因为我们选用的PFD工作频率高达3.2MHz。

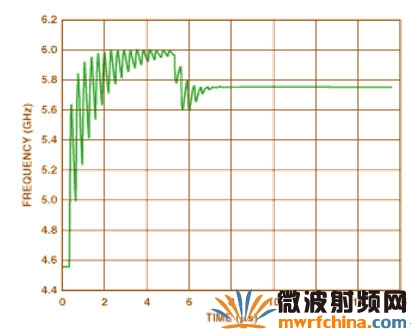

在环路带宽设定为500kHz, PFD频率为3.2MHz时,系统可以在10 µs以内完成锁相操作,且偏差在10°以内。图3所示的是频率锁定的响应特性。

图3 可调谐的IF电路锁定时间

滤波方面的考虑

上述的两种架构实质上都属于超外差,采用了两级下变频电路。在每一级电路中,滤波都有着关键性影响。

在图1中,位于LNA之前的RF滤波器可以抑制很强的带外干扰,IF滤波器可以选用窄带(在GSM体制中可以为200kHz)来抑制带内干扰。

在图2中,RF滤波器与图1中所示的相同。不过,图2中的IF滤波器不能采用窄带的。它必须能覆盖整个信号带宽,因为调谐是在其后才发生的。这意味着,带内干扰信号将在信号链后面的基带处理中滤除。ADI可以提供若干种IF到基带的接收机,包括AD6650、AD6652、AD9870和AD9874。在使用如图2所示的架构时,应该仔细考虑这些器件的选用。

结论

让PLL的内核以更高的PFD频率工作(最终的LO频率的整数倍)可以改善相位噪声、输出参考杂散和锁定时间性能。另外,可调谐的IF架构可以提供更高的性能,因为其倍频可以采用更高的整数倍。不过,需要精心考虑滤波方面的需求。

本文中所示的例子是针对整数N分频锁相环ADF4107的,但这种结构并不仅限于此,采用小数N分频体系结构,也能实现类似的性能改善。

作者:Mike Curtin,Paul O'Brien,ADI半导体

参考文献

Mini-Circuits Corporation, VCO Designer’s Handbook 1996.

Couch, L. W., Digital and Analog Communications Systems. New York: Macmillan Publishing Company, 1990.

Vizmuller, P., RF Design Guide, Artech House, 1995.

Best, R. L., Phase-Locked Loops: Design, Simulation and Applications, 3rd edition, McGraw Hill, 1997.

Bannerjee, Dean, “PLL Performance, Simulation and Design,” National Semiconductor Website.

Analog Devices, Inc. Data Sheet for ADF4107.

Hittite Microwave Corporation. Data Sheet for HMC362S8G

Curtin, Mike, “Phase-Locked Loops,” 3-part series in Analog Dialogue 33-3, 33-5, and 33-7 (1999). Also in hard copy: Analog Dialogue Volume 33, 1999.

Goldberg, Bar-Giora, Digital Frequency Synthesis Demystified, LLH, 1999.

粤公网安备 44030902003195号

粤公网安备 44030902003195号