1гҖҒеј•иЁҖ

иҝ‘е№ҙжқҘпјҢйҡҸзқҖж— зәҝйҖҡдҝЎжҠҖжңҜзҡ„иҝ…йҖҹеҸ‘еұ•пјҢеҜ№е…ЁйӣҶжҲҗгҖҒй«ҳжҖ§иғҪгҖҒдҪҺжҲҗжң¬зҡ„ж— зәҝ收еҸ‘жңәзҡ„йңҖжұӮеҸҳеҫ—и¶ҠжқҘи¶Ҡиҝ«еҲҮгҖӮиҖҢеҸ‘е°„жңәзі»з»ҹдёӯзҡ„дёҖдёӘе…ій”®жЁЎеқ—е°ұжҳҜеҠҹзҺҮж”ҫеӨ§еҷЁпјҢд»ҺеҠҹиҖ—ж–№йқўиҖғиҷ‘пјҢеҠҹзҺҮж”ҫеӨ§еҷЁзҡ„еҠҹзҺҮжҚҹиҖ—еңЁеҸ‘е°„жңәзҡ„жҖ»еҠҹиҖ—дёӯеҚ жңүеҫҲеӨ§жҜ”дҫӢгҖӮдәҺжҳҜдёҖдёӘй«ҳж•ҲзҺҮзҡ„CMOS еҠҹзҺҮж”ҫеӨ§еҷЁзҡ„и®ҫи®Ўе°ұжҳҫеҫ—е°ӨдёәйҮҚиҰҒгҖӮиҖҢйҡҸзқҖRF CMOSжҠҖжңҜзҡ„дёҚж–ӯеҸ‘еұ• пјҢдҪҝеҫ—еҹәдәҺSi CMOSе·Ҙиүәзҡ„е°„йў‘йӣҶжҲҗз”өи·ҜеңЁGHzйў‘ж®өдёҠзҡ„жҖ§иғҪдёҠжңүдәҶеҫҲеӨ§зҡ„жҸҗй«ҳпјҢиҖҢдё”е®ғе…·жңүй«ҳйӣҶжҲҗеәҰгҖҒдҪҺеҠҹиҖ—гҖҒдҪҺжҲҗжң¬зҡ„зү№зӮ№пјҢиғҪеӨҹе’ҢеҹәеёҰж•°еӯ—з”өи·Ҝзӣёе…је®№гҖӮжңҖз»ҲеҸҜд»Ҙе®һзҺ°зүҮдёҠзі»з»ҹйӣҶжҲҗ(SOC)гҖӮжүҖд»Ҙиҝ‘е№ҙжқҘеҜ№дәҺSiзҡ„CMOSе°„йў‘йӣҶжҲҗз”өи·Ҝзҡ„з ”з©¶жҲҗдёәеӣҪйҷ…дёҠз ”з©¶зҡ„зғӯзӮ№гҖӮ

еҠҹзҺҮж”ҫеӨ§еҷЁйҖҡеёёеҲҶдёәзәҝжҖ§е’ҢйқһзәҝжҖ§дёӨеӨ§зұ»пјҢзәҝжҖ§ж”ҫеӨ§еҷЁжңүеӣӣз§Қпјҡ AгҖҒB гҖҒABе’Ң CпјҢе®ғ们зҡ„дё»иҰҒе·®еҲ«еңЁдәҺж …жһҒеҒҸзҪ®жғ…еҶөдёҚеҗҢпјҢиҝҷзұ»дј з»ҹзҡ„еҠҹзҺҮж”ҫеӨ§еҷЁе…·жңүиҫғй«ҳзҡ„зәҝжҖ§еәҰпјҢдҪҶж•ҲзҺҮиҫғдҪҺ;йқһзәҝжҖ§ж”ҫеӨ§еҷЁдё»иҰҒжңүDгҖҒEе’ҢFгҖӮеҜ№дәҺжң¬ж–Үзҡ„ж— зәҝеұҖеҹҹзҪ‘иҖҢиЁҖпјҢз”ұдәҺиҰҒжұӮе…·еӨҮй«ҳзәҝжҖ§гҖӮжүҖд»ҘдёӨзә§еҲҶеҲ«йҮҮз”Ёзҡ„жҳҜAе’ҢABзұ»ж”ҫеӨ§жЁЎејҸгҖӮ

2гҖҒеҠҹзҺҮж”ҫеӨ§еҷЁзҡ„з”өи·Ҝи®ҫи®Ў

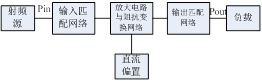

дёҖдёӘе…ёеһӢзҡ„еҠҹзҺҮж”ҫеӨ§еҷЁдёҖиҲ¬еҢ…жӢ¬иҫ“е…ҘеҢ№й…ҚзҪ‘з»ңгҖҒжҷ¶дҪ“з®Ўж”ҫеӨ§з”өи·ҜгҖҒзә§й—ҙеҢ№й…ҚзҪ‘з»ңгҖҒеҒҸзҪ®зҪ‘з»ңе’Ңиҫ“еҮәйҳ»жҠ—еҢ№й…ҚзҪ‘з»ңзӯү ,еҰӮдёӢеӣҫ1жүҖзӨәгҖӮ

гҖҖгҖҖеӣҫ1 еҠҹзҺҮж”ҫеӨ§еҷЁз»“жһ„жЎҶеӣҫ

2.1 иҮӘеҒҸзҪ®е…ұжәҗе…ұж …(Cascode)з»“жһ„

еҜ№дәҺеҠҹж”ҫиҖҢиЁҖпјҢж ҮеҮҶзҡ„0.18um CMOSе·Ҙиүәзҡ„жҷ¶дҪ“з®ЎжјҸж …й—ҙзҡ„жңҖеӨ§з”өжәҗз”өеҺӢдёә2VпјҢеҮ»з©ҝз”өеҺӢеӨ§зәҰжҳҜ4VгҖӮеңЁеҠҹж”ҫдёӯпјҢз®ЎеӯҗжјҸз«Ҝзҡ„зӣҙжөҒдёҺдәӨжөҒз”өеҺӢд№Ӣе’ҢеҸҜиҫҫеҲ°2-3еҖҚзҡ„з”өжәҗз”өеҺӢпјҢиҝҷе°ұз»ҷз®Ўеӯҗзҡ„ж …ж°§еҢ–еұӮеёҰжқҘеҮ»з©ҝзҡ„еҚұйҷ©гҖӮеңЁи®ҫи®ЎPAж—¶пјҢжҷ¶дҪ“з®ЎжүҖиғҪжүҝеҸ—зҡ„жңҖй«ҳз”өеҺӢVmaxеҸ—еҲ°жҷ¶дҪ“з®ЎеҮ»з©ҝз”өеҺӢзҡ„йҷҗеҲ¶пјҢиҖҢжңҖе°Ҹз”өеҺӢеҲҷеҸ—еҲ°Kneeз”өеҺӢзҡ„йҷҗеҲ¶гҖӮиҖҢеҠҹзҺҮж”ҫеӨ§еҷЁйҮҮз”ЁCascodeз»“жһ„еҸҜд»Ҙзј“и§Јжҷ¶дҪ“з®ЎеҮ»з©ҝзҡ„еҺӢеҠӣпјҢжҸҗй«ҳеҠҹзҺҮж”ҫеӨ§еҷЁиҫ“еҮәз”өеҺӢзҡ„ж‘Ҷе№…пјҢд»ҺиҖҢйҷҚдҪҺеҜ№жҷ¶дҪ“з®ЎжңҖеӨ§з”өжөҒиғҪеҠӣзҡ„иҰҒжұӮпјҢжҸҗй«ҳеҠҹзҺҮж”ҫеӨ§еҷЁзҡ„ж•ҲзҺҮпјҢ并еҮҸе°Ҹиҫ“еҮәжҷ¶дҪ“з®Ўзҡ„е°әеҜёгҖӮе®һйҷ…еңЁе…ұжәҗе…ұж …з»“жһ„зҡ„ж”ҫеӨ§еҷЁдёӯпјҢе…ұж …жҷ¶дҪ“з®ЎжҳҜз”өеҺӢеҮ»з©ҝе’ҢзғӯиҪҪжөҒеӯҗж•Ҳеә”зҡ„瓶йўҲгҖӮ

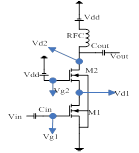

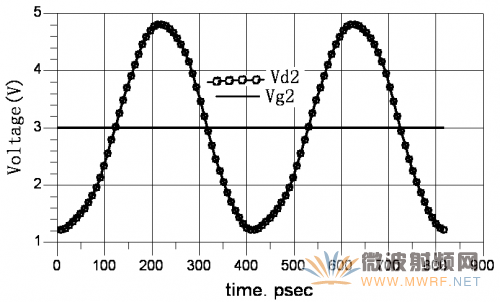

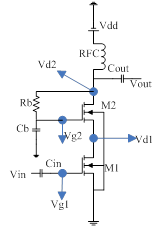

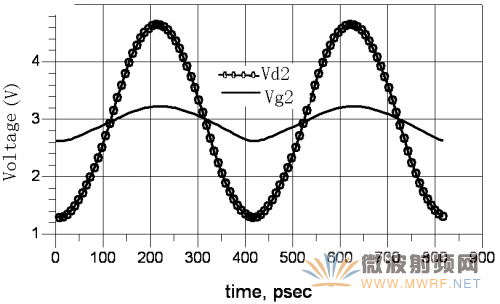

жүҖд»Ҙжң¬ж–ҮйҮҮз”ЁдәҶCascodeиҮӘеҒҸзҪ®з»“жһ„е’ҢеҺҡж …еҷЁд»¶пјҢдёҚд»…еҸҜд»Ҙж”№е–„ж·ұдәҡеҫ®зұіCMOSеҷЁд»¶зҡ„дҪҺеҮ»з©ҝз”өеҺӢпјҢеҗҢж—¶иҝҳеҸҜд»ҘеҮҸе°ҸзғӯиҪҪжөҒеӯҗж•Ҳеә”еҪұе“ҚгҖӮеӣҫ3жүҖзӨәзҡ„дј з»ҹCascodeж”ҫеӨ§еҷЁдёӯM2зҡ„ж …жјҸз”өеҺӢжіўеҪўпјҢVg2дёҖзӣҙеӣәе®ҡеңЁ3VпјҢVd2зҡ„жӯЈеі°еҖјз”өеҺӢеңЁ4.8VпјҢжүҖд»Ҙж …жјҸз”өеҺӢе·®дёә1.8VгҖӮдёәдәҶе…ӢжңҚиҝҷдёӘй—®йўҳпјҢеӣҫ4жүҖзӨәдёәиҮӘеҒҸзҪ®Cascodeз»“жһ„ж”ҫеӨ§з”өи·ҜпјҢиҜҘз»“жһ„жҠҠM2з®Ўзҡ„жјҸз«ҜдәӨжөҒз”өеҺӢVd2еј•е…ҘеҲ°ж …з«ҜVg2дёҠпјҢдҪҝжҲ‘们еңЁи®ҫи®ЎеҠҹж”ҫж—¶дёӨдёӘMOSз®Ўе°ҪеҸҜиғҪжңүзӣёеҗҢзҡ„жңҖеӨ§жјҸж …з”өеҺӢгҖӮжүҖд»ҘпјҢеңЁзғӯиҪҪжөҒеӯҗж•Ҳеә”еҮәзҺ°д№ӢеүҚM2з®ЎжңүдёҖдёӘеӨ§зҡ„дҝЎеҸ·ж‘Ҷе№…гҖӮеҜ№G2зҡ„еҒҸзҪ®жҳҜйҖҡиҝҮRb-CbжқҘе®һзҺ°зҡ„гҖӮеӣҫ6жүҖзӨәдёәM2з®Ўзҡ„Vd2еҜ№Vg2зҡ„з”өеҺӢжіўеҪўпјҢе…¶жңҖеӨ§з”өеҺӢе·®дёә1.4VгҖӮдёҺдј з»ҹз”өи·ҜжҜ”иҫғйҷҚдҪҺдәҶ0.4VпјҢжүҖд»ҘиҮӘеҒҸзҪ®зҡ„M2з®Ўзҡ„Vdgзҡ„з”өеҺӢе·®зӣёеҜ№дј з»ҹз»“жһ„зҡ„M2з®ЎйҷҚдҪҺдәҶ23%гҖӮ

гҖҖгҖҖеӣҫ2 дј з»ҹзҡ„Cascodeж”ҫеӨ§еҷЁ

гҖҖгҖҖеӣҫ3 дј з»ҹзҡ„Cascodeж”ҫеӨ§еҷЁдёӯM2зҡ„ж …жјҸз”өеҺӢжіўеҪў

гҖҖгҖҖеӣҫ4 иҮӘеҒҸзҪ®Cascodeж”ҫеӨ§еҷЁ

гҖҖгҖҖеӣҫ5 иҮӘеҒҸзҪ®Cascodeж”ҫеӨ§еҷЁзҡ„зӯүж•Ҳз”өи·Ҝеӣҫ

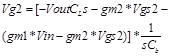

ж №жҚ®дёҠйқўзҡ„зӯүж•Ҳз”өи·ҜеӣҫпјҢжҲ‘们иғҪеӨҹеҫ—еҲ°дёӨдёӘ

зҡ„иЎЁиҫҫејҸпјҡ

(1)

(2)

еҗҢзҗҶпјҢжҲ‘们д№ҹеҸҜд»Ҙеҫ—еҲ°дёӨдёӘ

зҡ„иЎЁиҫҫејҸпјҡ

гҖҖгҖҖ(3)

(4)

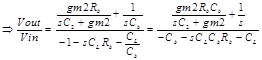

гҖҖгҖҖжҠҠ(2)ејҸд»Је…ҘејҸ(3)е’ҢејҸ(4)пјҢ并д»Өе®ғ们зӣёзӯүеҸҜеҫ—дёӢйқўзҡ„еўһзӣҠиЎЁиҫҫејҸпјҡ

(5)

(6)

(7)

(8)

д»Һ(8)ејҸзҡ„еўһзӣҠиЎЁиҫҫејҸеҸҜзҹҘпјҢеҰӮжһңRbжҲ–cbеўһеҠ пјҢж”ҫеӨ§еҷЁзҡ„еўһзӣҠйғҪдјҡжңүжүҖеўһеҠ пјҢдҪҶжҳҜйҖҡиҝҮз”өи·Ҝд»ҝзңҹеҗҺзҡ„з”өеҺӢжіўеҪўеҸҜзҹҘпјҢиӢҘRbжҲ–cbеўһеҠ пјҢеҜјиҮҙVg2зҡ„з”өеҺӢж‘Ҷе№…зҡ„йҷҚдҪҺпјҢд»ҺиҖҢжјҸз«ҜиҠӮзӮ№з”өеҺӢжіўеҪўе°ҶдјҡеңЁиҫ“е…ҘеҠҹзҺҮиҫғдҪҺзҡ„жғ…еҶөдёӢе°ұејҖе§ӢеӨұзңҹгҖӮжүҖд»ҘRbжҲ–cbзҡ„еҖјдёҚд»…иҰҒдҫқжҚ®M1е’ҢM2з®Ўе°ҪеҸҜиғҪжңүзӣёеҗҢзҡ„ж …жјҸдҝЎеҸ·ж‘Ҷе№…пјҢеҗҢж—¶д№ҹеҠӣжұӮеңЁеўһзӣҠе’ҢзәҝжҖ§д№Ӣй—ҙжңүдёӘиҫғеҘҪзҡ„жҠҳдёӯжқҘзЎ®е®ҡгҖӮ

гҖҖгҖҖеӣҫ6 иҮӘеҒҸзҪ®Cascodeж”ҫеӨ§еҷЁдёӯM2зҡ„ж …жјҸз”өеҺӢжіўеҪў

2.2гҖҒеҠҹзҺҮж”ҫеӨ§еҷЁзҡ„и®ҫи®ЎдёҺд»ҝзңҹ

еҜ№дәҺжң¬ж–Үзҡ„ж— зәҝеұҖеҹҹзҪ‘еә”з”ЁиҖҢиЁҖпјҢз”ұдәҺйҮҮз”Ёзҡ„жҳҜйқһжҒ’еҢ…з»ңи°ғеҲ¶пјҢиҰҒжұӮе…·еӨҮй«ҳзәҝжҖ§пјҢжүҖд»Ҙжң¬еҠҹзҺҮж”ҫеӨ§еҷЁз¬¬дёҖзә§е·ҘдҪңеңЁAзұ»пјҢ第дәҢзә§е·ҘдҪңеңЁABзұ»гҖӮAзұ»ж”ҫеӨ§жЁЎејҸиғҪжҸҗдҫӣжӣҙеҘҪзҡ„зәҝжҖ§еәҰпјҢиҖҢABзұ»ж”ҫеӨ§жЁЎејҸжҜ”Aзұ»ж”ҫеӨ§жЁЎејҸеҸҲе…·еӨҮжӣҙй«ҳзҡ„ж•ҲзҺҮгҖӮжүҖд»ҘпјҢжң¬ж–Үзҡ„еҠҹж”ҫеңЁзәҝжҖ§еәҰе’Ңж•ҲзҺҮд№Ӣй—ҙиҝӣиЎҢдәҶиҫғеҘҪзҡ„жҠҳдёӯгҖӮ

2.2.1гҖҒж”ҫеӨ§з”өи·Ҝи®ҫи®Ў

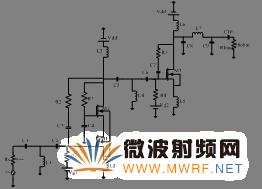

дёәдәҶиҫҫеҲ°еҠҹж”ҫзҡ„и®ҫи®ЎиҰҒжұӮпјҢз”ұдәҺй«ҳйў‘дёӢеҚ•зә§ж”ҫеӨ§еҷЁдёҚиғҪе®һзҺ°йў„е®ҡзҡ„еҠҹзҺҮеўһзӣҠжҢҮж Ү,жүҖд»ҘйҮҮз”ЁдёӨзә§ж”ҫеӨ§з»“жһ„гҖӮеҰӮеӣҫ7жүҖзӨәпјҢ第дёҖзә§йҮҮз”Ёе…ұжәҗе…ұж …з»“жһ„,еңЁжҸҗдҫӣеҗҲйҖӮзҡ„з”өеҺӢеўһзӣҠзҡ„еҗҢж—¶ ,жҸҗй«ҳдәҶеүҚеҗҺзә§з”өи·Ҝзҡ„йҡ”зҰ»еәҰпјҢдёәйҳ»жҠ—еҢ№й…ҚжҸҗдҫӣдәҶдҫҝеҲ©жқЎд»¶гҖӮ第дәҢзә§йҮҮз”Ёзҡ„жҳҜеҺҡж …зҡ„е…ұжәҗз»“жһ„д»ҘжүҝеҸ—жӣҙй«ҳзҡ„з”өжәҗз”өеҺӢгҖӮдё»дҪ“еҲҶдёәд»ҘдёӢеҮ дёӘйғЁеҲҶпјҡ(1) C1гҖҒC2гҖҒL1дёәиҫ“е…Ҙйҳ»жҠ—еҢ№й…ҚпјҢзүҮеҶ…е®һзҺ°пјҢдҪҝз”өи·Ҝзҡ„иҫ“е…Ҙз«ҜдёҺ50Ωз«ҜеҸЈеҢ№й…ҚгҖӮ

L3дёә第дёҖзә§ж”ҫеӨ§з”өи·Ҝзҡ„жүјжөҒз”өж„ҹпјҢиҖғиҷ‘еҲ°еҠҹж”ҫдёӯжөҒиҝҮзҡ„з”өжөҒеҫҲеӨ§пјҢзүҮеӨ–е®һзҺ°гҖӮ(2) M1дёҺM2дёәй©ұеҠЁзә§гҖӮ(3) C5гҖҒC6гҖҒL4дёәзә§й—ҙеҢ№й…ҚзҪ‘з»ңпјҢйҷӨдәҶдёӨзә§д№Ӣй—ҙеҢ№й…ҚеӨ–,иҝҳеҸҜд»Ҙз”ЁдәҺи°ғж•ҙж”ҫеӨ§з”өи·Ҝзҡ„еўһзӣҠе№іеқҰеәҰ[5]гҖӮ(4) M3дёәеҠҹзҺҮзә§гҖӮ(5) C8гҖҒC9гҖҒL7жһ„жҲҗ∏еһӢиҫ“еҮәеҢ№й…ҚзҪ‘з»ңпјҢиғҪеӨҹжңүж•ҲжҠ‘еҲ¶еҒ¶ж¬Ўи°җжіўеҲҶйҮҸпјҢе®һзҺ°жңҖдҪіиҙҹиҪҪеҢ№й…Қ[6]гҖӮдёәдәҶеҮҸе°‘жҚҹиҖ—пјҢиҫ“еҮәеҢ№й…ҚзҪ‘з»ңC8гҖҒC9гҖҒL7е’ҢжүјжөҒз”өж„ҹL6д№ҹйҮҮз”ЁзүҮеӨ–е®һзҺ°гҖӮ(6) CMOSзҡ„жҺҘең°з”өж„ҹеҜ№ж”ҫеӨ§еҷЁзҡ„еўһзӣҠе’Ңж•ҲзҺҮжңүеҫҲеӨ§еҪұе“ҚпјҢжүҖд»ҘеңЁз”өи·Ҝд»ҝзңҹж—¶жҠҠй”®еҗҲзәҝе’Ңpadзҡ„еҜ„з”ҹж•Ҳеә”дёҖиө·иҖғиҷ‘дәҶгҖӮе…¶дёӯL2е’ҢL5дёәеӨҡPADзҡ„й”®еҗҲзәҝз”өж„ҹгҖӮ

гҖҖгҖҖеӣҫ7 еҠҹзҺҮж”ҫеӨ§еҷЁз”өи·Ҝеӣҫ

2.2.2гҖҒд»ҝзңҹз»“жһң

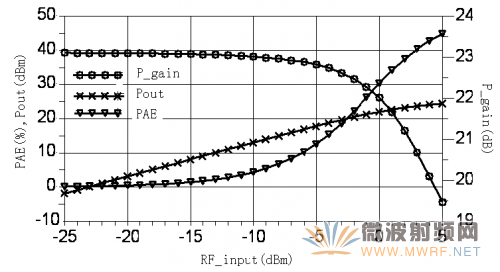

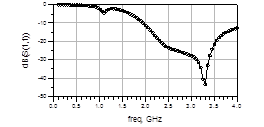

з”өи·Ҝзҡ„жҖ§иғҪд»ҝзңҹе’ҢдјҳеҢ–жҳҜеҲ©з”ЁAgilent е…¬еҸёзҡ„ADS(Advanced Design System)иҪҜ件е®ҢжҲҗзҡ„гҖӮж”ҫеӨ§еҷЁдёӯзҡ„жҷ¶дҪ“з®Ўе·ҘдҪңеңЁеӨ§дҝЎеҸ·зҠ¶жҖҒпјҢйқһзәҝжҖ§ж•Ҳеә”йқһеёёжҳҫи‘—пјҢеӣ жӯӨи®ҫи®Ўж”ҫеӨ§еҷЁз”өи·Ҝж—¶пјҢе°ҸдҝЎеҸ·з”өи·Ҝзҡ„зӯүж•ҲжЁЎеһӢдёҚеҶҚйҖӮз”ЁпјҢеҝ…йЎ»е……еҲҶиҖғиҷ‘жҷ¶дҪ“з®Ўзҡ„йқһзәҝжҖ§зү№жҖ§гҖӮеӣҫ8дёәд»ҝзңҹеҫ—еҲ°зҡ„иҫ“еҮәеҠҹзҺҮгҖҒеўһзӣҠе’ҢPAEйҡҸиҫ“е…ҘеҠҹзҺҮзҡ„еҸҳеҢ–жӣІзәҝгҖӮз”ұеӣҫеҸҜзҹҘпјҢеңЁиҫ“е…ҘеҠҹзҺҮе°ҸдәҺ0dBmзҡ„дҝЎеҸ·иҢғеӣҙеҶ…пјҢиҜҘеҠҹж”ҫзҡ„еўһзӣҠжңү22dBгҖӮеңЁ1dBеҠҹзҺҮеўһзӣҠеҺӢзј©зӮ№еӨ„иҫ“еҮәеҠҹзҺҮдёә22dBmпјҢзӣёеә”зҡ„PAEдёә30.4%гҖӮеӣҫ9дёәеҠҹж”ҫзҡ„S11еҸӮж•°йҡҸйў‘зҺҮзҡ„еҸҳеҢ–жӣІзәҝеӣҫпјҢз”ұеӣҫеҸҜзҹҘпјҢS11еңЁдёӯеҝғйў‘зҺҮ2.45GHzйҷ„иҝ‘йғҪе°ҸдәҺ-20dBжүҖд»Ҙиҫ“е…ҘеҢ№й…Қеҹәжң¬иҫҫеҲ°и®ҫи®ЎиҰҒжұӮгҖӮ

гҖҖгҖҖеӣҫ8 иҫ“еҮәеҠҹзҺҮгҖҒеўһзӣҠе’ҢPAEйҡҸиҫ“е…ҘеҠҹзҺҮзҡ„еҸҳеҢ–жӣІзәҝ

гҖҖгҖҖеҸҰеӨ–пјҢд»ҝзңҹжүҖеҫ—еҲ°зҡ„е…¶е®ғйҮҚиҰҒеҸӮж•°жңүпјҡиҫ“еҮәдёүйҳ¶дәӨжҺҘзӮ№зәҰдёә29 dBm;зЁіе®ҡеӣ еӯҗKеңЁе·ҘдҪңйў‘ж®өеҶ…жңүK>1гҖӮ

гҖҖгҖҖеӣҫ9 еҠҹж”ҫзҡ„S11еҸӮж•°жӣІзәҝ

2.2.3гҖҒзүҲеӣҫи®ҫи®Ў

зүҲеӣҫи®ҫи®ЎйҮҮз”ЁдәҶ CadenceиҪҜ件гҖӮеҠҹзҺҮж”ҫеӨ§еҷЁйҮҮз”Ё SMIC 0.18μm CMOSе·ҘиүәгҖӮе…¶дёӯж”ҫеӨ§з”өи·ҜдёӯдҪҝз”Ёзҡ„жҷ¶дҪ“з®ЎйҮҮз”Ёе°„йў‘жЁЎеһӢгҖӮжң¬зүҲеӣҫи®ҫи®Ўдё»иҰҒиҖғиҷ‘дәҶд»ҘдёӢеҮ дёӘж–№йқўзҡ„й—®йўҳпјҡ

(1)з”ұдәҺеҠҹж”ҫдёӯжөҒиҝҮзҡ„з”өжөҒеҫҲеӨ§пјҢжүҖд»ҘеңЁз”өжәҗзәҝе’Ңең°зәҝйҮҮз”ЁеҮ еұӮйҮ‘еұһ并иҒ”зҡ„ж–№ејҸжқҘйҒҝе…ҚеҸ‘з”ҹз”өиҝҒ移гҖӮ(2)жҺҘең°й”®еҗҲзәҝзҡ„еҜ„з”ҹз”өж„ҹдёҘйҮҚеҪұе“Қеҗ„зә§з”өи·Ҝзҡ„еҠҹзҺҮиҫ“еҮәгҖӮжүҖд»ҘпјҢдёәдәҶдҪҝжҺҘең°й”®еҗҲзәҝеҜ„з”ҹз”өж„ҹе°ҪйҮҸе°ҸпјҢи®ҫзҪ®еӨҡдёӘеҜ№ең°з„Ҡзӣҳ并引еҮәеӨҡжқЎй”®еҗҲзәҝеҲ°ең°зәҝдёҠгҖӮ(3)еҜ№дәҺй«ҳйў‘дҝЎеҸ·зәҝ ,е°ҪйҮҸйҮҮз”ЁйЎ¶еұӮе’ҢдёҠеұӮйҮ‘еұһ ,дё”жңҖеҘҪйҒөеҫӘжңҖзҹӯдҝЎеҸ·зәҝзҡ„еҺҹеҲҷз”ЁдәҺеҮҸе°‘еҜ„з”ҹз”өе®№гҖҒиҖҰеҗҲзӯүеӣ зҙ еј•иө·зҡ„жҚҹиҖ—гҖӮ

гҖҖгҖҖеӣҫ10 PAзүҲеӣҫ

3гҖҒз»“и®ә

йҮҮз”ЁSMIC 0.18um CMOS е·ҘиүәRFжЁЎеһӢи®ҫи®ЎдәҶе·ҘдҪңдәҺ2.45GHz WLANзҡ„еҠҹзҺҮж”ҫеӨ§еҷЁгҖӮйҖҡиҝҮиҮӘеҒҸзҪ®жҠҖжңҜзҡ„еә”з”ЁпјҢиҜҘеҠҹж”ҫе·ҘдҪңеңЁ3Vз”өжәҗз”өеҺӢдёӢпјҢе…¶д»ҝзңҹжҖ§иғҪжҢҮж ҮиЎЁжҳҺжңҖеӨ§иҫ“еҮәеҠҹзҺҮеҸҜиҫҫ24.5dBmпјҢеҜ№еә”зҡ„PAEиҫҫеҲ°40%пјҢеҠҹзҺҮеўһзӣҠдёә23dBпјҢйҖӮеҗҲж— зәҝеұҖеҹҹзҪ‘802.11bзҡ„зі»з»ҹеә”з”ЁгҖӮ

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·