з”ЁдәҺз”ҡй«ҳйў‘зҺҮзҡ„еҚҠеҜјдҪ“жҠҖжңҜ

жҜ«зұіжіўй•ҝиҢғеӣҙпјҲ30-300GHzпјүеҶ…йҷӨдәҶе…¶иҫғдҪҺз«ҜеӨ–пјҢиҝҳжІЎжңүеҫҲеҘҪең°иў«еҲ©з”ЁгҖӮиҖҢеңЁжҲҗеғҸпјҢе®үе…ЁпјҢеҢ»з–—пјҢе’Ңзҹӯи·қзҰ»ж— зәҝдј иҫ“д»ҘеҸҠж•°жҚ®йҖҹзҺҮдёҚж–ӯжҸҗй«ҳзҡ„е…үзәӨдј иҫ“дёӯзҡ„ж–°еә”з”ЁеҸҜиғҪдјҡиҝ…йҖҹең°ж”№еҸҳиҝҷз§ҚзҠ¶жҖҒ[1]пјҢ[2]гҖӮеңЁиҝҮеҺ»зҡ„дёүеҚҒе№ҙйҮҢпјҢIII-V жҠҖжңҜпјҲGaAs е’ҢInPпјүе·Із»ҸйҖҗжёҗжү©еӨ§еҲ°иҝҷдёӘжҜ«зұіжіўиҢғеӣҙдёӯгҖӮж–°иҝ‘д»ҘжқҘпјҢз”ұдәҺе·Ҙиүәе°әеҜёжҢҒз»ӯдёҚж–ӯең°еҮҸе°ҸпјҢзЎ…жҠҖжңҜе·Із»ҸеҠ е…ҘдәҶиҝҷдёӘ“жёёжҲҸ”гҖӮ

еңЁжң¬ж–ҮдёӯпјҢжҢүз…§еҚҠеҜјдҪ“зү№жҖ§е’ҢеҷЁд»¶иҰҒжұӮпјҢеҜ№еҸҜз”ЁдәҺ100-GHz е’Ң100-Gb/s еә”з”Ёзҡ„еҚҠеҜјдҪ“жңүжәҗеҷЁд»¶иҝӣиЎҢдәҶз»јиҝ°гҖӮйҡҸеҗҺд»Ӣз»ҚдәҶдҪҝз”ЁжңҖе№ҝжіӣзҡ„жҠҖжңҜпјҢжҺҘзқҖжҳҜдёӨдёӘдёҚеҗҢж–№йқўе…·жңүз«һдәүжҖ§зҡ„жҠҖжңҜзҺ°зҠ¶пјҡеҲҶйў‘еҷЁпјҢжқҘиҜҙжҳҺиҜҘжҠҖжңҜйҖӮе®ңз”ЁеңЁй«ҳйҖҹж•°еӯ—з”өи·ҜдёӯпјҢд»ҘеҸҠжҢҜиҚЎеҷЁпјҢз”ЁжқҘиҜҙжҳҺе…¶еңЁжЁЎжӢҹз”өи·Ҝеә”з”Ёдёӯзҡ„жҖ§иғҪгҖӮ

жқҗж–ҷе’Ңе·Ҙиүәзҡ„еҹәжң¬зү№жҖ§

еҚҠеҜјдҪ“жқҗж–ҷзҡ„зү№жҖ§

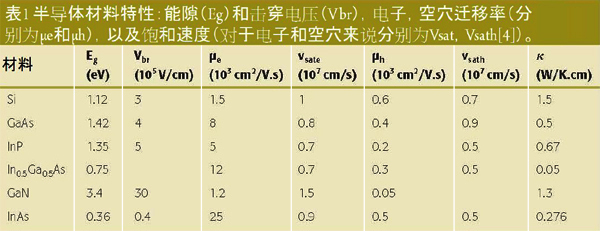

иҝҗиЎҢеңЁеҫҲй«ҳйў‘зҺҮдёӢзҡ„з”өеӯҗеҷЁд»¶жүҖиЎЁзҺ°зҡ„жҖ§иғҪдё»иҰҒдёҺпјҡ1)з»„жҲҗеҚҠеҜјдҪ“зҡ„жқҗж–ҷзү№жҖ§е’Ң2)еҷЁд»¶зҡ„з»“жһ„жңүе…і[3]гҖӮSiпјҢGaAs е’ҢInP жҳҜзӣ®еүҚе…·жңүжҲӘжӯўйў‘зҺҮеңЁ300GHz еҸҠд»ҘдёҠзҡ„еҷЁд»¶жүҖйҖүжӢ©зҡ„жқҗж–ҷгҖӮеңЁиЎЁ1пјҢдәә们з»ҷеҮәдәҶдёҖдәӣзӣёе…ізҡ„иЎЁеҫҒиғҪйҡҷпјҢиҪҪжөҒеӯҗиҫ“иҝҗзү№жҖ§е’ҢеҜјзғӯжҖ§зҡ„еҸӮж•°гҖӮеҗҢж ·д№ҹжҠҘйҒ“дәҶдёҺInPпјҢGaN е’ҢInAs жҷ¶ж јзӣёеҢ№й…Қзҡ„InGaAs зҡ„зү№жҖ§гҖӮ

жӢҘжңүдёҖдёӘи¶іеӨҹеӨ§иғҪйҡҷпјҲEg>1eV пјүжҳҜеҫҲжңүеҲ©зҡ„пјҢиҝҷжҳҜеӣ дёәе®ғеҸҜд»ҘжҸҗдҫӣеҘҪзҡ„еҮ»з©ҝзү№жҖ§гҖӮSiпјҢGaAs е’ҢInP еңЁ100nm е®һйҷ…дёҠеҸҜд»ҘжүҝеҸ—еҮ дјҸзҡ„з”өеҺӢж°ҙе№іпјӣжӯӨеӨ–пјҢp-n з»“жҳҫзӨәеҮәеҫҲжҳҺжҷ°зҡ„ж•ҙжөҒиЎҢдёәпјҢе®Өжё©дёӢзҡ„жі„жјҸз”өжөҒеҸҜд»ҘеҝҪз•ҘдёҚи®ЎгҖӮйҮҮз”ЁGaN еҸҜд»ҘиҺ·еҫ—жӣҙй«ҳзҡ„еҮ»з©ҝз”өеҺӢпјҢInAs еӣ дёәе…¶иғҪйҡҷеҫҲдҪҺиҖҢеҸӘиғҪз”ЁдәҺз”өеҺӢеҫҲдҪҺзҡ„еҷЁд»¶гҖӮ

III-V жқҗж–ҷдёӯзҡ„з”өеӯҗиҝҒ移зҺҮжҜ”зЎ…зҡ„иҰҒеӨ§пјҢиҝҷж„Ҹе‘ізқҖеңЁз»ҷе®ҡзҡ„жҺәжқӮжө“еәҰдёӢпјҢn-еһӢжҺҘи§ҰеҢәе…·жңүиҫғдҪҺзҡ„дёІиҒ”з”өйҳ»пјҢиҖҢеҜ№дәҺp-еһӢ еҢәжқҘиҜҙпјҢз”ұдәҺIII-V жқҗж–ҷиҫғдҪҺзҡ„з©әз©ҙиҝҒ移зҺҮпјҢжғ…еҶөеҲҷжҒ°жҒ°зӣёеҸҚгҖӮ然иҖҢпјҢеңЁеҷЁд»¶зҡ„й«ҳеңәејәеҢәжҺ§еҲ¶и·ЁеҜје’ҢжёЎи¶Ҡж—¶й—ҙзҡ„иҪҪжөҒеӯҗйҖҹеәҰдёҺеҸ–еҶідәҺиҪҪжөҒеӯҗзұ»еһӢзҡ„йҘұе’ҢжјӮ移йҖҹеәҰзӣёжҺҘиҝ‘пјҲVsat жҲ–Vsath′еҸ–еҶідәҺиҪҪжөҒеӯҗзҡ„зұ»еһӢпјӣжҺҘиҝ‘дәҺ10nm/psпјүгҖӮз”ұдәҺжҡӮжҖҒж•Ҳеә”пјҲз”өеӯҗд»ҺеҜјеёҰдёӯзҡ„дҪҺиғҪзә§пјҢй«ҳиҝҒ移зҺҮиғҪи°·еҲ°иҫҫиҫғй«ҳиғҪзә§пјҢиҫғдҪҺиҝҒ移зҺҮиғҪи°·зҡ„иҪ¬жҚўдёҚжҳҜзһ¬й—ҙеҸ‘з”ҹзҡ„пјүпјҢз”өеӯҗзҡ„дј иҫ“йҖҡеёёдјҡеҸ—зӣҠдәҺдёҖдәӣиҝҮеҶІйҮҸпјӣдҫӢеҰӮпјҢж №жҚ®е…·жңүи–„йӣҶз”өжһҒзҡ„InPејӮиҙЁз»“еҸҢжһҒжҖ§жҷ¶дҪ“з®ЎпјҲHBTпјүзҡ„еҹәжһҒеҲ°йӣҶз”өжһҒзҡ„жёЎи¶Ҡж—¶й—ҙжүҖжҺЁеҜјеҮәзҡ„жңүж•ҲйҖҹеәҰеӨ§дәҺ3×107cm/sпјҢеӨ§зәҰжҳҜйҘұе’ҢйҖҹеәҰзҡ„5 еҖҚ[5]гҖӮ

з”ҡй«ҳйў‘зҺҮжҖ§иғҪж„Ҹе‘ізқҖиҫғзҹӯзҡ„жёЎи¶Ҡж—¶й—ҙе’ҢиҫғдҪҺзҡ„RCеҜ„з”ҹйҮҸпјӣеҜ№дәҺеңәж•Ҳеә”з®ЎпјҲFETпјүе’ҢеҸҢжһҒжҖ§жҷ¶дҪ“з®ЎжқҘиҜҙпјҢиҝҷйҖҡеёёеҸҜд»ҘйҖҡиҝҮеҮҸе°Ҹз”өеӯҗеҷЁд»¶зҡ„е°әеҜёе’ҢжҸҗй«ҳз”өжөҒеҜҶеәҰжқҘе®һзҺ°пјҲдҫӢеҰӮпјҢи§Ғ[6]пјүгҖӮеҜ№дәҺжһҒй«ҳйў‘еҷЁд»¶е’Ңз”өи·ҜжқҘиҜҙпјҢзғӯеҜјзҺҮеҲҷжҲҗдёәдёҖдёӘйҮҚиҰҒзҡ„еҸӮж•°пјҢзЎ…еңЁдёҺе…¶III-V жҠҖжңҜзҡ„еҜ№жүӢзӣёжҜ”ж—¶пјҢе…¶жүҖе…·жңүзҡ„иүҜеҘҪзҡ„еҜјзғӯжҖ§дҫҝжҲҗдёәдёҖдёӘзңҹжӯЈзҡ„дјҳеҠҝпјҢеӣ дёәиҝҷжңүеҸҜиғҪиҫҫеҲ°жӣҙй«ҳзҡ„еҷЁд»¶еҜҶеәҰгҖӮ

еҹәдәҺIII-V жҠҖжңҜзҡ„ж—©жңҹеҚ•зүҮеҫ®жіўйӣҶжҲҗз”өи·ҜпјҲMMICпјүзҡ„дё»иҰҒдјҳзӮ№д№ӢдёҖиҰҒеҪ’еӣ дәҺжңӘжҺәжқӮпјҲжҲ–иЎҘеҒҝпјүеҹәзүҮзҡ„еҚҠз»қзјҳзү№жҖ§пјҢиҝҷжҳҜдёҺе…¶еӨ§зҡ„еҚҠеҜјдҪ“иғҪйҡҷзӣҙжҺҘзӣёе…ізҡ„пјҲеҹәзүҮзҡ„з”өйҳ»зҺҮдёә108Ω.cm зҡ„ж•°йҮҸзә§пјҢиҖҢзЎ…зҡ„з”өйҳ»зҺҮдёә104Ω.cmпјүгҖӮиҝҷдҪҝеҫ—еҸҜд»Ҙе®һзҺ°е…·жңүдҪҺе…іиҒ”еҜ„з”ҹж•Ҳеә”зҡ„з”өйҳ»пјҢз”өж„ҹе’Ңдј иҫ“зәҝгҖӮйҡҸзқҖиҝ‘жқҘе·ЁеӨ§зҡ„еҫ®жіўеә”з”ЁеёӮеңәзҡ„ејҖеҸ‘пјҲдҫӢеҰӮпјҢ移еҠЁз”өиҜқзҪ‘з»ңпјүпјҢеңЁзЎ…еҹәжҠҖжңҜдёҠеј•е…Ҙж— жәҗеҷЁд»¶иҝҷж–№йқўе·Із»ҸеҸ–еҫ—дәҶеҫҲеӨ§зҡ„иҝӣеұ•гҖӮжӯӨеӨ–пјҢз»қзјҳдҪ“еҠ иҪҪзЎ…еҹәзүҮжҠҖжңҜпјҲSOIпјүе·Із»Ҹеұ•зӨәеҮәе…¶йҷҚдҪҺеҜ„з”ҹж•Ҳеә”зҡ„жҪңеҠӣпјҲ然иҖҢпјҢиҝҷжҳҜд»ҘиҫғдҪҺзҡ„еҹәзүҮеҜјзғӯзҺҮдёәд»Јд»·зҡ„пјүгҖӮ

жңҚеҠЎдәҺй«ҳйў‘еә”з”Ёзҡ„FET е’ҢеҸҢжһҒжҖ§жҷ¶дҪ“з®Ў

д»ҠеӨ©пјҢйҖӮз”ЁдәҺй«ҳйў‘еә”з”Ёзҡ„еҸҢжһҒжҖ§жҷ¶дҪ“з®Ўе’ҢFET жҳҜеҹәдәҺејӮиҙЁз»“з»“жһ„зҡ„пјҲйҷӨдәҶжҳҜзЎ…еҹәMOSFET д»ҘеӨ–пјүгҖӮеҜ№ејӮиҙЁз»“зҡ„ејҖеҸ‘е·Із»Ҹжңү40 еӨҡе№ҙдәҶпјҢ并且еңЁжқҗж–ҷе’Ңжҷ¶ж јеә”еҠӣж–№йқўиҝҳеңЁдёҚж–ӯең°еҸ‘еұ•зқҖгҖӮдёӨз§ҚдёҚеҗҢжқҗж–ҷпјҲе…·жңүеҗҢж ·зҡ„жҷ¶дҪ“з»“жһ„е’ҢеҗҢж ·зҡ„жҷ¶ж јеҸӮж•°пјүд№Ӣй—ҙзҡ„ејӮиҙЁз»“дё»иҰҒжҳҜз”ұе®ғ们зҡ„иғҪйҡҷе·®ејӮпјҢд»ҘеҸҠз”ұиҝҷз§Қе·®ејӮжүҖеҢәеҲҶзҡ„еҜјеёҰе’Ңд»·еёҰзҡ„йҳ¶и·ғж–№ејҸжқҘиЎЁеҫҒзҡ„пјҲиЎЁ2пјүгҖӮеңЁжҷ¶дҪ“з®Ўзҡ„жңүжәҗеҢәпјҢејӮиҙЁз»“иў«з”ЁжқҘиҫҫеҲ°дёӨдёӘдёҚеҗҢзҡ„зӣ®зҡ„пјҡ

• еңЁй«ҳз”өеӯҗиҝҒ移зҺҮжҷ¶дҪ“з®ЎпјҲHEMTпјүдёӯе°Ҷз”өеӯҗеұҖйҷҗеңЁжңӘжҺәжқӮзҡ„йҮҸеӯҗиӮјдёӯгҖӮ

иҷҪ然жңҖеҲқжҳҜй’ҲеҜ№жҷ¶ж јеҢ№й…ҚејӮиҙЁз»“жқҘе®һж–Ҫзҡ„пјҢдҪҶеҫҲеҝ«е°ұжҳҫзӨәеҮәз”ЁеңЁеӨұй…ҚејӮиҙЁз»“дёӯд№ҹеҸҜд»ҘеўһејәжҖ§иғҪпјҢжқЎд»¶жҳҜеә”еҠӣз»“жҷ¶еұӮжҳҜеңЁеҒҮжҷ¶еҺҡеәҰзҡ„жһҒйҷҗеҶ…пјҲеҰӮжһңз”ҹй•ҝеұӮи¶іеӨҹи–„пјҢе…¶жҷ¶ж јеёёж•°дјҡи°ғж•ҙеҲ°еҹәзүҮзҡ„жҷ¶ж јеёёж•°пјүгҖӮиҝҷз§Қзү№жҖ§иў«з”ЁеңЁHBT дёӯпјҲдҫӢеҰӮжёҗеҸҳз»„еҲҶзҡ„ж–№жі•пјҢgraded-compositionпјүжқҘз”ҹжҲҗе…·жңүзҹӯзҡ„жёЎи¶Ҡж—¶й—ҙзҡ„еҹәжһҒеұӮпјҢд»ҘеҸҠй«ҳиҝҒ移зҺҮHEMT зҡ„жІҹйҒ“еұӮгҖӮеңЁдёҙз•ҢеҺҡеәҰд»ҘдёҠпјҢпјҲеӨұй…ҚзЁӢеәҰи¶Ҡй«ҳпјҢеұӮеҺҡе°ұи¶Ҡи–„пјүпјҢз”ҹй•ҝеұӮжқҫејӣдёӢжқҘпјҢеңЁжҷ¶дҪ“з»“жһ„дёӯдҫҝдјҡеҮәзҺ°жҷ¶ж ји„ұдҪҚгҖӮиҝҷз§ҚзҺ°иұЎд»Қ然еҸҜд»Ҙиў«з”ЁжқҘеңЁеҹәзүҮзҡ„йЎ¶йғЁз”ҹжҲҗе…·жңүдёҚеҗҢжҷ¶ж јеҸӮж•°зҡ„й«ҳиҙЁйҮҸжҷ¶дҪ“еұӮпјҢеңЁдёӯй—ҙжңүдёҖдёӘиҝҮжёЎеұӮпјҲзј“еҶІеұӮпјүжқҘдҝҳиҺ·еӨ§еӨҡж•°зҡ„и„ұдҪҚгҖӮдҫӢеҰӮпјҢиҝҷз§Қз»“жһ„еҸҜд»ҘеңЁиў«з§°дёәж”№жҖ§пјҲmetamorphicпјүHEMT дёӯжүҫеҲ°пјҢеңЁжқҫејӣзј“еҶІеұӮд№ӢдёҠеҸҲз”ҹй•ҝдәҶдёҖеұӮй«ҳиҙЁйҮҸзҡ„жҙ»жҖ§ејӮиҙЁз»“жһ„гҖӮзү№еҲ«жҳҜпјҢеҸҳжҖ§з»“жһ„е…Ғи®ёйҮҮз”ЁжһҒй«ҳиҝҒ移зҺҮзҡ„InAs жІҹйҒ“[7]пјҢ[8]гҖӮ

зӣ®еүҚпјҢеҸҜд»Ҙйў„и§ҒеҮ з§ҚжңҚеҠЎдәҺ100-GHz е’Ң100-Gb/sеә”з”Ёзҡ„жҠҖжңҜпјҡGaAs е’ҢInP HEMTпјӣInP е’ҢSiGe HBTпјҢиҝҷдәӣжҠҖжңҜеңЁиҝҮеҺ»зҡ„еҚҒе№ҙдёӯе·Із»ҸеңЁдҪҝз”Ёд№ӢдёӯдәҶпјӣд»ҘеҸҠзЎ…CMOS жҠҖжңҜпјҢд»ҺжңҖиҝ‘зҡ„дёҖдәӣжғ…еҶөжқҘзңӢпјҢе®ғдјјд№ҺиҰҒеҸ‘жҢҘдҪңз”ЁдәҶгҖӮеҫҲжңүеүҚжҷҜзҡ„жҠҖжңҜеҰӮGaN HEMT д»ҘеҸҠйӮЈдәӣйҮҮз”Ёе°ҸиғҪйҡҷжқҗж–ҷзҡ„жҠҖжңҜеҗҢж ·еҸҜд»Ҙиҝӣе…ҘиҝҷдёӘ“жёёжҲҸ”гҖӮеҲ°зӣ®еүҚдёәжӯўпјҢз”ұдәҺGaN HEMT йқһеҮЎзҡ„еҫ®жіўе’ҢжҜ«зұіжіўеҠҹзҺҮе®№йҮҸпјҢдәә们已еҜ№е…¶иҝӣиЎҢдәҶејҖеҸ‘[9]гҖӮжӯӨеӨ–пјҢдёҺжҷ¶дҪ“з»“жһ„зӣёе…ізҡ„еҺӢз”өж•Ҳеә”жүҖеёҰжқҘзҡ„й«ҳз•Ңйқўз”өеӯҗеҜҶеәҰпјҲеӨ§зәҰ1013cm-2пјүеҸҜд»Ҙз”ЁжқҘиЎҘеҒҝзӣёеҜ№иҫғдҪҺзҡ„иҪҪжөҒеӯҗиҝҒ移зҺҮпјҢеҰӮжһңзү№е®ҡзҡ„з»“жһ„и®ҫи®ЎеҸҜд»Ҙдә§з”ҹдҪҺжҺҘи§Ұз”өйҳ»зҡ„иҜқпјҢйӮЈд№ҲдҪҝе…¶е…·жңүз”ҡй«ҳйў‘зҺҮжҖ§иғҪдјјд№Һд№ҹжҳҜеҸҜиЎҢзҡ„[10]гҖӮ

HBT дёҺFET зҡ„е·®еҲ«

йҷӨдәҶFET жҳҜеҚ•жһҒжҖ§еҷЁд»¶д»ҘеӨ–пјҲеҸӘжңүдёҖз§Қзұ»еһӢзҡ„иҪҪжөҒеӯҗеҸӮдёҺжҷ¶дҪ“з®Ўзҡ„иҝҗиЎҢпјҢиҖҢдёҖдёӘеҸҢжһҒжҖ§еҷЁд»¶еҲҷж„Ҹе‘ізқҖдёӨз§Қзұ»еһӢзҡ„иҪҪжөҒеӯҗйғҪеҸӮдёҺиҝҗиЎҢпјүпјҢеңЁеҸҢжһҒжҖ§е’ҢFET жҠҖжңҜд№Ӣй—ҙиҝҳеҸҜд»Ҙи§ӮеҜҹеҲ°еҮ з§Қе·®еҲ«пјҢзү№еҲ«жҳҜпјҡ

• HBT еҷЁд»¶е…·жңүжҢҮж•°жҖ§зҡ„й©ұеҠЁзү№жҖ§[е°ұжҳҜиҜҙпјҢйӣҶз”өжһҒз”өжөҒдёҺиҫ“е…Ҙз”өеҺӢд№Ӣй—ҙзҡ„дҫқиө–е…ізі»жҳҜжҢҮж•°жҖ§зҡ„пјҡicαexp(Vbe/kT)]пјҢиҖҢFET еҷЁд»¶зҡ„еҲҷжҳҜе№іж–№зҡ„е…ізі»[жјҸжһҒз”өжөҒйҡҸзқҖз”өеҺӢзҡ„е№іж–№иҖҢеҸҳеҢ–зҡ„пјҡidsαk(Vgs2)]гҖӮеҜ№дәҺHEMT жқҘиҜҙпјҢиҝҷз§Қе…ізі»иҪ¬еҢ–дёәе…·жңүиҫғеӨ§еҲҶж•ЈжҖ§зҡ„й—Ёйҷҗз”өеҺӢгҖӮиҝҷдҫҝжҳҜдёәд»Җд№Ҳй«ҳйҖҹж•°еӯ—жҲ–ж··еҗҲдҝЎеҸ·йӣҶжҲҗз”өи·ҜпјҲICпјүйҖҡеёёйҮҮз”ЁHBT жҠҖжңҜиҝӣиЎҢи®ҫи®Ўзҡ„еҺҹеӣ пјҲдҪҶиҜ·и®°дҪҸCMOS еңЁж•°еӯ—йӣҶжҲҗз”өи·ҜиҠҜзүҮдёӯзҡ„жҲҗеҠҹпјүгҖӮеҸҰдёҖж–№йқўпјҢHEMT е‘ҲзҺ°еҮәжҜ”еҸҢжһҒжҷ¶дҪ“з®ЎиҫғдҪҺзҡ„еҫ®жіўеҷӘеЈ°пјҲйҮ‘еұһж …жһҒз”өйҳ»жҜ”еҚҠеҜјдҪ“еҹәжһҒз”өйҳ»иҰҒдҪҺпјүгҖӮ

• HBT жҷ¶дҪ“з®ЎжҳҜдёҖдёӘе·ҘдҪңеңЁеҫҲй«ҳз”өжөҒеҜҶеәҰдёӢзҡ„еһӮзӣҙжІҹйҒ“еҷЁд»¶пјҲ>100KA/m2пјҢе…·жңүжңҖй«ҳжҲӘжӯўйў‘зҺҮзҡ„HBT зҡ„з”өжөҒеҜҶеәҰз”ҡиҮі>1MA/cm2пјүгҖӮз”ұдәҺе…¶жүҖе…·жңүзҡ„й«ҳзӣёе…ізғӯйҳ»пјҢHBT зҡ„й«ҳеҠҹиҖ—дјҡеүҠејұе…¶еӣәжңүзҡ„дҪҺй—Ёйҷҗз”өеҺӢеҲҶж•ЈжҖ§иҝҷдёӘдјҳзӮ№гҖӮ

• иҷҪ然жҲӘжӯўйў‘зҺҮеҸҜд»ҘжҳҜзұ»дјјзҡ„пјҲзӣҙеҲ°500GHzпјүпјҢеҫ®жіўеҸҢжһҒжҷ¶дҪ“з®ЎйҖҡеёёжҳҜе…·жңүиҫғдҪҺйҳ»жҠ—зҡ„еҷЁд»¶пјҢиҝҷжҳҜз”ұиҫғй«ҳзҡ„и·ЁеҜје’Ңиҫ“е…Ҙз”өе®№жқҘиЎЁеҫҒзҡ„гҖӮиҝҷдјҡдә§з”ҹдёҖдәӣеҗҺжһңпјҢеҢ…жӢ¬еҸҢжһҒжҷ¶дҪ“з®ЎиҫғдҪҺзҡ„иҙҹиҪҪзҒөж•ҸеәҰгҖӮ

зҺ°жңүе·Ҙиүә

иҷҪ然дёҖдёӘи®ҫи®Ўдәәе‘ҳеҸҜиғҪдёҚе®№жҳ“жҺҘи§ҰеҲ°дёҚеҗҢзҡ„е·ҘиүәпјҢдҪҶиҝҳжҳҜеӯҳеңЁдёҖдәӣдёәж•°дёҚеӨҡзҡ„е…·жңүдёӢеҲ—е·Ҙиүәзҡ„еҲ¶йҖ еҺӮ家пјҡ

• 45-пјҢ65-е’Ң90-nm CMOS• 130- nm HBT SiGe

• 100- nm HEMT

• 500- nm HBT InPгҖӮ

еҜ№GaAs HEMT зҡ„ејҖеҸ‘е·Із»ҸеҫҲй•ҝж—¶й—ҙдәҶпјҢе…¶ж …жһҒй•ҝеәҰиҝңиҝңе°ҸдәҺ1μmпјӣе°ұиҫғж—©зҡ„MESFET жҠҖжңҜиҖҢиЁҖпјҢдё»иҰҒзҡ„жҠҖжңҜеҸҳеҢ–жҳҜдёҺжӣҙеҠ еӨҚжқӮзҡ„ејӮиҙЁеӨ–延结жһ„зӣёе…ізҡ„гҖӮзұ»дјјең°пјҢIII-V HBT жҠҖжңҜйҖҡиҝҮе°ҶдҪҺйў‘GaAs еҠҹзҺҮж”ҫеӨ§еҷЁз”ЁдәҺжүӢжңәд№ӢдёӯиҖҢеҸ–еҫ—дәҶе•ҶдёҡдёҠзҡ„жҲҗеҠҹгҖӮеҸӘйңҖйҖҡиҝҮиҪ¬жҚўеҲ°InP еҹәзҡ„жқҗж–ҷзі»з»ҹпјҢиҝҷдёӘжҠҖжңҜдҫҝеҸҜиёҸе…Ҙз”ҡй«ҳйў‘йўҶеҹҹгҖӮ

ж–°иҝ‘пјҢз”ұдәҺжҷ¶дҪ“з®Ўе°әеҜёжҢҒз»ӯдёҚж–ӯең°дёӢйҷҚпјҢзЎ…е·Ҙиүәд№ҹеҗҢж ·зҷ»дёҠдәҶжҜ«зұіжіўиҲһеҸ°гҖӮеҪ“SiGe HBT жҠҖжңҜиў«ејҖеҸ‘еҗҺпјҢиҝҷз§ҚжҠҖжңҜйҖҡиҝҮж·ұдәҡжҜ«зұіе·Ҙиүәиў«еј•е…ҘеҲ°Bi-CMOS еңҶжҷ¶еҺӮпјҢеҫҲеҝ«дҫҝе‘ҲзҺ°еҮәе…·жңүдёҺе®ғ们жүҖеҜ№еә”зҡ„III-V жҠҖжңҜзӣёиҝ‘зҡ„жҲӘжӯўйў‘зҺҮгҖӮд»ҠеӨ©пјҢиҝҷдёӨдёӘжҠҖжңҜдё»иҰҒзҡ„дёҚеҗҢд№ӢеӨ„жҳҜпјҡ1)SiGe HBT жҠҖжңҜе…·жңүжӣҙжҲҗзҶҹзҡ„е·ҘдёҡзҺҜеўғпјҲиҫғй«ҳзҡ„з”өи·ҜеӨҚжқӮзЁӢеәҰе’Ңжү©еұ•дәҶCMOS зҡ„зҺҜеўғпјүпјҢд»ҘеҸҠ2)иҜҘе·ҘиүәиҫғдҪҺзҡ„йӣҶз”өжһҒеҮ»з©ҝз”өеҺӢгҖӮ

еҪ“и°ҲеҲ°еә”з”Ёж—¶пјҢеҶіе®ҡе“Әз§Қе·ҘиүәжңҖйҖӮеҗҲзҡ„дё»иҰҒеӣ зҙ еҸҜиғҪжҳҜдёӢйқўеҮ зӮ№пјҢеҗ„иҮӘзҡ„еҲҶйҮҸеҸ–еҶідәҺеә”з”Ёжғ…еҶөгҖӮ

1) жҖ§иғҪгҖӮиҝҷжҳҜдёҖдёӘе…ій”®еӣ зҙ пјҢзү№еҲ«жҳҜеҜ№дәҺйӮЈдәӣиҰҒжұӮе…·жңүжңҖдҪіжҖ§иғҪзҡ„еә”з”ЁжқҘиҜҙгҖӮ2) зӣ®ж Ү规иҢғгҖӮеә”з”Ёзҡ„规иҢғиҰҒжұӮеҸҜиғҪдјҡж”№еҸҳпјҲйҡҸзқҖж ҮеҮҶзҡ„жј”еҸҳпјүпјҢеҜ№дәҺж–°еә”з”ЁжқҘиҜҙпјҢе…·жңүдёҖе®ҡзЁӢеәҰзҡ„зҒөжҙ»жҖ§д№ҹи®ёжҳҜеҝ…иҰҒзҡ„гҖӮ

3) зӣҙжөҒеҠҹиҖ—гҖӮдёәдәҶеҮҸе°‘и®ҫеӨҮзҡ„е°әеҜёд»ҘеҸҠ移еҠЁз»Ҳз«Ҝзҡ„йҮҚйҮҸе’ҢеҠҹиҖ—пјҢдҪҺеҠҹиҖ—жҳҜдёҖдёӘйҮҚиҰҒзҡ„еӣ зҙ гҖӮ

4) й—Ёж•°гҖӮиҝҷжҳҜеҸҰдёҖдёӘйҮҚиҰҒж–№йқўпјҢеӣ дёәж•°еӯ—дҝЎеҸ·еӨ„зҗҶжӯЈеңЁжҸҗй«ҳе…¶еңЁеә”з”Ёдёӯзҡ„еҲҶйҮҸгҖӮ

5) жҲҗжң¬гҖӮеҫҲжҳҫ然иҝҷжҳҜдёҖдёӘеҫҲйҮҚиҰҒзҡ„й—®йўҳпјҢ并且йҖӮз”ЁдәҺж•ҙдёӘзі»з»ҹгҖӮиҖҢжҲҗжң¬еҸҚиҝҮжқҘеҲҷеҸ–еҶідәҺжүҖйңҖзҡ„еҷЁд»¶ж•°йҮҸпјҲеёӮеңәе®№йҮҸпјүпјҡеҜ№дәҺе°Ҹзҡ„жҲ–дёӯзӯүж•°йҮҸпјҲеҮ еҚғеҲ°еҮ дёҮ件пјүжқҘиҜҙпјҢIII-V е·ҘиүәеҸҜиғҪжҜ”SiGeзҡ„жҲҗжң¬иҰҒдҪҺпјӣеҜ№дәҺжӣҙеӨ§зҡ„ж•°йҮҸпјҢжғ…еҶөеҲҷеҸҜиғҪзӣёеҸҚгҖӮ

жҲҗзҶҹе·Ҙиүәзҡ„д»Ӣз»ҚеҸҠзҺ°зҠ¶

еҹәдәҺGaAs е’ҢInP зҡ„P-HEMTе’ҢM-HEMT

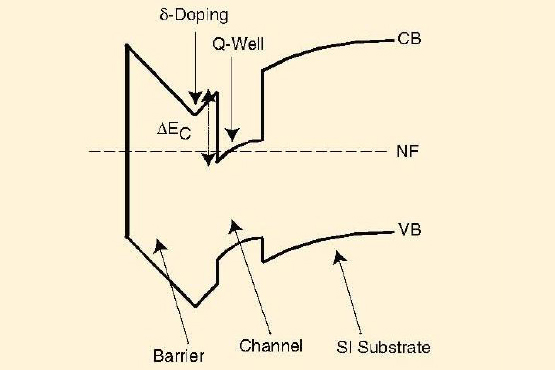

жңҖеҲқпјҢGaAs жҷ¶дҪ“з®ЎжҳҜе…·жңүn- еһӢжІҹйҒ“зҡ„иӮ–зү№еҹәж …FET(MESFET)пјҢеӣ дёәIII-V жқҗж–ҷдёӯз”өеӯҗзҡ„иҝҒ移зҺҮжҜ”з©әз©ҙзҡ„иҝҒ移зҺҮеӨ§еҫ—еӨҡгҖӮдјҡеҰЁзўҚе®һзҺ°MOS з»“жһ„зҡ„иЎЁйқўеҫҲејәзҡ„иҙ№зұіиғҪзә§й’үжүҺж•Ҳеә”еҚҙжңүеҲ©дәҺејҖеҸ‘иӮ–зү№еҹәж …жһҒгҖӮMESFETзҡ„жҖ§иғҪйҖҡиҝҮжҸҗй«ҳжІҹйҒ“зҡ„жҺәжқӮжө“еәҰиҖҢйҖҗжёҗж”№е–„пјӣиҝҷжҳҜд»Ҙз”өеӯҗиҝҒ移зҺҮпјҲеҪ“жҺәжқӮжө“еәҰжҸҗй«ҳж—¶пјҢиҝҒ移зҺҮдёӢйҷҚпјүе’Ңж …жһҒжі„жјҸз”өжөҒдёәд»Јд»·зҡ„гҖӮеңЁ1980 е№ҙжүҖеј•е…Ҙзҡ„HEMT з»“жһ„(и§Ғеӣҫ1) еҸҜд»ҘеҗҢж—¶е®һзҺ°дёӨз§Қж”№е–„пјҡ1) йҖҡиҝҮдёҖдёӘй«ҳиҝҒ移зҺҮжІҹйҒ“жқҘжҸҗй«ҳжІҹйҒ“з”өжөҒпјҲдә§з”ҹдёҖдёӘй«ҳи·ЁеҜјпјүпјҢд»ҘеҸҠ2пјүз”ұдәҺе®ҪиғҪйҡҷеҠҝеһ’иҖҢж”№е–„дәҶж …жһҒжі„жјҸгҖӮ

еӣҫ1гҖҒHEMT ејӮиҙЁз»“жһ„зҡ„иғҪеёҰеӣҫеұ•зӨәдәҶеӨ№еңЁеҚҠ-з»қзјҳпјҲSIпјүеҹәзүҮе’ҢеҠҝеһ’еұӮд№Ӣй—ҙзҡ„зӘ„иғҪйҡҷжІҹйҒ“гҖӮеңЁиҝҷдёӘеӣҫдёӯпјҢеҠҝеһ’еұӮжҳҜδ жҺәжқӮпјҢиҝҷж„Ҹе‘ізқҖе°Ҷж–Ҫдё»жқӮиҙЁеј•е…ҘеҲ°дёҖдёӘжһҒи–„еұӮеҶ…гҖӮжІҹйҒ“дёӯзҡ„з”өеӯҗеңЁз•Ңйқўзҡ„йҮҸеӯҗиӮјдёӯз§ҜзҙҜпјҢз•ҢйқўеҜјеёҰеҒҸ移йҮҸпјҲΔEcпјүжҺ§еҲ¶зқҖиЎЁйқўеҜҶеәҰnsгҖӮ

иҮӘд»ҺHEMT жҠҖжңҜй—®дё–д»ҘжқҘпјҢдәә们已з»Ҹеј•е…ҘдәҶи®ёеӨҡж—ЁеңЁж”№е–„жҖ§иғҪпјҲns е’ҢVsateпјүзҡ„ж”№иҝӣж–№жЎҲгҖӮдёӨз§Қдё»иҰҒзҡ„йҖ”еҫ„жҳҜпјҡ1пјүжҸҗй«ҳеҜјеёҰеҒҸ移пјҢд»ҺиҖҢдҪҝеҫ—еңЁз•ҢйқўйҮҸеӯҗиӮјеҶ…з§ҜзҙҜжӣҙеӨҡзҡ„з”өеӯҗпјҢд»ҘеҸҠ2)жҸҗй«ҳжІҹйҒ“зҡ„иҝҒ移зҺҮпјҢе®һйҷ…дёҠиҝҷж„Ҹе‘ізқҖжҸҗй«ҳInGaAs жІҹйҒ“дёӯIn жҲҗеҲҶзҡ„еҗ«йҮҸпјҲд»Һ常规зҡ„GaAsHEMT зҡ„Xin=0%еҲ°жңҖй«ҳйҖҹInP HEMT дёӯзҡ„Xin=80%пјүгҖӮ

зӣ®еүҚпјҢжӯЈеңЁGaAs еҹәзүҮдёҠејҖеҸ‘дёӨз§Қзұ»еһӢзҡ„HEMT:

1) е…·жңүдёҖеұӮAlGaAs йҡңзўҚеұӮе’ҢдёҖдёӘеә”еҠӣInGaAs жІҹйҒ“зҡ„дё»жөҒGaAs P-HEMTпјҲеҒҮжҷ¶HEMTпјүдё»иҰҒжҳҜз”ЁеңЁ20-70GHz йў‘зҺҮиҢғеӣҙзҡ„дҪҺеҷӘеЈ°жҲ–еҠҹзҺҮеә”з”Ёдёӯ[11]гҖӮ2) йҮҮз”ЁGaAs M-HEMTпјҲж”№жҖ§HEMTпјүеҸҜд»ҘиҺ·еҫ—жӣҙй«ҳзҡ„йҖҹеәҰпјҢе®ғеҹәжң¬дёҠжҳҜдёҖдёӘеңЁGaAs еҹәзүҮзҡ„жқҫејӣзј“еҶІеұӮдёҠз”ҹй•ҝдёҖдёӘжҷ¶ж јеҢ№й…Қзҡ„InP з»“жһ„пјҲе…·жңүдёҖдёӘALInAs/InGaAs ејӮиҙЁз»“з»“жһ„пјүгҖӮиҝҷдёӘз»“жһ„еҫ—зӣҠдәҺInP еҹәз»“жһ„иҫғй«ҳзҡ„йҖҹеәҰе’ҢдёҺиҫғеӨ§пјҢиҫғи„ҶGaAs еҹәзүҮзӣёе…ізҡ„дҪҺжҲҗжң¬гҖӮиҷҪ然缓еҶІеұӮзҡ„зғӯеҜјжҖ§зӣёеҪ“е·®пјҢдҪҶиҝҷдёӘжҠҖжңҜеңЁ100GHz дёӢд»Қ然жҳҫзӨәеҮәеҮәиүІзҡ„еҠҹзҺҮе’ҢеҷӘеЈ°жҖ§иғҪгҖӮ

е°ұжңҖй«ҳиҝҗиЎҢйҖҹеәҰе’Ңиҫғй«ҳзҡ„иҫ“еҮәеҠҹзҺҮиҖҢиЁҖпјҢиҝҷдәӣжҖ§иғҪзәӘеҪ•иҝҳжҳҜз”ұInP PM-HEMT жқҘеҲӣйҖ зҡ„пјҢе®ғеңЁ90GHz ж—¶и¶…иҝҮ400mWпјҢ并且еңЁ300GHz и¶…иҝҮ2mW[14]гҖӮ

InP HBT

иҝһеҗҢйҮҮз”ЁдёҺInP еҹәзүҮжҷ¶ж јеҢ№й…Қзҡ„жқҗж–ҷзі»з»ҹжҲҗеҠҹеҲ¶жҲҗдәҶеҷЁд»¶зҡ„йҰ–зҜҮжҠҘйҒ“дёҖиө·пјҢеңЁ90 е№ҙд»ЈеҗҺжңҹпјҢжңүе…іInP ејӮиҙЁз»“еҸҢжһҒжҖ§жҷ¶дҪ“з®ЎпјҲHBTпјүзҡ„е·ҘдҪңжӯЈејҸиҝҲе…ҘдәҶиҪЁйҒ“[15]гҖӮиҝҷдёӘжқҗж–ҷзі»з»ҹе…·жңүиӢҘе№Іи¶…еҮәSiGe е’ҢGaAs зҡ„дјҳеҠҝпјҢеҢ…жӢ¬пјҡ

1) InGaAsпјҲжҷ¶ж јдёҺInP зӣёеҢ№й…Қпјүжқҗж–ҷдёӯзҡ„иҝҒ移зҺҮе’Ңз”өеӯҗйҖҹеәҰжҜ”GaAs жҲ–SiGe зҡ„жӣҙй«ҳгҖӮ2) дёҺGaAs зӣёжҜ”е…·жңүиҫғдҪҺзҡ„иЎЁйқўеӨҚеҗҲйҖҹзҺҮпјҢд»ҺиҖҢе…·жңүиҫғй«ҳзҡ„з”өжөҒеўһзӣҠпјҢеҜјиҮҙе…¶е…·жңүжҢүжҜ”дҫӢзј©е°ҸеҲ°иҫғе°Ҹе°әеҜёзҡ„иғҪеҠӣгҖӮ

3) з”ұдәҺеңЁеҹәжһҒдёӯдҪҝз”ЁдәҶзӘ„иғҪйҡҷInGaAsпјҢеҲҷе…·жңүжҜ”GaAs иҫғдҪҺзҡ„еҹәжһҒ-еҸ‘е°„жһҒејҖеҗҜз”өеҺӢгҖӮ

4) еҪ“InP иў«з”ЁдҪңйӣҶз”өжһҒжқҗж–ҷж—¶пјҢе…·жңүжҜ”SiGe жӣҙй«ҳзҡ„еҮ»з©ҝз”өеңәејәеәҰгҖӮ

5) дә§е“Ғе…·жңүжҜ”е…¶е®ғд»»дҪ•Si жҲ–III-V жқҗж–ҷжӣҙй«ҳзҡ„еҮ»з©ҝз”өеңә/жҲӘжӯўйў‘зҺҮзҡ„д№ҳз§ҜгҖӮ

6) еңЁInGaAs еҹәжһҒе’ҢInGaAs еҸ‘е°„жһҒиҰҶзӣ–еұӮпјҲCapпјүзҡ„жңҖеӨ§жҺәжқӮжө“еәҰиҫғй«ҳпјҢд»ҺиҖҢдә§з”ҹиҫғдҪҺзҡ„еҜ„з”ҹжҺҘи§Ұз”өйҳ»еҖјгҖӮ

7) з”ұдәҺи®ёеӨҡдёүд»·еҚҠеҜјдҪ“жқҗж–ҷзҡ„жҷ¶ж јдёҺInP зҡ„зӣёеҢ№й…ҚпјҢд»ҺиҖҢе…·жңүдёҖз§Қеўһејәзҡ„“з”ЁиғҪйҡҷжқҘж“Қзәө”HBT зҡ„иғҪеҠӣгҖӮ

иҝҷдәӣе№ҙжқҘпјҢInP HBT е·Із»ҸжӢ…иҙҹиө·жңҖеҝ«йҖҹеҹәеҮҶжҷ¶дҪ“з®Ўе’Ңз”өи·ҜжҖ§иғҪзҡ„йҮҚд»»гҖӮиҝ‘жқҘпјҢеңЁSanta Barbara е’Ңillinois зҡ„з ”з©¶е°Ҹз»„е·Із»ҸжҠҘйҒ“дәҶFt и¶…иҝҮ700GHz зҡ„еҷЁд»¶пјҢд»ҘеҸҠFt/Fmax и¶…иҝҮ500GHz зҡ„е№іиЎЎеҷЁд»¶[16]пјҢ[17]гҖӮ

SiGe HBT-BiCMOSпјӣCMOS е’ҢNMOS

еңЁ80 е№ҙд»ЈеҗҺжңҹжүҖејҖеҸ‘зҡ„SiGe HBT жҳҜйҮҮз”ЁжҲҗзҶҹзҡ„зЎ…жҠҖжңҜжқҘз”ҹдә§зҡ„гҖӮйҖҡиҝҮеҗ„з§ҚејҖеҸ‘пјҢеҢ…жӢ¬еңЁеҹәжһҒдҪҝз”ЁзўіжҺәжқӮе’ҢеҹәжһҒиҮӘеҜ№еҮҶз”ҹй•ҝжҠҖжңҜпјҢеҷЁд»¶е·ІиҫҫеҲ°дәҶеҮәиүІзҡ„жҖ§иғҪ- зү№еҲ«жҳҜпјҢеңЁBi-CMOS й…ҚзҪ®дёӯзҡ„HBT жҳҫзӨәдәҶй«ҳзҡ„FtпјҢFmaxпјҲ>300GHzпјү[19]гҖӮжӯӨеӨ–пјҢз”ұдәҺе…·жңүеҫҲеҘҪзҡ„й’қеҢ–з»“иҖҢиҺ·еҫ—дәҶеңЁж··йў‘еҷЁе’ҢжҢҜиҚЎеҷЁдёӯжһҒдёәжңүз”Ёзҡ„еҮәиүІзҡ„1/f еҷӘеЈ°жҖ§иғҪгҖӮжүҖжңүиҝҷдәӣзү№жҖ§иў«з”ЁжқҘеҲ¶жҲҗдәҶи®ёеӨҡеҸҜд»ҘиҝҗиЎҢзҡ„иҠҜзүҮпјҢдҫӢеҰӮеңЁ43GHz е…үзәӨдј иҫ“зі»з»ҹдёӯзҡ„еӨҡз”ЁеӨҚз”ЁеҷЁпјҲMUXпјүе’ҢеӨҡи·ҜеҲҶзҰ»еҷЁпјҲDEMUXпјүпјҢй«ҳйҖҹжЁЎ-ж•°иҪ¬жҚўеҷЁ[20]пјҢд»ҘеҸҠ77GHz йў‘зҺҮзҡ„иҪҰз”Ёйӣ·иҫҫиҠҜзүҮз»„пјҢз”ҡиҮіеҸҜз”ЁдәҺе·ҘдҪңеңЁ100GHz д»ҘдёҠзҡ„收еҸ‘жңәдёӯ[21]гҖӮ

еңЁиҝҮеҺ»зҡ„еҮ е№ҙдёӯпјҢйҡҸзқҖжһҒзҹӯж …жһҒе·ҘиүәиҝҮзЁӢзҡ„йҮҮзәіпјҲзҺ°еңЁжҳҜеңЁ45-90nm зҡ„иҢғеӣҙпјүпјҢдәә们已з»ҸжҠҘйҒ“дәҶе…·жңүжһҒй«ҳжҲӘжӯўйў‘зҺҮзҡ„n-жІҹйҒ“MOS жҷ¶дҪ“з®ЎпјҲft>200GHzпјү[22]гҖӮиҝҷз§ҚдёҺеҚҠеҜјдҪ“еӣҪйҷ…жҠҖжңҜеҸ‘еұ•и“қеӣҫзӣёдёҖиҮҙзҡ„з»“жһңпјҢе®һйҷ…дёҠжҳҜд»ҺеүҚд»…йҷҗдәҺIII-V HEMTпјҲжҳӮиҙөпјүзҡ„з”өеӯҗжқҹеҠ е·Ҙе·ҘиүәиҝҮзЁӢе’Ңи®ёеӨҡжӯЈеңЁеҸ‘з”ҹзҡ„MOS з»“жһ„жј”еҸҳжүҖдә§з”ҹзҡ„ж …жһҒй•ҝеәҰеҮҸе°Ҹзҡ„з»“жһңгҖӮжӯЈеғҸHEMT з»“жһ„дёҖж ·пјҢйҖҡиҝҮиҫғй«ҳзҡ„иҝҒ移зҺҮжІҹйҒ“пјҲдҫӢеҰӮжүҖиҺ·еҸ–зҡ„еә”еҸҳзЎ…жІҹйҒ“пјүд»ҘеҸҠз”ұжүҖи°“зҡ„й«ҳ-K з”өд»ӢиҙЁж …жһҒжүҖдә§з”ҹзҡ„е…·жңүеҗҲйҖӮзҡ„ж°§еҢ–еұӮеҺҡеәҰдёҺжІҹйҒ“зҡ„й•ҝеәҰжҜ”еҖјпјҢдҪҝеҫ—жҖ§иғҪеҫ—еҲ°дәҶеҠ ејәпјҲз”ұдәҺSiO2 еҸҜд»ҘжҸҗдҫӣж— дёҺдјҰжҜ”зҡ„Si й’қеҢ–дҪңз”ЁпјҢе®ғзҡ„зӣёеҜ№д»Ӣз”өеёёж•°-еҸӘжңү4 -еңЁж …жһҒй•ҝеәҰпјҢж …жһҒеҺҡеәҰжҢүжҜ”дҫӢеҮҸе°Ҹж—¶пјҢе°ұеҸҳеҫ—еӨӘдҪҺдәҶпјүгҖӮ

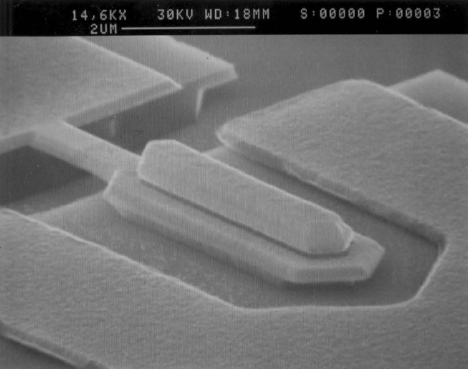

еӣҫ2гҖҒеңЁдә’иҝһд№ӢеүҚпјҢеҸ‘е°„жһҒе®ҪеәҰдёә0.6μm зҡ„InP DHBT зҡ„жҳҫеҫ®з…§зүҮгҖӮHBT жҳҜйҮҮз”ЁдёүеұӮеҸ°йқўпјҲTriple-MesaпјүиҮӘеҜ№еҮҶе·ҘиүәеҲ¶дҪңзҡ„[18]гҖӮ

еҸ—зӣҠдәҺиҝҷз§Қжү©еұ•зҡ„йў‘зҺҮжҖ§иғҪпјҢеңЁиҝҮеҺ»еҮ е№ҙпјҢдәә们已з»ҸеңЁжҜ«зұіжіўйўҶеҹҹеҜ№MOS жҠҖжңҜзҡ„жҪңеҠӣиҝӣиЎҢдәҶеҲқжӯҘзҡ„иҜ„дј°[23]гҖӮй«ҳйӣҶжҲҗеәҰе’ҢдҪҺжҲҗжң¬пјҲеҜ№дәҺеӨ§йҮҸиҠҜзүҮпјүжҳҜжҲ‘们еҜ№зЎ…е·Ҙиүәж„ҹе…ҙи¶Јзҡ„дё»иҰҒеҺҹеӣ гҖӮ

III-V еҷЁд»¶пјҡдёҺCMOSзҡ„е…ұеҗҢйӣҶжҲҗ

дёәдәҶеҗҢж—¶иҺ·еҫ—дёӨз§ҚжҠҖжңҜйўҶеҹҹзҡ„жңҖдҪідјҳеҠҝпјҢејӮиҙЁйӣҶжҲҗе·ҘиүәжҳҜдёҖдёӘйўҮжңүеүҚйҖ”зҡ„и§ЈеҶіж–№жЎҲгҖӮдёәдәҶе°ҶIII-V жҷ¶дҪ“з®ЎпјҲе®һйҷ…дёҠжҳҜInP жҷ¶дҪ“з®Ўпјүе’ҢзЎ…еҹәCMOS иҝӣиЎҢзӣёиҝ‘зҡ„йӣҶжҲҗпјҢдәә们已з»ҸжҺўзҙўдәҶдёҚеҗҢзҡ„йҖ”еҫ„пјҢзү№еҲ«жҳҜеңЁDARPA иө„еҠ©зҡ„COSMOS йЎ№зӣ®дёӯ[24]гҖӮдәә们已з»ҸжҺўзҙўдәҶиӢҘе№Із§Қж–№жі•пјҢд»Һи¶…зә§иҮӘеҜ№еҮҶпјҲе°ҸдәҺ5μmпјүеҖ’иЈ…иҠҜзүҮйӣҶжҲҗеҲ°дёҖдёӘе®Ңе…ЁеҪ»еә•зҡ„еҚ•зүҮеӨұй…ҚеӨ–延жҠҖжңҜгҖӮж—©жңҹзҡ„з»“жһңйқһеёёйј“иҲһдәәеҝғпјҢеңЁе°ҶInP еҷЁд»¶йӣҶжҲҗеҲ°CMOS еңҶжҷ¶зүҮд№ӢеҗҺпјҢInP еҷЁд»¶зҡ„жҖ§иғҪеҠЈеҢ–并дёҚжҳҺжҳҫпјҢ并且已з»Ҹжј”зӨәдәҶдёҖзұ»е…·жңүеӨ§иҫ“еҮәж‘Ҷе№…е’Ңе°ҸеҠҹиҖ—зҡ„еӨ§еўһзӣҠ-еёҰе®Ҫзҡ„е·®еҲҶж”ҫеӨ§еҷЁпјҲ>100GHzпјү[25]гҖӮиҷҪ然没жңүзӣҙжҺҘзҡ„иҒ”зі»пјҢдҪҶдәә们еә”еҪ“жіЁж„ҸеҲ°пјҢйҖҡиҝҮMOSFETжҠҖжңҜдёӯзҡ„й«ҳиҝҒ移зҺҮIII -V жІҹйҒ“еұӮзҡ„з ”з©¶иҖҢеңЁжІҝзқҖеҚҠеҜјдҪ“еӣҪйҷ…жҠҖжңҜи·ҜзәҝеҸ‘еұ•и“қеӣҫйҒ“и·ҜдёҠжүҖеҸ–еҫ—зҡ„иҝӣеұ•[26]гҖӮ

д»Һжҷ¶дҪ“з®ЎеҲ°з”өи·Ҝ

жҲ‘们еңЁдёҠдёҖиҠӮд»Ӣз»ҚдәҶзҺ°жңүзҡ„з”ЁдәҺжңүжәҗеҷЁд»¶зҡ„дёҚеҗҢе·Ҙиүәзҡ„зү№жҖ§гҖӮиҝҷдәӣеҷЁд»¶жҳҜејҖеҗҜ100-GHz д»ҘдёҠйў‘зҺҮеӨ§й—Ёзҡ„е…ій”®пјҢдҪҶиҝҷиҝҳдёҚеӨҹгҖӮеҗҢж ·йңҖиҰҒеҗҲйҖӮзҡ„ж–№ејҸе°Ҷе®ғ们еҸҳдёәеҸҜиҝҗиЎҢзҡ„з”өи·ҜпјҢиҝҷж„Ҹе‘ізқҖдј иҫ“зәҝпјҢж— жәҗеҷЁд»¶е’ҢжҺҘең°зӯүзү№е®ҡйўҶеҹҹзҡ„ејҖеҸ‘гҖӮз”ұдәҺиҝҷдәӣеӣ зҙ пјҢеңЁе°ҶеҷЁд»¶зү№жҖ§иҪ¬жҚўеҲ°еә”з”ЁйўҶеҹҹж—¶пјҢжҹҗдёҖз§Қе·ҘиүәеҸҜиғҪжҜ”е…¶е®ғзҡ„йғҪиҰҒеҘҪгҖӮ

зӣ®еүҚпјҢдәә们已еҸҜд»ҘжҳҺзЎ®дёҚеҗҢжҠҖжңҜеңЁзү№е®ҡж–№йқўзҡ„иғңеҮәпјҢи§ҒиЎЁ3гҖӮ

иҝҷдёӘиЎЁз»ҳеҲ¶дәҶдёҖе№…жј”еҸҳзҺ°зҠ¶зҡ„з”»йқўгҖӮеңЁжҺҘдёӢжқҘзҡ„и®Ёи®әдёӯпјҢе°Ҷз”ЁдёӨз§ҚдёҚеҗҢзұ»еһӢзҡ„жј”зӨәз”өи·ҜжқҘеҜ№з”»йқўиҝӣиЎҢе…·дҪ“зҡ„иҜҙжҳҺгҖӮT.SwanпјҢY.BaeyensпјҢе’ҢM.Meghelli еңЁж–Үз« дёӯеҜ№зү№е®ҡзҡ„100-Gb/s е…үжіўз”өи·ҜеңЁиҜҘж–№йқўзҡ„иҝӣеұ•иҝӣиЎҢдәҶи®Ёи®ә[53]гҖӮ

з”ЁйқҷжҖҒеҲҶйў‘еҷЁдҪңдёәжҠҖжңҜзҡ„иЎЎйҮҸеҹәеҮҶ

з”ЁдәҺж•°еӯ—з”өи·Ҝзҡ„еҚҠеҜјдҪ“е·ҘиүәйҖҡеёёжҳҜз”ЁйқҷжҖҒеҲҶйў‘еҷЁзҡ„жҖ§иғҪжқҘдҪңдёәиЎЎйҮҸеҹәеҮҶзҡ„гҖӮз”ұдәҺдёҖдёӘйқҷжҖҒеҲҶйў‘еҷЁдҪҝз”Ёзҡ„жҳҜеҸҜд»ҘеңЁжӣҙеӨҚжқӮзҡ„ж—¶еәҸз”өи·ҜдёӯжүҫеҲ°зҡ„и§ҰеҸ‘еҷЁеҚ•е…ғе…ғ件[36]пјҢеӣ жӯӨиҝҷж ·дёҖдёӘз”өи·Ҝзҡ„жҖ§иғҪеҸҜд»ҘдҪңдёәе…¬и®Өзҡ„ж•°еӯ—йӣҶжҲҗз”өи·Ҝе·Ҙиүәзҡ„иҙЁйҮҸеӣ ж•°гҖӮзӣёеҗҢзҡ„и§ҰеҸ‘еҷЁиў«з”ЁдҪңеҲҶйў‘еҷЁпјҢеҲӨж–ӯз”өи·ҜпјҢ10/100-Gb/s зі»з»ҹеӨҚз”ЁеҷЁзҡ„еҹәжң¬еҚ•е…ғ[37]гҖӮеңЁдҪҝз”Ёзұ»дјјеҹәзЎҖе…ғ件зҡ„дёҚеҗҢз”өи·ҜдёӯпјҢйҖүжӢ©йқҷжҖҒеҲҶйў‘еҷЁзҡ„еҺҹеӣ жҳҜеӣ дёәе®ғжҒ°еҘҪжҳҜйҮҮз”Ёз®ҖеҚ•зҡ„жөӢйҮҸи®ҫеӨҮжңҖе®№жҳ“иҝӣиЎҢжҳҺзЎ®иҜ„дј°зҡ„з”өи·ҜпјҢ并且е®ғеҸҜд»Ҙз»ҷеҮәиҝҷдёӘжҠҖжңҜжүҖиғҪиҫҫеҲ°зҡ„жҳҺзЎ®зҡ„жҖ§иғҪдёҠйҷҗгҖӮ

еӣҫ3 зӨәеҮәдәҶд»Һ90 е№ҙд»ЈеҲқжңҹзӣҙеҲ°зҺ°еңЁжүҖжҠҘйҒ“зҡ„йқҷжҖҒеҲҶйў‘еҷЁзҡ„йҖҹеәҰгҖӮж•°жҚ®жҳҫзӨәеҮәеңЁиҝҮеҺ»еҮ е№ҙдёӯпјҢеҚідҪҝеңЁ2000е№ҙй«ҳйҖҹе…үзәӨзҡ„еёӮеңәеҙ©жәғд№ӢеҗҺпјҢйҖҹеәҰд№ҹжҳҜеңЁзЁіе®ҡдёҠеҚҮзҡ„гҖӮжңҖиҝ‘зҡ„иҝӣеұ•дёӯеӨ§йғЁеҲҶжҳҜз”ұDARPA йҖҡиҝҮйў‘зҺҮжҚ·еҸҳж•°еӯ—еҗҲжҲҗеҸ‘е°„жңәжҠҖжңҜиҝҷдёӘи®ЎеҲ’пјҲTFASTпјүжүҖиө„еҠ©зҡ„гҖӮжіЁж„ҸпјҢеңЁInP HBT жҠҖжңҜдёҠжӯЈжҢҒз»ӯдёҚж–ӯиҺ·еҫ—жңҖеҘҪзҡ„з»“жһңпјҢSiGe HBT зҙ§йҡҸе…¶еҗҺ[38]гҖӮHEMT жҲ–CMOSеҷЁд»¶жҠҖжңҜеңЁжңҖй«ҳйў‘зҺҮж–№йқўжІЎжңүйӮЈд№Ҳејәзҡ„з«һдәүеҠӣпјҢеӣ дёәеңЁFET дёәеҹәзҡ„еҷЁд»¶дёӯпјҢйңҖиҰҒеӨ§зҡ„еҷЁд»¶е°әеҜёжүҚиғҪиҫҫеҲ°еҝ…иҰҒзҡ„и·ЁеҜјиҰҒжұӮгҖӮиҮід»ҠдёәжӯўпјҢжүҖеҸ‘иЎЁзҡ„йқҷжҖҒеҲҶйў‘еҷЁзҡ„жңҖеҘҪз»“жһңжҳҜйҮҮз”Ё250-nm InP HBT жҠҖжңҜжүҖиҫҫеҲ°зҡ„150GHzпјҢжңҖиҝ‘зҡ„иҝӣеұ•е·Із»ҸйӣҶдёӯеҲ°йҷҚдҪҺеҠҹиҖ—иҝҷж–№йқўдәҶ[39]гҖӮиҝҷдёӘжҖ§иғҪдёҺе…ЁйҖҹзҺҮеҲӨж–ӯз”өи·Ҝзҡ„жҖ§иғҪжҳҜдёҖиҮҙзҡ„пјҢ并且еңЁеӨҡи·ҜеӨҚз”ЁеҷЁ/еӨҡи·ҜеҲҶзҰ»еҷЁпјҲMUX/DEMUXпјүз”өи·Ҝдёӯзҡ„жҖ§иғҪиҝҳжңүеҫҲеӨ§зҡ„еҸ‘еұ•дҪҷең°гҖӮ

еӣҫ3гҖҒйқҷжҖҒйў‘еҲҶеҷЁзҡ„жңҖй«ҳйў‘зҺҮйҡҸзқҖжҠҘйҒ“е№ҙд»ЈиҖҢеҸ‘з”ҹзҡ„еҸҳеҢ–гҖӮжүҖзӨәж•°жҚ®д»…д»…дәҶеҢ…еҗ«дәҶеҪ“ж—¶зү№е®ҡжҠҖжңҜзҡ„жңҖеҘҪз»“жһңгҖӮ

еңЁжңҖй«ҳе·ҘдҪңйҖҹеәҰдёӢпјҢеҠҹиҖ—жҳҜзү№еҲ«йҮҚиҰҒзҡ„пјҢжӯӨж—¶еҚ•дёӘй—Ёз”өи·ҜдјҡжңүеҮ зҷҫжҜ«з“Ұзҡ„еҠҹиҖ—гҖӮиҷҪ然еҠҹиҖ—йҡҸзқҖеҲҶйў‘еҷЁеҲҮжҚўзҺҮзҡ„жҸҗй«ҳиҖҢиҝ…йҖҹеўһй•ҝпјҲдҫӢеҰӮпјҢеңЁ87GHzж—¶жҳҜ23mW[41]пјүпјҢдҪҶCMOS з”ұдәҺе…¶еҮәиүІзҡ„з»“жһңпјҲиҫ“е…Ҙйў‘зҺҮиҢғеӣҙжҳҜ90-100GHz[40]пјүиҖҢеҠ е…ҘдәҶз«һдәүиЎҢеҲ—гҖӮжүҖжҠҘйҒ“зҡ„жңҖеҘҪзҡ„еҠҹиҖ—жҳҜйҮҮз”ЁInP HBT жҠҖжңҜпјҢеңЁ150GHz ж—¶дёә42mW/жҜҸдёӘй”ҒеӯҳеҷЁ[39]гҖӮ

з”ЁжҢҜиҚЎеҷЁпјҲVCOпјүдҪңдёәжҠҖжңҜиЎЎйҮҸеҹәеҮҶ

еҺӢжҺ§жҢҜиҚЎеҷЁпјҲVCOпјүжҳҜ100Gb/s дёІиЎҢеә”зӯ”еҷЁд»ҘеҸҠдёӢжҜ«зұіжіўйҖҡдҝЎпјҢй«ҳеҲҶиҫЁзҺҮйӣ·иҫҫе’ҢжҲҗеғҸзі»з»ҹжүҖеҝ…дёҚеҸҜе°‘зҡ„жһ„е»әжЁЎеқ—гҖӮиҝҷж ·зҡ„жҢҜиҚЎеҷЁиҰҒжұӮе°ҶдҪҺзӣёдҪҚеҷӘеЈ°пјҢй«ҳиҫ“еҮәеҠҹзҺҮе’ҢеҘҪзҡ„зӣҙжөҒ-еҲ°-е°„йў‘иҪ¬жҚўж•ҲзҺҮзӣёз»“еҗҲпјҢзү№еҲ«жҳҜеңЁжңҖй«ҳйў‘зҺҮдёӢгҖӮиҝҷдҫҝиҪ¬жҚўдёәи®ёеӨҡйҮҚиҰҒзҡ„жҠҖжңҜиҰҒжұӮгҖӮ

• жңҖй«ҳжҢҜиҚЎйў‘зҺҮпјҲfmaxпјүеҜ№дәҺдәҡжҜ«зұіжіўж“ҚдҪңжқҘиҜҙжҳҜеҫҲе…ій”®зҡ„пјӣжңҖй«ҳйў‘зҺҮеҹәйў‘жҢҜиҚЎеҷЁжҳҜеҹәдәҺзәізұізә§еҲ«зҡ„InP еҹәHEMTгҖӮжүҖжҠҘйҒ“зҡ„жңҖй«ҳеҹәйў‘жҢҜиҚЎеҷЁжҳҜе·ІжңүеҚҒе№ҙеҺҶеҸІзҡ„213-GHz InP HEMT жҢҜиҚЎеҷЁ[42]гҖӮиҝ‘жқҘпјҢйҮҮз”Ё35-nmж …жһҒInP HEMT жҠҖжңҜе…·жңүFmax дёә600-GHz зҡ„еҷЁд»¶зҡ„fmax зҡ„иҝӣдёҖжӯҘж”№е–„дҪҝеҫ—еҹәйў‘жҢҜиҚЎеҷЁеҸҜд»ҘиҫҫеҲ°346GHz[43] гҖӮInPDHBT жңҖиҝ‘д№ҹеҗҢж ·еұ•зӨәдәҶеңЁдәҡжҜ«зұіжіўйў‘зҺҮзҡ„еҹәйў‘жҢҜиҚЎ[44]гҖӮ

• дёәдәҶиҺ·еҫ—жҢҜиҚЎеҷЁеҘҪзҡ„иҝ‘иҪҪжіўзӣёдҪҚеҷӘеЈ°жҖ§иғҪпјҢйҮҚиҰҒзҡ„жҳҜдҪҝз”Ёе…·жңүдҪҺй—ӘзғҒеҷӘеЈ°зҡ„жҠҖжңҜгҖӮеҸҢжһҒжҠҖжңҜпјҢеҰӮSiGe жҲ–InP HBT йҖҡеёёеҸҜд»ҘжҸҗдҫӣжҜ”иҜёеҰӮHEMTжҲ–CMOS иҝҷзұ»FET жӣҙдҪҺзҡ„1/f жӢҗи§’йў‘зҺҮпјҢиҝҷиҰҒеҪ’еҠҹдәҺиЎЁйқўзҠ¶жҖҒеҪұе“Қзҡ„еҮҸе°‘гҖӮеңЁи§ӮеҜҹиҫғеӨ§йў‘зҺҮеҒҸзҰ»еӨ„зҡ„зӣёдҪҚеҷӘеЈ°ж—¶пјҲдҫӢеҰӮпјҢи·қзҰ»иҪҪжіў1MHz-и§Ғеӣҫ4пјүпјҢжҜ«зұіжіўCMOS жҢҜиҚЎеҷЁжүҖеұ•зӨәзҡ„зӣёдҪҚеҷӘеЈ°дёҺе®ғ们жүҖеҜ№еә”зҡ„SiGe е’ҢInP HBT еҷЁд»¶зҡ„зӣёжҺҘиҝ‘гҖӮиҝҷдёӘжҜ”иҫғ并жңӘе°Ҷи°ғи°җиҢғеӣҙзҡ„еҪұе“ҚиҖғиҷ‘еңЁеҶ…пјҢиҖҢдё”иҝҳдјҡеҸ—еҲ°жӣІи§ЈпјҢеҚіеҰӮж–ҮзҢ®[45]дёӯжүҖжҸҗеҲ°зҡ„пјҢеңЁжІЎжңүиҫ“еҮәзј“еҶІж—¶пјҢжҢҜиҚЎеҷЁжҜ«зұіжіўйў‘зҺҮзӣёдҪҚеҷӘеЈ°дјҡжӣҙеҘҪдёҖдәӣгҖӮ

еӣҫ4гҖҒжүҖжҠҘйҒ“зҡ„йҮҮз”ЁдёҚеҗҢжҠҖжңҜжүҖе®һж–Ҫзҡ„жҜ«зұіжіўжҢҜиҚЎеҷЁзӣёдҪҚеҷӘеЈ°жҰӮи§ӮпјҲеңЁеҒҸзҰ»иҪҪжіў1-MHz еӨ„пјүгҖӮ

• жңҖеҗҺпјҢжҢҜиҚЎеҷЁеңЁжңҖй«ҳйў‘зҺҮдёӢеҸҜе®һзҺ°зҡ„иҫ“еҮәеҠҹзҺҮдҫҝжҲҗдәҶдёҖдёӘйҮҚиҰҒзҡ„и®ҫи®ЎеҸӮж•°пјҢзү№еҲ«жҳҜеҪ“еҷЁд»¶е·ҘдҪңеңЁжҺҘиҝ‘е…¶fmax ж—¶пјҢиҝҷжҳҜеӣ дёәпјҢжӯӨж—¶иҰҒиҝӣдёҖжӯҘж”ҫеӨ§иҫ“еҮәдҝЎеҸ·дјҡеҸҳеҫ—ж јеӨ–еӣ°йҡҫгҖӮдёәдәҶи®©иҫ“еҮәеҠҹзҺҮиҫҫеҲ°жңҖеӨ§пјҢжҢҜиҚЎеҷЁеҶ…йғЁз”өеҺӢзҡ„ж‘Ҷе№…йңҖиҰҒиҫҫеҲ°жңҖеӨ§гҖӮеӨ§еӨҡж•°III-V еҷЁд»¶пјҢеҰӮInP HBT е°ұеҮ»з©ҝз”өеҺӢиҖҢиЁҖе…·жңүдёҚжҠҳдёҚжүЈзҡ„дјҳеҠҝпјҢе°Өе…¶жҳҜеҪ“е…¶дёҺCMOS зӣёжҜ”иҫғж—¶гҖӮиҝҷж ·дҫҝеҸҜд»Ҙдә§з”ҹжүҖжҠҘйҒ“зҡ„иҫғй«ҳзҡ„иҫ“еҮәеҠҹзҺҮгҖӮ

100GHz д»ҘдёҠзҡ„й«ҳж•ҲзҺҮй«ҳеҠҹзҺҮжәҗжҺЁ-жҺЁжҢҜиҚЎеҷЁ

дёәдәҶеңЁ100GHz д»ҘдёҠиҫҫеҲ°иҫғй«ҳзҡ„жҢҜиҚЎеҷЁиҫ“еҮәеҠҹзҺҮпјҢи®ҫи®ЎиҖ…们жӣҙеҖҫеҗ‘дәҺжҺЁ-жҺЁжҢҜиҚЎеҷЁжӢ“жү‘з»“жһ„пјҢеңЁиҝҷдёӘз»“жһ„дёӯпјҢдёӨдёӘд»ҘзӣёеҸҚзӣёдҪҚзӣёиҖҰеҗҲзҡ„жҢҜиҚЎеҷЁзҡ„иҫ“еҮәеҗҲжҲҗеҲ°дёҖиө·жқҘдә§з”ҹдёҖдёӘе…·жңүејәдәҢйҳ¶и°җжіўзҡ„иҫ“еҮәдҝЎеҸ·гҖӮиҝҷдёӘжӢ“жү‘з»“жһ„дҪҝеҫ—еҸҜд»ҘеңЁзҺ°жңүжңүжәҗеҷЁд»¶жҠҖжңҜдёҠе®һзҺ°й«ҳдәҺfmax зҡ„дҝЎеҸ·жәҗпјҢ并且еҸҜд»Ҙе°ҶзҺ°жңүй«ҳ-Q еҖји°җжҢҜеҷЁжҠҖжңҜзҡ„йў‘зҺҮиҢғеӣҙжү©еұ•[46]гҖӮжӯӨеӨ–пјҢйҮҮз”ЁжҺЁ-жҺЁжӢ“жү‘з»“жһ„пјҢеҸҜд»ҘдҪҝз”Ёе·ҘдҪңеңЁеҹәйў‘иҖҢдёҚжҳҜдәҢйҳ¶и°җжіўиҫ“еҮәйў‘зҺҮзҡ„йқҷжҖҒжҲ–еҠЁжҖҒеҲҶйў‘еҷЁжқҘе°ҶзӣёдҪҚй”ҒзӣёзҺҜпјҲPLLпјүзҡ„жҢҜиҚЎеҷЁй”Ғе®ҡпјҢд»Ҙе®һзҺ°йў‘зҺҮй”Ғе®ҡдҝЎеҸ·жәҗпјҢд»ҺиҖҢе°ҶеҲҶйў‘еҷЁзҡ„йҖҹеәҰиҰҒжұӮйҷҚдҪҺдәҶдёҖеҚҠгҖӮ

жҜ«зұіжіўйў‘зҺҮзҡ„жҺЁ-жҺЁжҢҜиҚЎеҷЁзҡ„жҪңеҠӣе·Із»Ҹеҫ—еҲ°дәҶе……еҲҶзҡ„еұ•зӨәгҖӮз”ЁдёҚеҗҢзҡ„еҢ–еҗҲзү©еҚҠеҜјдҪ“жҠҖжңҜжүҖе®һзҺ°зҡ„жҺЁ-жҺЁжҢҜиҚЎеҷЁе·Із»ҸеңЁж–ҮзҢ®дёӯжңүжүҖжҠҘйҒ“пјҡеңЁ[47]дёӯжҠҘйҒ“дәҶзӣҙеҲ°140GHz зҡ„0.13μmGaAs PHEMT жҢҜиҚЎеҷЁпјҢе’ҢеңЁ[48]дёӯжүҖжҠҘйҒ“зҡ„еҸҜд»ҘзӣҙеҲ°278GHz зҡ„SiGe HBT жҢҜиҚЎеҷЁгҖӮеҚідҪҝжҳҜйҮҮз”ЁCMOS жҠҖжңҜд№ҹжҲҗеҠҹең°е®һзҺ°дәҶ100GHzд»ҘдёҠзҡ„дҝЎеҸ·жәҗпјҡдәә们已з»ҸжҠҘйҒ“дәҶдёҖдёӘйҮҮз”Ё130-nmCMOS жҠҖжңҜзҡ„192GHz жҺЁ-жҺЁжҢҜиҚЎеҷЁ[49]гҖӮжңҖиҝ‘пјҢйҮҮз”Ё45-nm CMOS жҠҖжңҜжһ„е»әдәҶдёҖеҸ°е·ҘдҪңеңЁ410GHz зҡ„дҝЎеҸ·жәҗ[50]гҖӮ然иҖҢпјҢеҚідҪҝжҳҜйҮҮз”ЁжҺЁ-жҺЁжӢ“жү‘з»“жһ„пјҢз”ұдәҺзЎ…еҹәй«ҳйҖҹжҠҖжңҜйҷҚдҪҺдәҶзҡ„еҮ»з©ҝз”өеҺӢд»ҘеҸҠзәізұізә§CMOS йңҖиҰҒеңЁдҪҺеҒҸзҪ®з”өеҺӢдёӢе·ҘдҪңпјҢеңЁ100GHz д»ҘдёҠеҸҜд»Ҙи§ӮеҜҹеҲ°CMOS жҺЁ-жҺЁжҢҜиҚЎеҷЁжҳҺжҳҫйҷҚдҪҺдәҶзҡ„иҫ“еҮәеҠҹзҺҮгҖӮдҫӢеҰӮпјҢ410-GHzCMOS дҝЎеҸ·жәҗе…·жңү20nWзҡ„иҫ“еҮәеҠҹзҺҮпјҢиҝҷеҸҜиғҪдёҚи¶ід»Ҙз”ЁеңЁеҸ‘е°„жңәеә”з”ЁдёӯжҲ–й©ұеҠЁжҺҘ收жңәзҡ„ж··йў‘еҷЁдёӯгҖӮжӯЈеҰӮеңЁдёӢеҲ—ж®өиҗҪдёӯжүҖиҜҙжҳҺзҡ„пјҢе…·жңүеҰӮжӯӨй«ҳеҠҹзҺҮзҡ„жҺЁ-жҺЁжҢҜиҚЎеҷЁзҡ„зҗҶжғійҖүжӢ©жҳҜInP еҸҢ-ејӮиҙЁз»“HBTпјҲD-HBTпјүжҠҖжңҜпјҢе®ғе°Ҷй«ҳзҡ„fmax е’Ңй«ҳзҡ„еҮ»з©ҝз”өеҺӢз»“еҗҲеңЁдёҖиө·гҖӮ

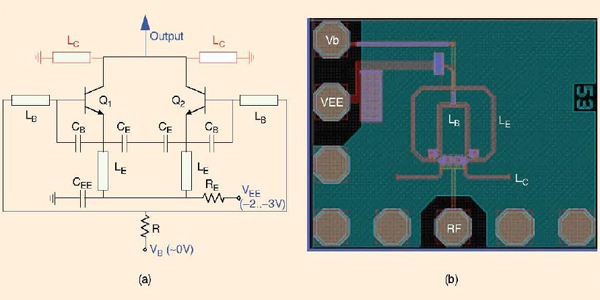

жҢҜиҚЎйў‘зҺҮеңЁ220 е’Ң355GHz зҡ„йӣҶжҲҗжҺЁ-жҺЁжҢҜиҚЎеҷЁжҳҜз”ұAlcatel-Lucent/Bell- е®һйӘҢе®Өзҡ„0.5μm еҸ‘е°„жһҒInGaAs/InP HBT D-HBT жҠҖжңҜжқҘе®һзҺ°зҡ„пјҢе…·жңүзҡ„жңҖеӨ§жҢҜиҚЎйў‘зҺҮдёә335GHz е’Ң4V зҡ„еҮ»з©ҝз”өеҺӢпјҲVbceoпјү[51]гҖӮ

иҝҷдәӣжҢҜиҚЎеҷЁжҳҜеҹәдәҺдёҖз§Қе№іиЎЎColpitts жҢҜиҚЎеҷЁжӢ“жү‘з»“жһ„зҡ„гҖӮйҖҡиҝҮе°ҶзӣёдҪҚзӣёеҸҚзҡ„иҫ“еҮәиҝӣиЎҢеҗҲжҲҗпјҢ并且дҪҝз”Ёзҹӯи·ҜжҲӘзәҝпјҲshort stubпјүйҖҡиҝҮз”өжҠ—йғЁеҲҶеңЁдәҢйҳ¶и°җжіўйў‘зҺҮдёҠжқҘи°ғиҠӮжҢҜиҚЎеҷЁиҫ“еҮәйҳ»жҠ—дҪҝе…¶дә§з”ҹдёҖдёӘеҫҲејәзҡ„дәҢйҳ¶и°җжіўдҝЎеҸ·[52]пјҢеҰӮеӣҫ5 жүҖзӨәгҖӮдәә们已з»ҸйҮҮз”ЁиҝҷдёӘжҠҖжңҜе®һзҺ°дәҶдёҚеҗҢзҡ„и°җжҢҜеҷЁгҖӮеӣҫ5 еұ•зӨәдёҖдёӘ287GHz зҡ„з”өи·ҜеёғеұҖеӣҫгҖӮдј иҫ“зәҝи°җжҢҜеҷЁLEпјҢLB е’ҢLC жҳҜеңЁ7-μm дҪҺ-K еұӮй—ҙд»Ӣз”өжқҗж–ҷпјҲεr=2.6пјүд№ӢдёҠйҮҮз”ЁдёҖдёӘ2-μm еҺҡзҡ„йҮ‘жқҝжҺҘең°йқўйҖҡиҝҮи–„иҶңеҫ®еёҰзәҝжқҘе®һзҺ°зҡ„гҖӮ

еӣҫ5гҖҒдёҖеҸ°InP D-HBT жҺЁ-жҺЁжҢҜиҚЎеҷЁзҡ„пјҲaпјүз”өи·Ҝеӣҫе’ҢпјҲbпјүз”өи·ҜеёғеұҖеӣҫ[52]гҖӮ

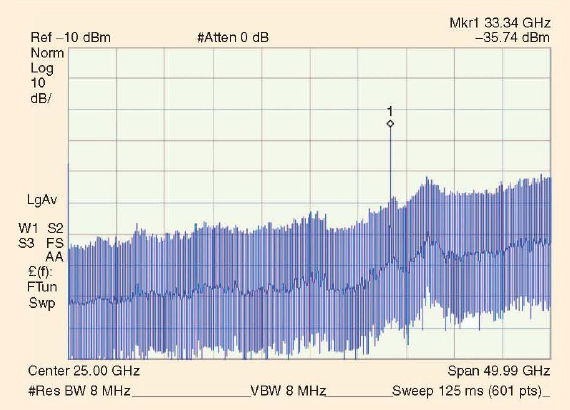

дёҚеҗҢжҢҜиҚЎеҷЁзҡ„иҫ“еҮәдҝЎеҸ·жҳҜйҮҮз”ЁдёҖдёӘWR03 жіўеҜјжҺўеӨҙжқҘжҺўжөӢзҡ„пјҢ并且дҪҝз”ЁWR03 ж¬Ўи°җжіўж··йў‘еҷЁиҝӣиЎҢдёӢеҸҳйў‘зҡ„гҖӮеңЁ210GHz е’Ң235GHz жүҖжөӢеҫ—зҡ„иҫ“еҮәеҠҹзҺҮеҸҜиҫҫ1mWпјҢзӣҙжөҒ-еҲ°-е°„йў‘зҡ„ж•ҲзҺҮдёә2-3%гҖӮе·ҘдҪңеңЁ280 е’Ң297GHz зҡ„жҢҜиҚЎеҷЁеҸҜд»ҘиҺ·еҫ—-5dBm зҡ„иҫ“еҮәеҠҹзҺҮгҖӮеӣҫ6 еұ•зӨәдәҶжүҖе®һзҺ°зҡ„жңҖй«ҳйў‘зҺҮжҢҜиҚЎеҷЁжүҖжөӢеҫ—зҡ„иҫ“еҮәйў‘и°ұгҖӮиҷҪ然иҫ“еҮәи¶…иҝҮдәҶWR03 жіўеҜјпјҲLOпјүеңЁзүҮжҺўеӨҙе’ҢдёӢеҸҳйў‘ж··йў‘еҷЁзҡ„йў‘ж®өиҢғеӣҙпјҢеңЁе°ҶжҢҜиҚЎеҷЁдҝЎеҸ·дёҺ321.6GHz зҡ„жңүж•Ҳжң¬жҢҜйў‘зҺҮзӣёж··йў‘ж—¶пјҢд»Қ然дјҡжҺўжөӢеҲ°еҫҲејәзҡ„IF дҝЎеҸ·гҖӮйҖҡиҝҮеҜ№жҺўеӨҙе’Ңж··йў‘еҷЁжҚҹиҖ—иҝӣиЎҢж ЎжӯЈпјҢжҚҹиҖ—еҖјдј°и®ЎеңЁ23dB дёҺ30dB д№Ӣй—ҙпјҢеңЁ355GHz дёҠеҸҜд»ҘиҺ·еҫ—й«ҳдәҺ-13dBmзҡ„иҫ“еҮәеҠҹзҺҮгҖӮ

еӣҫ6гҖҒдёҖдёӘе·ҘдҪңеңЁ355GHz зҡ„InP D-HBT жҺЁ-жҺЁVCO зҡ„дёӢеҸҳйў‘йў‘и°ұпјҲLO=321.6GHzпјҢдёҠиҫ№еёҰпјүпјҲжңӘеҜ№ж··йў‘еҷЁзҡ„жҚҹиҖ—иҝӣиЎҢд»»дҪ•дҝ®жӯЈпјүгҖӮ

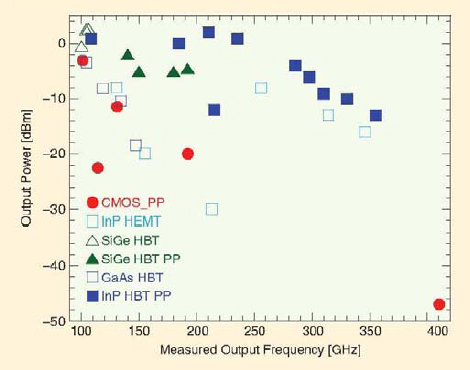

иҝҷдәӣжҢҜиҚЎеҷЁзҡ„иҫ“еҮәеҠҹзҺҮдёҺжҢҜиҚЎйў‘зҺҮзҡ„е…ізі»еұ•зӨәеңЁеӣҫ7 дёӯпјҢ并且е°Ҷе…¶дёҺдёҚеҗҢзҡ„еҚҠеҜјдҪ“жҠҖжңҜжүҖеҲ¶дҪңзҡ„жҢҜиҚЎеҷЁиҝӣиЎҢдәҶжҜ”иҫғгҖӮеӨҡдәҸдәҶInP D-HBT зҡ„й«ҳеҮ»з©ҝз”өеҺӢпјҢд»ҘеҸҠеҸҜд»Ҙе°Ҷиҫ“еҮәеҠҹзҺҮж”№е–„5dB зҡ„дәҢйҳ¶и°җжіўи°ғи°җжҠҖжңҜпјҢжҲӘжӯўзӣ®еүҚдёәжӯўпјҢInP D-HBT жҺЁ-жҺЁжҢҜиҚЎеҷЁеҸҜд»ҘеңЁиҜҘйў‘ж®өиҢғеӣҙеҶ…е…·жңүжҜ”жүҖжҠҘйҒ“зҡ„е…¶е®ғжҷ¶дҪ“з®ЎдҝЎеҸ·жәҗжӣҙй«ҳзҡ„иҫ“еҮәеҠҹзҺҮе’Ңж•ҲзҺҮгҖӮ

еӣҫ7гҖҒжүҖжҠҘйҒ“зҡ„йҮҮз”ЁдёҚеҗҢжҠҖжңҜжүҖе®һж–Ҫзҡ„жҢҜиҚЎеҷЁзҡ„иҫ“еҮәеҠҹзҺҮе’Ңе·ҘдҪңйў‘зҺҮзҡ„жҰӮи§ӮгҖӮйҮҮз”Ёеҹәйў‘е’ҢжҺЁ-жҺЁжҢҜиҚЎеҷЁзҡ„з»“жһңеҲҶеҲ«з”Ёз©әеҝғе’Ңе®һеҝғз¬ҰеҸ·жқҘиЎЁзӨәгҖӮ

з»“и®ә

иӢҘе№Із§ҚеҚҠеҜјдҪ“жқҗж–ҷе’ҢжҠҖжңҜйғҪйҖӮеҗҲз”ЁжқҘи§ЈеҶі100GH е’Ң100-Gb/s зҡ„еә”з”Ёй—®йўҳгҖӮиҝҷдәӣжҠҖжңҜжңүж—¶еҖҷдјҡзӣёдә’з«һдәүпјҢжӯЈеҰӮжҲ‘们жүҖйў„жңҹзҡ„пјҢиҝҷжҳҜдёҖдёӘж–°зҡ„еә”з”ЁйўҶеҹҹпјҢдәә们д»Қ然еңЁеҜ№иҝҷдәӣжҠҖжңҜеҗ„иҮӘзҡ„дјҳзӮ№е’ҢзјәзӮ№иҝӣиЎҢзқҖи®Ёи®әгҖӮжң¬ж–Үж—ЁеңЁиҜҙжҳҺйҡҸзқҖйў‘зҺҮжҖ§иғҪзҡ„дёҚж–ӯжҸҗй«ҳпјҢиҝҷдәӣжј”иҝӣжҠҖжңҜзҡ„еӨҡж ·жҖ§е’Ңе…¶жҪңеңЁзҡ„еҪұе“ҚгҖӮе°Ҫз®Ўй•ҝжңҹд»ҘжқҘпјҢеҷЁд»¶жҖ§иғҪзҡ„ж”№е–„д»…д»…дҫқиө–дәҺе…үеҲ»жҠҖжңҜиҝӣжӯҘжүҖе…Ғи®ёзҡ„е°әеҜёзҡ„еҮҸе°ҸпјҢ然иҖҢејӮиҙЁз»“жһ„е’Ңеә”еҠӣе·ҘзЁӢжҠҖжңҜзҺ°еңЁе·ІжҲҗдёәејәжңүеҠӣзҡ„жүӢж®өпјҢйҖҡиҝҮе®ғ们еҸҜд»ҘеўһејәйҖҹеәҰе’ҢеҠҹзҺҮжҖ§иғҪпјҢдҪҝд№ӢиҫҫеҲ°иғҪеӨҹжү“ејҖ100-GHz е’Ң100-Gb/s еә”з”ЁйўҶеҹҹд№Ӣй—Ёзҡ„ж°ҙе№ігҖӮ

дҪңиҖ…пјҡAndré Scavennec,Marko Sokolich,Yves Baeyens

еҸӮиҖғж–ҮзҢ®

[1] P. H. Siegel, “Terahertz technology,” IEEE Trans. Microwave Theory Tech., vol. 50, pp. 910–928, Mar. 2002.[2] A. Tessmann, I. Kallfass, A. Leuther, H. Massler, M. Kuri, M. Riessle, M. Zink, R. Sommer, A. Wahlen, H. Essen, V. Hurm, M. Schlechtweg, and O. Ambacher, “Metamorphic HEMT MMICs and modules for use in a high-bandwidth 210 GHz radar,” IEEE J. Solid-State Circuits, vol. 43, no. 10, pp. 2194–2205, Oct. 2008.

[3] R. J. Trew, “High frequency solid-state electronic devices,” IEEE Trans. Electron. Devices, vol. 52, pp. 638–649, May 2005.

[4] R. Quay, C. Moglestue, V. Palankovski, and S. Selberherr, “A temperature dependent model for the saturation velocity in semiconductor materials,” Mater. Sci. Semicond. Process., vol. 3, no. 1-2, pp. 149–155, 2000.

[5] Z. Griffith, Y. Dong, D. Scott, Y. Wei, N. Parthasarathy, M. Dahlström, C. Kadow, V. Paidi, M. J. W. Rodwell, M. Urteaga, R. Pierson, P. Rowell, B. Brar, S. Lee, N. X. Nguyen, and C. Nguyen, “Transistor and circuit design for 100–200-GHz ICs,” IEEE J. Solid-State Circuits, vol. 40, no. 10, pp. 2061–2069, Oct. 2005.

[6] M. J. W. Rodwell, M. Urteaga, T. Mathew, D. Scott, D. Mensa, Q. Lee, J. Guthrie, Y. Betser, S. C. Martin, R. P. Smith, S. Jaganathan, S. Krishnan, S. I. Long, R. Pullela, B. Agarwal, U. Battacharya, L. Samoska, and M. Dahlström, “Submicron scaling of HBTs,” IEEE Trans. Electron. Devices, vol. 48, no. 11, pp. 2606–2624, Nov. 2001.

[7] B. Y. Ma, J. Bergman, P. S. Chen, J. B. Hacker, G. Sullivan, B. Brar, “Ultrawideband ultra-low-dc-power high gain differentialinput low noise amplifier MMIC using InAs/AlSb HEMT,” in Proc. Compound Semiconductors ICs Symp., Portland, OR, Oct. 2007, pp. 213–216.

[8] D.-H. Kim and J. A. del Alamo, “30-nm InAs pseudomorphic HEMTs on an InP substrate with a current-gain cutoff frequency of 628 GHz,” IEEE Trans Electron. Device Lett., vol. 29, no. 8, pp. 830–833, Aug. 2008.

[9] M. Micovic, A. Kurdoghlian, H. P. Moyer, P. Hashimoto, M. Hu, M. Antcliffe, P. J. Willadsen, W. S. Wong, R. Bowen, I. Milosavljevic, Y. Yoon, A. Schmitz, W. Wetzel, C. McGuire, B. Hughes, and D. H. Chow, “GaN MMIC for E-band (71 GHz – 95 GHz) radio,” in Proc. Compound Semiconductors ICs Symp., Oct. 2008, pp. 10–13.

[10] M. Higashiwaki, T. Mimura, and T. Matsui, “Enhancementmode AlN/GaN HFETs using Cat-CVD SiN,” IEEE Trans. Electron. Devices, vol. 54, no. 6, pp. 1566–1570, June 2007.

[11] H. Amasuga, A. Inoue, S. Goto, T. Kunii, Y. Yamamoto, T. Oku, and T. Ishikawa, “A high power and high breakdown voltage millimeter- wave GaAs pHEMT,” in IEEE MTT-S Dig. Int. Microwave Symp., 2007, pp. 821–824.

[12] K.J. Herrick, K.W. Brown, F.A. Rose, C.S. Whelan, J. Kotce, J.R. Laroche, Y. Zhang “W-band Metamorphic HEMT with 267 mW Output Power”, in Microwave Symp. Dig., 12–17 June 2005, pp. 843–846.

[13] D. L. Ingram, Y. C. Chen, J. Kraus, B. Brunner, B. Allen, H. C. Yen, and K. F. Lau, “A 427 mW, 20% compact W-band InP HEMT MMIC power amplifier,” in Proc. IEEE Radio Frequency ICs Symp., 1999, pp. 95–98.

[14] W. R. Deal,X.B. Mei, V. Radisic, M.D. Lange, W. Yoshida, P-H. Liu, J. Uyeda, M.E. Barsky, A. Fung, T. Gaier, and R. Lai, “Development of sub-millimeter-wave power amplifiers,” IEEE Trans. Microwave Theory Tech., vol. 55, no. 12, pp. 2719– 2726, Dec. 2007.

[15] B. Jalali, R. N. Nottenburg, Y. K. Chen, A. F. J. Levi, A. Y. Cho, and M. B. Panish, “Scaled AlInAs/InGaAs and InP/InGaAs heterostructure bipolar transistors,” IEEE Trans. Electron. Devices, vol.36, no. 11, p. 2602, Nov. 1989.

[16] Z. Griffith, E. Lind, M. J. W. Rodwell, Xiao-Ming Fang, D. Loubychev, Ying Wu, J. M. Fastenau, and A. W. K. Liu, “Sub-300 nm InGaAs/InP Type-I DHBTs with a 150 nm collector, 30 nm base demonstrating 755 GHz fmax and 416 GHz ft,” in Proc. Indium Phosphide and Related Materials, 2007 (IPRM ‘07), May 14–18, 2007, pp. 403–406.

[17] W. Snodgrass, Bing-Ruey Wu; K. Y. Cheng, and M. Feng, “Type-II GaAsSb/InP DHBTs with Record fT = 670 GHz and Simultaneous fT, fMAX . 400 GHz,” in Proc. IEEE Electronic Devices Meeting, Dec.10–12, 2007, pp. 663–666.

[18] J. Godin, V. Nodjiadjim, M. Riet, P. Berdaguer, O. Drisse, E. Derouin, A. Konczykowska, J. Moulu, J.-Y. Dupuy, F. Jorge, J.-L. Gentner, A. Scavennec, T. Johansen, and V. Krozer, “Submicron InP DHBT technology for high-speed, highswing mixed signal ICs,” in Proc. Compound Semiconductors IC Symp., Monterey, Oct. 12–15, 2008, pp. 109–112.

[19] B. A. Orner, M. Dahlstrom, A. Pothiawala, R. M. Rassel, Q. Liu, H. Ding, M. Khater, D. Ahlgren, A. Joseph, and J. Dunn, “A BiCMOS technology featuring a 300/330 GHz (fT/fmax) SiGe HBT for millimeter wave applications,” in Proc. BCTM, 2006, pp. 49–52.

[20] J. Lee, “High-speed analog-to-digital converters in SiGe technologies,” in Dig. IEEE Compound Semiconductors IC Symp., Portland, Oct. 14–17, 2007, pp. 93–96. [21] E. Laskin, P. Chevallier, A. Chantre, B. Sautreuil, and S. Voinigescu, “165-GHz transceiver in SiGe technology,” IEEE J. Solid-State Circuits, vol. 43, no. 5, pp. 1087–1100, May 2008.

[22] S. Lee, B. Jagannathan, S. Narashimha, A. Chou, N. Zamdmer, J. Johnson, R. Williams, L. Wagner, J. Kim, J.-O. Plouchart, J. Pekarik, S. Springer, and G. Freeman, “Record RF performance of 45-nm SOI CMOS technology,” in Proc. IEDM, 2007, pp. 255–258.

[23] K. K. O, C. Cao, E.-Y. Seok, and S. Sankaran, “100–200 GHz CMOS signal sources and detectors,” in Dig. IEEE Compound Semiconductors IC Symp., Portland, Oct. 14–17, 2007, pp. 11–14.

[24] M. J. Rosker, V. Greanya, and T.-H. Chang, “The DARPA Compound Semiconductor Materials On Silicon (COSMOS) Program,” in Proc. Compound Semiconductors ICs Symp., Oct. 12–15, 2008, pp. 6–9.

[25] J. C. Li, K. R. Eliott, D. S. Matthews, D. A. Hitko, D. M. Zehnder, Y. Royter, P. R. Patterson, T. Hussain, and J. F. Jensen, “100GHz+ gain-bandwidth differential amplifiers in a wafer scale heterogeneously integrated technology using 250nm InP DHBTs and 130 nm CMOS,” in Proc. Compound Semiconductors IC Symp., Monterey, Oct. 12–15, 2008, pp. 227–230.

[26] G. Dewey, M. K. Hudait, K. Lee, R. Pillarisetty, W. Rachmady, M. Radosavljevic, T. Rakshit, and R. Chau, “Carrier transport in high-mobility III-V quantum-well transistors and performance impact for high-speed low-power logic applications,” IEEE Trans. Electron. Device Lett., vol. 29, no. 10, pp. 1094–1097, Oct. 2008.

[27] L. Wang, S. Glisic, J. Borngraeber, W. Winkler, and J.-C. Scheytt, “A singleended fully integrated SiGe 77/79 GHz receiver for automotive radar,” IEEE J. Solid-State Circuits, vol. 43, no. 9, pp. 1897–1908, Sept. 2008.

[28] J. Hallin, T. Kjellberg, and T. Swahn, “A 165-Gb/s 4:1 multiplexor in InP DHBT technology,” IEEE J. Solid-State Circuits, vol. 41, no. 10, pp. 2209–2214, Oct. 2006.

[29] M. Meghelli, “A 132-Gb/s 4:1 multiplexor in 0.13-μm SiGebipolar technology,” IEEE J. Solid-State Circuits, vol. 39, no. 12, pp. 2403–2407, Dec. 2004.

[30] P. Schvan, J. Bach, C. Fait, P. Flemke, R. Gibbins, Y. Greshishchev, N. Ben- Hamida, D. Pollex, J. Sitch, S.-C. Wang, and J. Wolczanski, “A 24GS/s 6b ADC in 90 nm CMOS,” in Dig. Tech. Papers, 2008 Solid-State Circuits Conf. (ISSCC), Feb. 3–7, 2008,pp. 544–638.

[31] B. Chan, B. Oyama, C. Monier, and A. Gutierrez-Aitkin, “An ultra-wideband 7- bit 5-Gsps ADC implemented in submicron InP HBT technology,” IEEE J. Solid- State Circuits, vol. 43, no. 10,pp. 2187–2193, Oct. 2008.

[32] E. Laskin, M. Khanpour, R. Aroca, K. W. Tang, P. Garcia, and S. P. Voinigescu, “A 95 GHz receiver with fundamental-frequency VCO and static frequency divider in 65nm digital CMOS,” in IEEE ISSCC Dig. Tech. Papers, Feb. 2008, p. 180.

[33] T. Suzuki, Y. Nakasha, T. Takahashi, K. Makiyama, T. Hirose, and M. Takikawa, “144-Gbit/s selector and 100-Gbit/s 4:1 multiplexer using InP HEMTs,” in Proc. 2004 IEEE MTT-S Int. Microwave Symp. Dig., June 6–11, 2004, vol. 1, pp. 117–120.

[34] K. Kanda, D. Yamazaki, T. Yamamoto, M. Horinaka, J. Ogawa, H. Tamura, and H. Onodera, “40Gb/s 4:1 MUX/1:4 DEMUX in 90 nm standard CMOS,” in IEEE ISSCC Dig. Tech. Papers, 2005, vol. 1, p. 152.

[35] S. Shahramian, A. C. Carusone, P. Schvan, and S. P. Voinigescu, “An 81 gb/s, 1.2v tiala-retimer in standard 65 nm cmos,” in Proc. IEEE Compound Semiconductor Integrated Circuits Symp., 2008, pp. 1–4.

[36] J. F. Jensen, M. Hafizi, W. E. Stanchina, R. A. Metzger, and D. B. Rensch, “39.5- GHz static frequency divider implemented in AlInAs/GaInAs HBT technology,” in GaAs IC Symp. Tech. Dig., 1992, pp. 101–104.

[37] M. Yoneyama, Y. Miyamoto, T. Otsuji, H. Toba, Y. Yamane, T. Ishibashi, and H. Miyazawa, “Fully electrical 40-Gb/s TDM system prototype based on InP HEMT digital IC technologies,” J. Lightwave Technol., vol. 18, pp. 34–43, Jan. 2000.

[38] S. Trotta, H. Knapp, T. F. Meister, K. Aufinger, J. Böck, W. Simbürger, and A. L. Scholtz, “110-GHz static frequency divider in SiGe bipolar technology,” in CSIC 2005 Dig., 2005, pp. 291–294.

[39] D. A. Hitko, T. Hussain, D. S. Matthews, R. D. Rajavel, I. Milosavljevic, M. Sokolich, “State of the art low power (42 mW per flip-flop) 150 GHz+ CML static divider implemented in scaled 0.2 m emitter-width InP DHBTs,” in Indium Phosphide and Related Materials Conf. Proc., May 7–11, 2006, pp. 85–88.

[40] S. P. Voinigescu, R. Aroca, T. O. Dickson, S. T. Nicolson, T. Chalvatzis, P. Chevalier, P. Garcia, C. Garnier, and B . Sautreuil “Towards a sub-2.5 V, 100-Gb/s serial transceiver,” in Proc. IEEE CICC 2007, pp. 471–478.

[41] D. D. Kim, C. Cho, J. Kim, and J.-O. Plouchart, “Wideband mm- Wave CML static divider in 65nm SOI CMOS technology” in Proc. IEEE CICC 2008, pp. 627– 634.

[42] S.E. Rosenbaum, B.K. Kormanyos, L.M. Jelloian, M. Matloubian,A.S. Brown, L.E. Larson, L.D. Nguyen, M.A. Thompson, L.P.B. Katehi, and G.M. Rebeiz, “155- and 213-GHz AlInAs/GaInAs/InP HEMT MMIC oscillators,” IEEE Trans. MicroIEEE microwave magazine April 2009 86 wave Theory Tech., vol. 43, no. 4, pp. 927–932, Apr. 1995.

[43] V. Radisic, X.B. Mei, W.R. Deal, W. Yoshida, P.H. Liu, J.Uyeda, M. Barsky, L. Samoska, A. Fung, T. Gaier, and R. Lai, “Demonstration of sub-millimeter wave fundamental oscillators using 35-nm InP HEMT technology,” IEEE Microwave Wireless Comp. Lett., vol. 17, no. 3, pp. 223–225, Mar. 2007.

[44] V. Radisic, D. Sawdai, D. Scott, W.R. Deal, L. Dang, D. Li, T. Chen, A. Fung, L. Samoska, T. Gaier, and R. Lai, “Demonstration of a 311-GHz fundamental oscillator using InP HBT technology, IEEE Trans. Microwave Theory Tech., vol. 55, no. 11, pp. 2329–2335, Nov. 2007.

[45] H. Li and H. Rein, “Millimeter-wave VCOs with wide tuning range and low phase noise, fully integrated in a SiGe bipolar production technology,” IEEE J. Solid-State Circuits, vol. 38, no. 2, pp. 184–191, Feb. 2003.

[46] F. Sinnesbichler, “Hybrid millimeter-wave push-push oscillators using silicongermanium HBTs,” IEEE Trans. Microwave Theory Tech., vol. 51, no. 2, pp. 422– 430, Feb. 2003.

[47] S. Kudszus, W.H. Haydl, A. Tessmann, W. Bronner, and M. Schlechtweg, “Pushpush oscillators for 94 and 140 GHz applications using standard pseudomorphic GaAs HEMTs,” in 2001 IEEE MTT-S Int. Microwave Symp. Dig., 2001, vol. 3, pp. 1571–1574.

[48] R. Wanner, R. Lachner, G. Olbrich, and P. Russer, “A SiGe monolithically integrated 278 GHz push-push oscillator,” in Dig. 2007 IEEE/MTT-S Int. Microwave Symp., June 3–8, 2007, pp. 333–336.

[49] C. Cao, E. Seok, and K. K. O, “192 GHz push-push VCO in 0.13 mm CMOS,” Electron. Lett., vol. 42, no. 4, pp. 208–210, Feb. 2006.

[50] E. Seok, K.K.O, “A 410GHz CMOS push-push oscillator with an on-chip patch antenna,” in Dig. Tech. Papers of the 2008 Solid-State Circuits Conf. (ISSCC), Feb. 3–7, 2008, pp. 472–629.

[51] N. Weimann, V. Houtsma, Y. Yang, J. Frackoviak, A. Tate, and Y.K. Chen, “Fully dry-etched Inp double-hetero bipolar transistors with ft > 400 GHz,” in Proc. 2006 IEEE Device Research Conf., State College, PA.

[52] Y. Baeyens, N. Weimann, V. Houtsma, J. Weiner, Y. Yang, J. Frackoviak, P. Roux, A. Tate, and Y.K. Chen, “Highly efficient harmonically tuned InP D-HBT push-push oscillators operating up to 287 GHz,” in Dig. 2007 IEEE/MTT-S Int. Microwave Symp., June 3–8, 2007, pp. 341–344.

[53] T. Swahn, Y. Baeyens, and M. Meghelli, “ICs for 100 Gb/s serial operation,” IEEE Microwave Mag., vol. 10, no. 2, pp. 58–67.

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·