XilinxжңҖж–°е°„йў‘зә§жЁЎжӢҹжҠҖжңҜпјҢе®һзҺ°йқўеҗ‘5Gж— зәҝзҡ„йў иҰҶжҖ§жҠҖжңҜзӘҒз ҙ

ж–°еһӢRFSoC иғҪе°ҶеҠҹиҖ—е’Ңе°ҒиЈ…е°әеҜёеҮҸе°‘50-75%пјҢ

еҜ№й«ҳж•ҲйғЁзҪІ5G еӨ§и§„жЁЎMIMO е’ҢжҜ«зұіжіўж— зәҝеӣһдј иҮіе…ійҮҚиҰҒгҖӮ

з®Җд»Ӣ

йҡҸзқҖйҖҡдҝЎиЎҢдёҡйҖҗжёҗеҗ‘5G ж ҮеҮҶйқ жӢўпјҢ移еҠЁи®ҫеӨҮеҲ¶йҖ е•ҶеҚҒеҲҶй’ҹжғ…дәҺжҠҖжңҜиҜ•йӘҢе’ҢжҰӮеҝөйӘҢиҜҒжөӢиҜ•гҖӮзҺ°еңЁпјҢиҝҷдәӣжҠҖжңҜзҡ„е•ҶдёҡеҸҜиЎҢжҖ§жӯЈеңЁиҝӣиЎҢдёҘж јиҜ„дј°пјҢ然иҖҢеҺҹеһӢи®ҫи®ЎжүҖдҪҝз”Ёзҡ„еҫҲеӨҡжҠҖжңҜйғҪж— жі•еҫҲеҘҪең°иҪ¬еҢ–дёәе•ҶдёҡйғЁзҪІгҖӮ

з”ұдәҺзӣ®ж ҮжҳҜд»ҘжӣҙдҪҺеҠҹиҖ—йҖҡиҝҮйў‘и°ұж•ҲзҺҮгҖҒй«ҳеәҰиҮҙеҜҶеҢ–д»ҘеҸҠж–°йў‘и°ұжқҘжҸҗй«ҳзҪ‘з»ңе®№йҮҸпјҢеӣ жӯӨеҲ¶йҖ е•ҶжӯЈеңЁдҫқйқ иҪҜ件гҖҒ硬件е’Ңзі»з»ҹзә§зҡ„жҠҖжңҜзӘҒз ҙжқҘе®һзҺ°зӣ®ж ҮгҖӮ

жңүдәӣжҠҖжңҜеҜ№ж»Ўи¶ідёҘиӢӣзҡ„зҪ‘з»ңе®№йҮҸзӣ®ж Үе…·жңүиҮіе…ійҮҚиҰҒзҡ„дҪңз”ЁпјҢиҖҢеӨ§и§„жЁЎеӨҡиҫ“е…ҘеӨҡиҫ“еҮәпјҲMIMOпјүеӨ©зәҝйҳөеҲ—е°ұеұһдәҺиҝҷзұ»жҠҖжңҜгҖӮдёҺиҝҷдәӣеӨ©зәҝйҳөеҲ—иҝӣиЎҢжҺҘеҸЈиҝһжҺҘзҡ„е°„йў‘еҚ•е…ғеҝ…йЎ»ж»Ўи¶іжһҒе…¶дёҘж јзҡ„еҠҹиҖ—е’Ңе°ҒиЈ…е°әеҜёиҰҒжұӮпјҢдҪҶеҰӮжһңжІЎжңүзі»з»ҹйӣҶжҲҗж–№йқўзҡ„зӘҒз ҙпјҢиҝҷдәӣзӣ®ж ҮеҫҲеҸҜиғҪж— жі•е®һзҺ°гҖӮ

иөӣзҒөжҖқдёҚж–ӯеңЁеҮҶ5G е’Ң5G жҠҖжңҜзҡ„е®һзҺ°гҖҒиҜ•йӘҢе’Ңе•ҶдёҡеҢ–дёӯжү®жј”дё»иҰҒи§’иүІпјҢдҝғиҝӣзҪ‘з»ңи®ҫи®Ўдёӯзҡ„зҒөжҙ»жҖ§е’ҢеҸҜзј–зЁӢжҖ§гҖӮ

дёәдҪҝеӨ§и§„жЁЎMIMO зі»з»ҹзҡ„е•ҶдёҡеҢ–жҲҗдёәзҺ°е®һпјҢиөӣзҒөжҖқжӯЈжҺЁеҮәйҰ–ж¬ҫйҮҮз”ЁRF зә§жЁЎжӢҹжҠҖжңҜзҡ„е…ЁеҸҜзј–зЁӢпјҲAll ProgrammableпјүRFSoCпјҢиҜҘж–№жЎҲеңЁйӣҶжҲҗж–№йқўеҸ–еҫ—дәҶзӘҒз ҙжҖ§зҡ„иҝӣеұ•пјҢе…¶е°Ҷй«ҳжҖ§иғҪADC е’ҢDAC е®ҢзҫҺйӣҶжҲҗеҲ°дәҶSoC дёӯгҖӮйҖҡиҝҮз”ЁйӣҶжҲҗзӣҙжҺҘRF йҮҮж ·жҠҖжңҜеҸ–д»ЈеҲҶз«Ӣж•°жҚ®иҪ¬жҚўеҷЁпјҢRFSoC еҸҜеүҠеҮҸ50-75% зҡ„еҠҹиҖ—е’Ңе°ҒиЈ…е°әеҜёпјҢиҝҷд№ҹжҳҜеӨ§и§„жЁЎMIMO 5G ж— зәҝз”өе’ҢжҜ«зұіжіўж— зәҝеӣһдј зҡ„е…ій”®гҖӮеҗҢж—¶пјҢSoC дёҺзӣҙжҺҘRF дҝЎеҸ·еӨ„зҗҶзҡ„з»“еҗҲдёәж•°еӯ—еҹҹдёӯжҸҗдҫӣдәҶе…Ёйқўзҡ„зҒөжҙ»жҖ§пјҢе°ҶжҲ‘们дёҺйҖӮеҗҲе•Ҷз”ЁгҖҒйқўеҗ‘ж— зәҝеҹәзЎҖи®ҫж–Ҫзҡ„иҪҜд»¶ж— зәҝз”өзҡ„и·қзҰ»жӢүеҫ—жӣҙиҝ‘дәҶгҖӮ

еҠҹиҖ—дёҺе°ҒиЈ…е°әеҜё –5G е•ҶдёҡйғЁзҪІзҡ„е…ій”®

дј з»ҹ4G е°„йў‘жҺҘе…ҘзҪ‘з»ңпјҲRANпјүйҖҡиҝҮй«ҳжҚҹиҖ—зҡ„еҗҢиҪҙз”өзјҶдёҺиҝңз«Ҝе°„йў‘еҚ•е…ғе»әз«ӢжңүзәҝиҝһжҺҘгҖӮе°Ҫз®Ўиҝңз«Ҝе°„йў‘жһ¶жһ„жҳҜд»Һ3G жј”иҝӣиҖҢжқҘпјҢдҪҶиҜҘж–№жЎҲд»ҚеӯҳеңЁдёҖдәӣй—®йўҳгҖӮд»ҺеӨ©зәҝеҲ°иҝңз«Ҝе°„йў‘еҚ•е…ғзҡ„еҠҹиҖ—дҫқ然йқһеёёеӨ§пјҢиҖҢдё”зі»з»ҹдҪ“з§ҜеӨ§пјҢж— жі•е®һзҺ°еҜҶйӣҶйғЁзҪІгҖӮ

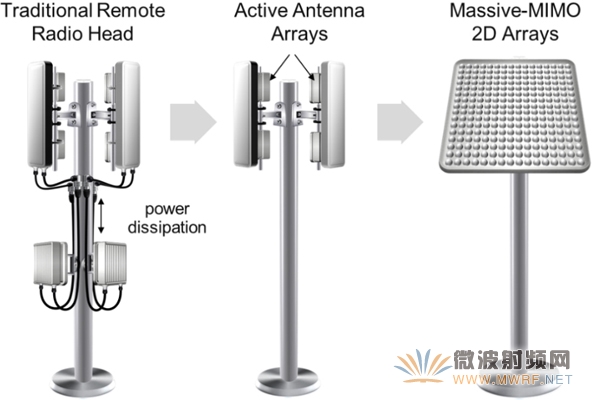

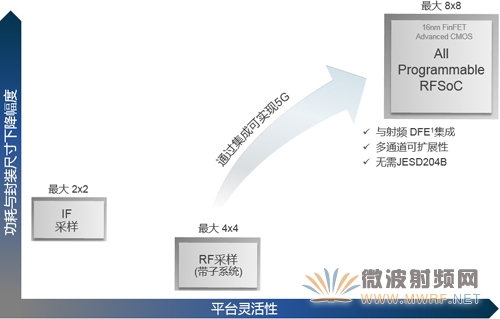

еҰӮеӣҫ1жүҖзӨәпјҢRAN жј”еҸҳиҝҮзЁӢдёӯзҡ„дёӢдёҖжӯҘжҳҜдҪҝз”ЁжңүжәҗеӨ©зәҝйҳөеҲ—пјҲдҪҝж•°еӯ—е’ҢжЁЎжӢҹе°„йў‘еҚ•е…ғдёҺеӨ©зәҝзҡ„и·қзҰ»жӣҙиҝ‘пјүпјҢд»ҘиҠӮзңҒз©әй—ҙпјҢйҒҝе…Қз”өзјҶжҚҹиҖ—е’Ңзӣёе…іеҠҹиҖ—пјҢеҗҢж—¶ж”№е–„й“ҫи·Ҝйў„з®—гҖӮжңүжәҗеӨ©зәҝйҳөеҲ—еңЁ4G еҫҲжҲҗеҠҹпјҢдҪҶжҳҜж— жі•ж»Ўи¶і5G иҝһжҺҘи®ҫеӨҮж•°йҮҸе’Ңз”ЁжҲ·ж•°жҚ®йҖҹзҺҮзҡ„жҸҗй«ҳгҖӮ

еӣҫ1пјҡиҝңз«Ҝе°„йў‘и®ҫеӨҮе’ҢеӨ©зәҝзі»з»ҹзҡ„жј”иҝӣ

еӨ§и§„жЁЎMIMO е’ҢжіўжқҹжҲҗеһӢжҠҖжңҜеҚ и§ЈеҶіж–№жЎҲдёӯзҡ„еҫҲеӨ§дёҖйғЁеҲҶгҖӮж №жҚ®еӣҫ1жүҖзӨәпјҢ“еӨ§и§„жЁЎ”MIMO й…ҚзҪ®еҸҜе°Ҷ32гҖҒ256 з”ҡиҮіеӨҡиҫҫ1024 дёӘзӢ¬з«Ӣ[зү©зҗҶ] еӨ©зәҝж•ҙеҗҲеҲ°дёҖдёӘ2D йҳөеҲ—дёӯгҖӮе®ғ们зҡ„зӣёжҺ§йҳөеҲ—зү№жҖ§иғҪе®һзҺ°й«ҳеҲҶиҫЁзҺҮжіўжҺ§е’ҢжӣҙдҪҺеҠҹиҖ—пјҢе…Ғи®ёиҝӣиЎҢйқһеёёй«ҳеҜҶеәҰзҡ„е®үиЈ…пјҢжҳҫи‘—жҸҗй«ҳжҜҸеҚ•е…ғе®№йҮҸгҖӮжңүдәҶиҝҷз§Қ2D йҳөеҲ—з»“жһ„пјҢе°ұеҸҜд»ҘеңЁйқһдј з»ҹеёғеұҖдёӯдҪҝз”Ёж–°еһӢзҪ‘з»ңжӢ“жү‘з»“жһ„пјҢеҢ…жӢ¬д»Ҙ“з“ҰзүҮ”еҪўејҸе®үиЈ…еҲ°е»әзӯ‘зү©дҫ§йқўпјҢжҲ–йҮҮз”ЁдёҚ规еҲҷеҪўзҠ¶зҡ„е№ҝе‘ҠжқҝжҲ–еҗҚзүҢгҖӮ

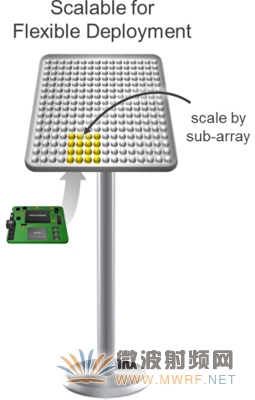

дёәдәҶж”ҜжҢҒиҝҷдәӣеӨ§и§„жЁЎMIMO йҳөеҲ—пјҢиҝңз«Ҝе°„йў‘еҚ•е…ғйңҖиҰҒзҙ§еҮ‘жҖ§пјҢ并且иғҪеӨҹж”ҜжҢҒеӯҗйҳөеҲ—д»Ҙе®һзҺ°зҒөжҙ»е’ҢеҸҜжү©еұ•зҡ„еӨ©зәҝй…ҚзҪ®гҖӮ

еӣҫ 2пјҡйҖҡиҝҮеӯҗзі»з»ҹеҸҜжү©еұ•жҖ§е®һзҺ°зҒөжҙ»ејҖеҸ‘

дёҡз•ҢйҰ–ж¬ҫAllProgrammable RFSoC

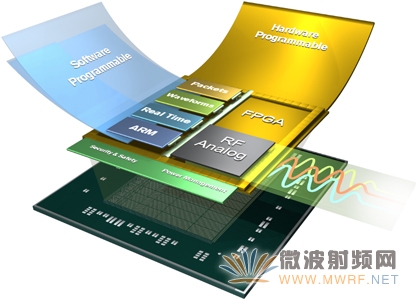

AllProgrammable RFSoC иғҪи§ЈеҶідёҠиҝ°жүҖжңүиҝҷдәӣй—®йўҳгҖӮиҜҘеҷЁд»¶е°ҶйҖҡдҝЎзә§RF йҮҮж ·ж•°жҚ®иҪ¬жҚўеҷЁпјҲй…Қжңүж•°еӯ—еӨ„зҗҶеӯҗзі»з»ҹпјүгҖҒзЁіе®ҡеҸҜйқ зҡ„ARM зә§еӨ„зҗҶзі»з»ҹд»ҘеҸҠFPGA жһ¶жһ„ж•ҙеҗҲеҲ°еҚ•иҠҜзүҮеҷЁд»¶дёӯгҖӮд»ҺиҖҢеңЁйӣҶжҲҗеәҰж–№йқўеҸ–еҫ—дәҶйҮҚеӨ§зӘҒз ҙгҖӮе°Өе…¶жҳҜжЁЎжӢҹеҲ°ж•°еӯ—дҝЎеҸ·й“ҫеҫ—еҲ°зЎ¬еҢ–DSP еӯҗзі»з»ҹзҡ„ж”ҜжҢҒпјҢдҫҝдәҺжЁЎжӢҹи®ҫи®Ўдәәе‘ҳиҝӣиЎҢзҒөжҙ»й…ҚзҪ®гҖӮиҝҷж ·еҸҜе°Ҷзі»з»ҹеҠҹиҖ—е’Ңзі»з»ҹе°әеҜёйҷҚдҪҺ50-75%пјҢ并иҫҫеҲ°жүҖйңҖзҡ„зҒөжҙ»жҖ§д»ҘйҖӮеә”дёҚж–ӯжј”иҝӣзҡ„规иҢғе’ҢзҪ‘з»ңжӢ“жү‘з»“жһ„гҖӮ

еӣҫ3пјҡжҺЁеҮәйҰ–ж¬ҫAll Programmable RFSoC

еҮҸе°‘еҠҹиҖ—гҖҒе°ҒиЈ…е°әеҜёе’Ңи®ҫи®Ўе‘Ёжңҹ

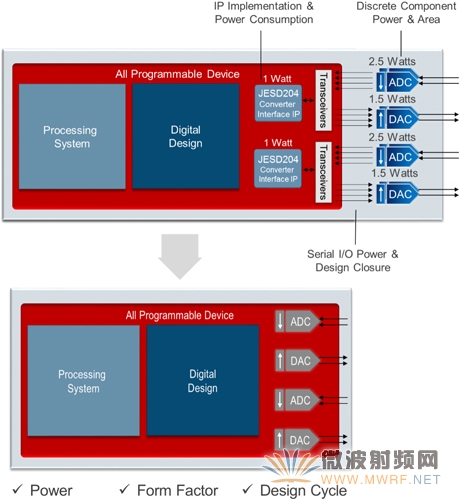

дј з»ҹзҡ„ж— зәҝз”өзі»з»ҹеҢ…еҗ«дёҖдёӘеӨ„зҗҶеҷЁгҖҒеҸҜй…ҚзҪ®йҖ»иҫ‘гҖҒиҝһжҺҘIPпјҢеҪ“然иҝҳжңүж•°жҚ®иҪ¬жҚўеҷЁгҖӮеҪ“еңЁй«ҳRF йў‘зҺҮдёӢе·ҘдҪңж—¶пјҢе…ёеһӢзҡ„еҚ•йҖҡйҒ“ADC зҡ„еҠҹиҖ—зәҰдёә2WпјҢDAC зҡ„еҠҹиҖ—зәҰ1.25WгҖӮйҖҡиҝҮйӣҶжҲҗеҮҸ少组件д№ӢеҗҺпјҢиғҪйҷҚдҪҺеҠҹиҖ—е’Ңе°ҒиЈ…е°әеҜёпјҢиҝҷеҜ№дәҺй«ҳйҖҡйҒ“ж•°зҡ„зі»з»ҹжқҘиҜҙж•Ҳжһңжҳҫи‘—гҖӮйҷӨдәҶиҝҷдәӣдјҳеҠҝд»ҘеӨ–пјҢйӣҶжҲҗиҝҳиғҪжҳҺжҳҫз®ҖеҢ–зі»з»ҹи®ҫи®ЎгҖӮ

дё»иҰҒеҺҹеӣ еңЁдәҺпјҢдёҺеӨ§йҮҸеҲҶз«ӢејҸиҪ¬жҚўеҷЁе»әз«ӢиҝһжҺҘе°ҶйқўдёҙеҫҲеӨ§зҡ„I/O жҢ‘жҲҳгҖӮдёәдәҶйҡҸеёҰе®Ҫжү©еұ•пјҢеӨ§еӨҡж•°ж–°еһӢиҪ¬жҚўеҷЁйғҪдҪҝз”ЁеҹәдәҺJESD204B еҚҸи®®зҡ„йҖҹзҺҮй«ҳиҫҫ12.5Gb/s зҡ„й«ҳйҖҹдёІиЎҢжҺҘеҸЈгҖӮиҝҷз§Қж–№жЎҲеӯҳеңЁеҫҲеӨҡй—®йўҳгҖӮйҰ–е…ҲпјҢJESD204B IP ж ёзҡ„е®һзҺ°йңҖиҰҒж—¶й—ҙпјҢиҰҒдҪҝз”Ёе®қиҙөзҡ„FPGA жһ¶жһ„пјҢ并ж¶ҲиҖ—еӨ§йҮҸзҡ„еҠҹиҖ—гҖӮе…¶ж¬ЎпјҢдёІиЎҢI/O еҠҹиҖ—еңЁжӣҙй«ҳж•°жҚ®йҖҹзҺҮдёӢдјҡжҳҫи‘—еўһеҠ гҖӮдёҚиҝҮпјҢжңҖйҡҫзҡ„иҝҳжҳҜе»әз«ӢдёІиЎҢй“ҫи·ҜгҖӮ12.5Gb/s йҖҹеәҰдёӢзҡ„дҝЎеҸ·еӨұзңҹжҳҜдёӘй—®йўҳпјҢеӨ§еӨҡжҳҜйҖҡиҝҮй«ҳжҚҹиҖ—дҪҺжҲҗжң¬й“ңзјҶиҝһжҺҘиҝҗиЎҢй«ҳзәҝи·ҜйҖҹзҺҮжүҖиҮҙгҖӮиҝҷдёӘиҝҮзЁӢд»ӨдәәдёҚзҲҪпјҢжЁЎжӢҹи®ҫи®Ўдәәе‘ҳиҝ«еҲҮеёҢжңӣи§ЈеҶігҖӮ

еӣҫ4пјҡйҖҡиҝҮйӣҶжҲҗжқҘеҮҸе°ҸеҠҹиҖ—гҖҒе°ҒиЈ…е°әеҜёе’Ңи®ҫи®Ўе‘Ёжңҹ

йӣҶжҲҗиҪ¬жҚўеҷЁд№ӢеҗҺе°ұж— йңҖеҶҚдҪҝз”ЁJESD204B IP ж ёе’ҢдёІиЎҢ收еҸ‘еҷЁгҖӮе…¶дјҳеҠҝдёҚеұҖйҷҗдәҺеҮҸе°‘еҠҹиҖ—е’Ңе°ҒиЈ…е°әеҜёпјҢиҝҳиғҪеӨ§еӨ§зј©зҹӯејҖеҸ‘ж—¶й—ҙгҖӮ

еҠҹиҖ—йҷҚдҪҺиҫҫ50%

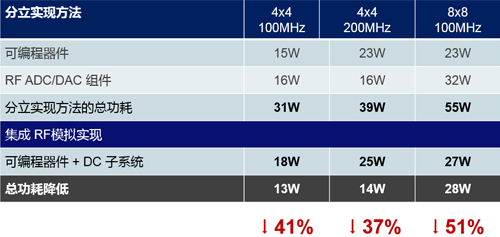

д»ҺеҲқжӯҘжөӢйҮҸз»“жһңжқҘзңӢпјҢеҠҹиҖ—еүҠеҮҸж•ҲжһңжҳҺжҳҫгҖӮеңЁе…ёеһӢ4 и·ҜеҸ‘йҖҒгҖҒ4 и·ҜжҺҘ收пјҲ4Tx/4RxпјүеӨ©зәҝй…ҚзҪ®дёӯпјҢеҲҶз«ӢејҸADC е’ҢDAC зҡ„еҠҹиҖ—жҳҺжҳҫйҷҚдҪҺпјҢд»ҘиҮідәҺд»ҺTable 1дёӯзңӢеҠҹиҖ—йҷҚдҪҺдәҶ40%пјҢ8Tx/8Rx зі»з»ҹзҡ„еҠҹиҖ—йҷҚдҪҺдәҶ50%гҖӮ

иЎЁ1пјҡеҲ©з”ЁйӣҶжҲҗеӯҗзі»з»ҹдёәж•°еӯ—ж— зәҝз”өпјҲеёҰDPDпјүйҷҚдҪҺеҠҹиҖ—

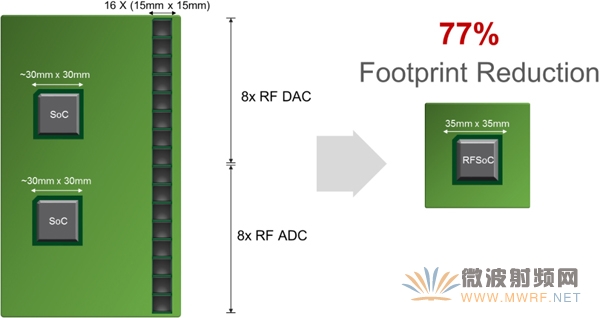

е°ҒиЈ…е°әеҜёеҮҸе°ҸеӨҡиҫҫ75%

е°әеҜёеҮҸе°Ҹзҡ„зЁӢеәҰйҡҸ收еҸ‘еҷЁе’ҢеӨ©зәҝж•°йҮҸиҖҢеўһеҠ пјҢеӣ дёәеҸҜд»ҘйҒҝе…ҚдҪҝз”ЁжӣҙеӨҡиҪ¬жҚўеҷЁгҖӮе•Ҷз”ЁеҷЁд»¶дёӯпјҢе…ёеһӢRF ADC жҲ–DAC жҜҸйҖҡйҒ“еҚ дҪҚйқўз§ҜеҸҜй«ҳиҫҫ15x15mmгҖӮ4Tx4Rx ж— зәҝз”өжһ¶жһ„дёӯзҡ„йқўз§ҜиҠӮзңҒзәҰ50%пјҢеҜ№дәҺжӣҙеӨ§зҡ„ж— зәҝз”өжһ¶жһ„пјҢеҰӮFigure 2дёӯжүҖзӨәзҡ„8Tx/8Rx иҖҢиЁҖпјҢдјҳеҠҝдјҡжҳҫи‘—еўһеҠ пјҢдёәе®Ңе…ЁйғЁзҪІзҡ„еӨҡйҖҡйҒ“зі»з»ҹе®һзҺ°75% д»ҘдёҠзҡ„йқўз§ҜиҠӮзңҒгҖӮиҖғиҷ‘еҲ°жңүеӨҡдёӘеӯҗйҳөеҲ—зҡ„128Tx/128Rx зі»з»ҹдјҡеңЁ5G дёӯжҷ®йҒҚеӯҳеңЁпјҢеӣ иҖҢеҚ дҪҚйқўз§ҜиҠӮзңҒйҮҸе°ҶдјҡйқһеёёеҸҜи§ӮгҖӮйүҙдәҺеҚ•дёӘеӨ©зәҝеҚ•е…ғйқһеёёе°ҸпјҢеҸҜз”Ёйқўз§ҜеҫҲжңүйҷҗпјҢеҜ№дәҺйңҖиҰҒ10гҖҒ20 жҲ–30 еӨҡдёӘеҷЁд»¶зҡ„еҺҹеһӢиҖҢиЁҖпјҢйңҖиҰҒеӨ§е№…зј©еҮҸеҚ дҪҚйқўз§ҜгҖӮ

еӣҫ5пјҡ8Tx8Rx ж— зәҝз”өжһ¶жһ„зҡ„е°ҒиЈ…е°әеҜёзј©еҮҸ

зӣҙжҺҘRF йҮҮз”Ёзҡ„д»·еҖј

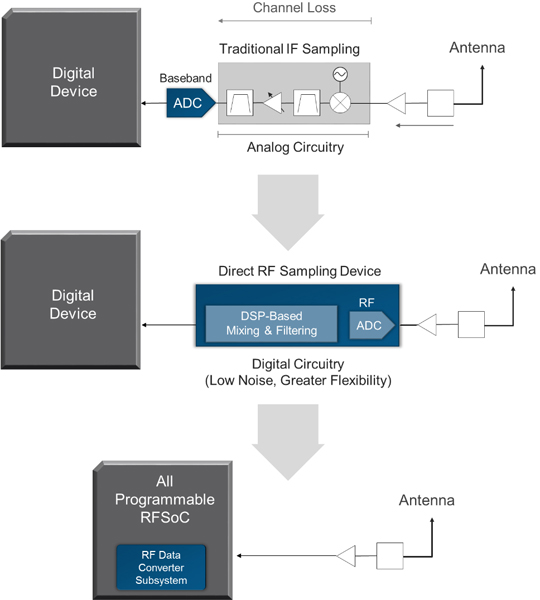

йҷӨдәҶе°әеҜёгҖҒеҠҹиҖ—е’Ңз”ҹдә§еҠӣдјҳеҠҝд»ҘеӨ–пјҢеҸҰдёҖдёӘдёҚиғҪдҪҺдј°зҡ„еӣ зҙ жҳҜеҹәдәҺйўҶе…Ҳзҡ„зӣҙжҺҘRF йҮҮж ·жҠҖжңҜзҡ„иҪ¬жҚўеҷЁеӯҗзі»з»ҹжң¬иә«зҡ„дјҳеҠҝгҖӮиҝҷз§ҚзҺ°д»ЈеҢ–зҡ„йҮҮж ·ж–№жі•еҸҜ“зӣҙжҺҘ”еҜ№иҝӣе…Ҙ/жөҒеҮәзҡ„RF дҝЎеҸ·иҝӣиЎҢйҮҮж ·пјҢж— йңҖдәӢе…Ҳз”ЁжЁЎжӢҹеҷЁд»¶еҒҡд»»дҪ•дҝЎеҸ·и°ғиҠӮгҖӮ

иҝ„д»ҠдёәжӯўпјҢеӨ§йғЁеҲҶзі»з»ҹйғҪйҮҮз”Ёз§°дёәдёӯйў‘пјҲIF жҲ–Zero-IFпјүйҮҮж ·зҡ„жЁЎжӢҹеҢ–ж–№жЎҲпјҢйңҖиҰҒе°ҶеҺҹе§ӢдҝЎеҸ·дёӢеҸҳйў‘еҲ°ADC ж”ҜжҢҒзҡ„йҮҮж ·йў‘зҺҮгҖӮдёӢеҸҳйў‘з”өи·ҜеҢ…еҗ«ж··йў‘еҷЁгҖҒй«ҳиҙЁйҮҸжҢҜиҚЎеҷЁд»ҘеҸҠе…¶д»–жЁЎжӢҹеҷЁд»¶гҖӮжЁЎжӢҹз”өи·ҜзӣёеҜ№жқҘиҜҙдёҚеӨӘзҒөжҙ»пјҢйңҖиҰҒй«ҳеәҰдё“дёҡеҢ–зҡ„и®ҫи®Ўе’ҢеӨҚжқӮзҡ„еҷЁд»¶йҖүжӢ©гҖӮ

зӣҙжҺҘRF йҮҮж ·дёӯпјҢеҸҜзӣҙжҺҘеҜ№жөҒе…Ҙзҡ„RF дҝЎеҸ·йҮҮж ·пјҢж— йңҖдәӢе…ҲиҝӣиЎҢдёӢеҸҳйў‘гҖӮдҝЎеҸ·иў«ж•°еӯ—еҢ–д№ӢеҗҺпјҢеҲ©з”Ёж•°еӯ—дҝЎеҸ·еӨ„зҗҶжҠҖжңҜеңЁжӣҙдёәзҒөжҙ»зҡ„еҸҜзј–зЁӢж•°еӯ—еҹҹдёӯе®ҢжҲҗдёӢеҸҳйў‘е’ҢдҝЎеҸ·еӨ„зҗҶгҖӮиҝҷдәӣRF ADC ж”ҜжҢҒжӣҙй«ҳзҡ„йҮҮж ·зҺҮпјҢз”ұдәҺж•°еӯ—еҹҹжңүжӣҙеҘҪзҡ„ж»ӨжіўжҠҖжңҜпјҢеӣ жӯӨиғҪеӨҹжӣҙеҘҪең°еңЁеҠЁжҖҒиҢғеӣҙгҖҒдҝЎеҸ·иҙЁйҮҸпјҲдҝЎеҷӘжҜ”пјүе’ҢдҝЎеҸ·еёҰе®Ҫд№Ӣй—ҙиҝӣиЎҢжқғиЎЎгҖӮ

иөӣзҒөжҖқйҖҡиҝҮSoC йӣҶжҲҗдҪҝжӯӨж–№жЎҲжӣҙиҝӣдёҖжӯҘпјҢеңЁж•°еӯ—еҹҹе®һзҺ°дәҶе®Ңе…ЁзҒөжҙ»жҖ§пјҢеҗҢж—¶и®©ж— зәҝз”өеӨ„зҗҶдёҺеӨ©зәҝзҡ„и·қзҰ»жӣҙиҝ‘гҖӮз”ұдәҺиғҪеҲ©з”ЁеҗҢдёҖеҷЁд»¶ж»Ўи¶ідёҚеҗҢзҡ„Tx/Rx еӨ©зәҝй…ҚзҪ®е’ҢдёҚж–ӯжј”еҸҳзҡ„ж ҮеҮҶпјҢеӣ жӯӨ移еҠЁи®ҫеӨҮеҺӮе•ҶеҸҜд»ҘеҜ№еёӮеңәеҸҳеҢ–е’ҢжңәйҒҮеҒҡеҮәеҝ«йҖҹе“Қеә”гҖӮеҫҲжҳҺзЎ®пјҢеңЁ5G зҺҜеўғдёӢпјҢжІЎжңүе“Әз§ҚеҚ•дёҖзұ»еһӢзҡ„ж— зәҝз”өжҠҖжңҜиғҪж»Ўи¶ідёӢдёҖд»Јж— зәҝз”өжҺҘе…ҘзҪ‘з»ңзҡ„еӨҡж ·еҢ–йңҖжұӮгҖӮ

еӣҫ 6пјҡзӣҙжҺҘ RF йҮҮж ·е’Ң SoC йӣҶжҲҗ

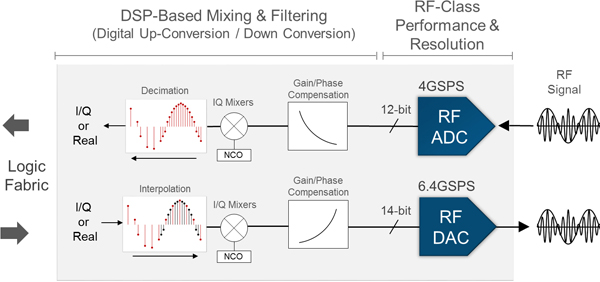

е®Ңж•ҙзҡ„ж•°жҚ®иҪ¬жҚўеҷЁеӯҗзі»з»ҹе®һзҺ°зҒөжҙ»жҖ§

RF ж•°жҚ®иҪ¬жҚўеҷЁеӯҗзі»з»ҹеҢ…жӢ¬ж··йў‘еҷЁгҖҒж•°жҺ§жҢҜиҚЎеҷЁгҖҒжҠҪеҸ–/жҸ’еҖјпјҢд»ҘеҸҠй’ҲеҜ№жҜҸдёӘйҖҡйҒ“зҡ„е…¶д»–ж•°еӯ—дҝЎеҸ·еӨ„зҗҶжҠҖжңҜ——ж”ҜжҢҒз”ЁдәҺIQ еӨ„зҗҶзҡ„еӨҚдҝЎеҸ·гҖӮиҪ¬жҚўеҷЁе…·еӨҮ5G жүҖйңҖзҡ„й«ҳйҮҮж ·зҺҮгҖҒеӨ§еҠЁжҖҒиҢғеӣҙе’ҢеҲҶиҫЁзҺҮгҖӮжңүдәӣжғ…еҶөдёӢпјҢж•°еӯ—дёӢеҸҳйў‘пјҲDDCпјүж— йңҖFPGA иө„жәҗпјҢж•°жҚ®зӣҙжҺҘиҝӣе…ҘйҖ»иҫ‘жһ¶жһ„гҖӮ

еӣҫ7пјҡRFSoC дёӯзҡ„йӣҶжҲҗRF еӯҗзі»з»ҹ

дёҺеҲҶз«ӢејҸRF еҷЁд»¶зҡ„еҜ№жҜ”д»ҘеҸҠ16nm FinFET зҡ„дјҳеҠҝ

зӣҙжҺҘRFйҮҮж ·е·Із»ҸйҖҗжёҗйҮҮз”ЁгҖӮдәӢе®һдёҠпјҢеӣ дёәIFйҮҮж ·еҸҜд»ҘжҸҗеҚҮйқўз§ҜеҸҠеҠҹиҖ—ж•ҲзҺҮпјҢиҝҷз§Қдј з»ҹж–№жі•дҫқ然дҪҝз”Ёжҷ®йҒҚгҖӮиҝҷдәӣи§ЈеҶіж–№жЎҲдёҖиҲ¬з”ЁеңЁиҫғиҖҒзҡ„иҠҜзүҮе·ҘиүәпјҲдҫӢеҰӮ65nmпјүдёҠпјҢдё”жҲҗжң¬дҪҺгҖӮйүҙдәҺRF и®ҫи®Ўз•ҢеҜ№дј з»ҹжЁЎжӢҹдҪҝз”ЁжЁЎеһӢжӣҙеҠ зҶҹжӮүпјҢеӣ жӯӨиҝҷеҫҲеҸҜиғҪжҳҜжңҖйҖӮеҗҲзҡ„ж–№жЎҲгҖӮ

д»Қиў«и®ӨдёәжҳҜ“й«ҳз«Ҝ”зҡ„еҲҶз«ӢејҸзӣҙжҺҘRF ж•°жҚ®иҪ¬жҚўеҷЁйҖҡеёёеҹәдәҺжӣҙе…Ҳиҝӣзҡ„е·ҘиүәиҠӮзӮ№гҖӮиҷҪ然зӣҙжҺҘRFе…·жңүжӣҙејәзҡ„зҒөжҙ»жҖ§пјҢдҪҶз”ұдәҺйңҖиҰҒжӣҙй«ҳзҡ„йҮҮж ·зҺҮпјҢдҪңдёәе…·жңүдё°еҜҢж•°еӯ—еӨ„зҗҶиғҪеҠӣзҡ„еҲҶз«ӢеҷЁд»¶пјҢеҸҜиғҪе…·жңүи¶…иҝҮжЁЎжӢҹе®һзҺ°зҡ„еҠҹиҖ—зјәзӮ№гҖӮ

еҰӮдёӢеӣҫжүҖзӨәпјҢе°Ҫз®ЎзӣҙжҺҘRF йҮҮж ·зӢ¬з«Ӣзҡ„зҒөжҙ»жҖ§дјҳеҠҝе®һе®һеңЁеңЁпјҢйҡҸзқҖеҲҶз«ӢеҷЁд»¶зҡ„йҖ’еўһе’ҢжқғиЎЎеҸ–иҲҚпјҢдјҳеҠҝжӣҙдёәжҳҺжҳҫгҖӮеҗҢж—¶пјҢиҰҒиҫҫеҲ°5GпјҢж— зәҝеҲ¶йҖ е•ҶйңҖиҰҒзҡ„дёҚд»…д»…жҳҜйҖҗжёҗж”№иҝӣгҖӮеҜ№еҠҹиҖ—е’Ңе°әеҜёеүҠеҮҸд»ҘеҸҠзҒөжҙ»жҖ§иҖҢиЁҖпјҢжңҖжңүж„Ҹд№үзҡ„йЈһи·ғжҳҜе…Ёзі»з»ҹйӣҶжҲҗгҖӮйҖҡиҝҮе°ҶRF еүҚз«Ҝе’Ңж— зәҝз”өеүҚз«Ҝз»“еҗҲеҲ°зӣёеҗҢж•°еӯ—еҹҹпјҢзі»з»ҹе’ҢжЁЎжӢҹи®ҫи®Ўе°ұдјҡеҸҳеҫ—жӣҙеҠ зҒөжҙ»гҖӮе®һйҷ…дёҠпјҢйӣҶжҲҗдҪҝRF йҮҮж ·жҲҗдёәжӣҙйҖӮеҗҲйҮҮз”Ёзҡ„жҠҖжңҜпјҢдҪҝиЎҢдёҡжңқе®Ңе…ЁиҪҜд»¶ж— зәҝз”өеҸҲиҝҲиҝӣдёҖжӯҘгҖӮ

з”ұдәҺеҹәдәҺеҸ°з§Ҝз”өпјҲTSMCпјүе…Ҳиҝӣзҡ„16nm FinFET е·ҘиүәпјҲе…·еӨҮеҮәиүІзҡ„жЁЎжӢҹзү№жҖ§пјүпјҢRFSoC дёӯиҪ¬жҚўеҷЁеӯҗзі»з»ҹжң¬иә«е®һзҺ°дәҶеҮәиүІзҡ„еҚ•дҪҚеҠҹиҖ—жҖ§иғҪгҖӮйҖҡиҝҮе°ҶRF еӯҗзі»з»ҹе’Ңж•ҙдёӘдҝЎеҸ·й“ҫжһ„е»әеңЁе…Ҳиҝӣзҡ„CMOS дёҠпјҢRFSoC ејҖеҲӣжҖ§ең°е°Ҷж‘©е°”е®ҡеҫӢеә”з”ЁдәҺжЁЎжӢҹеҹҹгҖӮ

еӣҫ8пјҡй’ҲеҜ№5G ж— зәҝзҡ„ж•°жҚ®иҪ¬жҚўеҷЁжҜ”иҫғ

иөӣзҒөжҖқRFжЁЎжӢҹйӣҶжҲҗз»ҸйӘҢ

й«ҳжҖ§иғҪADC/DAC еңЁ2012е№ҙе°ұиў«йӣҶжҲҗеҲ°дәҶ7 зі»еҲ—FPGAдёӯ——RFSoC д№ӢеүҚзҡ„дә§е“ҒгҖӮз»ҸиҝҮйӘҢиҜҒгҖҒзү№жҖ§жҸҸиҝ°е’Ңе®ўжҲ·зЎ®и®ӨпјҢжөӢиҜ•иҠҜзүҮиғҪеӨҹж¶ҲйҷӨJESD204 жҺҘеҸЈпјҢеұ•зҺ°еҮәдәҶзҒөжҙ»жҖ§дјҳеҠҝпјҢз”ҹдә§еҠӣдјҳеҠҝпјҢд»ҘеҸҠе®һзҺ°йҖҡйҒ“ж•°йҮҸзҡ„жү©еұ•гҖӮжҰӮеҝөйӘҢиҜҒеҸҜжҢҮеҜјд»Ҙеә”з”ЁдёәйҮҚзӮ№зҡ„All Programmable RFSoC ејҖеҸ‘ж–№жЎҲгҖӮ

жҖ»з»“пјҡйқўеҗ‘5G ж— зәҝйўҶеҹҹзҡ„йў иҰҶжҖ§жҠҖжңҜзӘҒз ҙ

еҮӯеҖҹRF зә§жЁЎжӢҹжҠҖжңҜзҡ„жҺЁеҮәпјҢиөӣзҒөжҖқ继з»ӯе…¶зі»з»ҹйӣҶжҲҗдҪҝе‘ҪгҖӮж— и®әиҠҜзүҮзә§е’Ңзі»з»ҹзә§пјҢ移еҠЁеҲ¶йҖ е•ҶйғҪйңҖиҰҒзӘҒз ҙжҖ§жҠҖжңҜд»Ҙдҫҝи¶…еӨ§е°әеҜёзҡ„5G жөӢиҜ•е№іеҸ°е’ҢеҺҹеһӢиҝҮжёЎеҲ°жӣҙе°ҸеһӢгҖҒжӣҙе…·е•ҶдёҡйғЁзҪІд»·еҖјзҡ„зі»з»ҹгҖӮжҖ»д№ӢпјҢRFSoC жӯЈйҖўе…¶ж—¶пјҢи§ЈеҶідәҶ5G ж— зәҝз”өи®ҫи®Ўдёӯзҡ„зҮғзңүд№ӢжҖҘгҖӮ

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·