гҖҖ дёҖз§Қз”ҹдә§еһӢжөӢиҜ•д»Әеә”жңүиҝҷз§ҚиғҪеҠӣпјҢеҚіеңЁеҗ„ж¬ЎжөӢиҜ•й—ҙеҜ№жөӢиҜ•д»Ә硬件е’ҢDUTдҪңеҝ…иҰҒдҝ®ж”№ж—¶пјҢд»ҚдҝқжҢҒж•°еӯ—еӯҗзі»з»ҹзҡ„иҝҗиЎҢгҖӮе®ғдҪҝжөӢиҜ•д»ӘиғҪеӨҹз»ҙжҢҒзӣёеҜ№дәҺDUTиҫ“еҮәзҡ„йҖүйҖҡж—¶еәҸпјҢйҒҝе…ҚеңЁжӯЈејҸиҝҗиЎҢдёӯзҡ„йҖүйҖҡзӣёдҪҚйҮҚи°ғпјҢиҠӮзңҒдәҶжөӢиҜ•ж—¶й—ҙгҖӮ

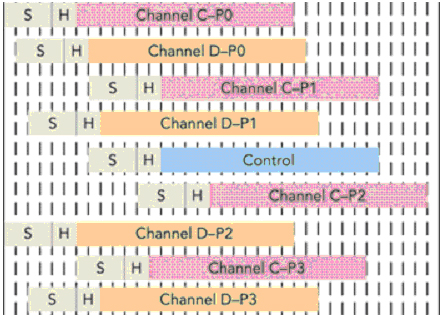

дёӢдёҖдёӘйҮҚиҰҒзҡ„жөӢиҜ•жҢ‘жҲҳжҳҜеҜ»жүҫдёҖдёӘиғҪеӨ„зҗҶеӨҡзә§дёҚзЎ®е®ҡжҖ§ж•°жҚ®еҢ…дј иҫ“жҖ§иғҪзҡ„ж–№ејҸгҖӮеҰӮеӣҫ3жүҖзӨәпјҢеңЁDUTзҡ„жҜҸдёӘRFжҺҘ收жөӢиҜ•жңҹй—ҙпјҢжөӢиҜ•д»ӘйғҪдёҚзҹҘйҒ“жҜҸдёӘеҢ…дјҡеңЁе“ӘдёӘжөӢиҜ•еҫӘзҺҜдёӯдј иҫ“пјҢеҢ…зҡ„зұ»еһӢдјҡжҳҜд»Җд№ҲпјҢжҲ–иҖ…еҢ…зҡ„зұ»еһӢжҳҜеҗҰз¬ҰеҗҲйў„жңҹпјҲдҫӢеҰӮпјҢRFICдјҡз”ҹжҲҗдёҖдёӘдё»еҠЁзҡ„жҺ§еҲ¶зҠ¶жҖҒж¶ҲжҒҜпјүгҖӮ

еӣҫ 3. з”ұдәҺж•°жҚ®еҢ…зҡ„дёҚзЎ®е®ҡжҖ§пјҢеңЁдёҖж¬ҫеҷЁд»¶зҡ„жҜҸж¬ЎRFжҺҘ收жөӢиҜ•жңҹй—ҙпјҢжөӢиҜ•д»ӘдёҚзҹҘйҒ“жҜҸдёӘеҢ…дјҡеңЁе“ӘдёӘжөӢиҜ•еҫӘзҺҜдёӯдј иҫ“пјҢеҢ…зҡ„зұ»еһӢжҳҜд»Җд№ҲпјҢжҲ–иҖ…еҢ…зҡ„зұ»еһӢжҳҜеҗҰз¬ҰеҗҲйў„жңҹгҖӮ

гҖҖгҖҖ马дёҠиғҪзңӢеҮәпјҢжөӢиҜ•зЁӢеәҸдёҚиғҪеңЁж•°еӯ—жөӢиҜ•жЁЎејҸдёӯйҮҮз”Ёеӣәе®ҡеҫӘзҺҜе‘Ёжңҹзҡ„йҖүйҖҡйҡ”зҰ»жүҖйңҖI/Qж•°жҚ®гҖӮеҗҢж ·пјҢеҜ№еҗҢжӯҘжҲ–еӨҙзҡ„ж•°еӯ—еҢ№й…Қеӣһи·ҜдёҚиғҪд»ҘDigRFйҖҹеәҰпјҢи¶іеӨҹеҝ«ең°йҖҡиҝҮATEд»ӘеҷЁзҡ„жөҒж°ҙзәҝпјҢд»ӘеҷЁд№ҹдёҚиғҪе®ҢжҲҗеҜ№еӨҙдҝЎжҒҜзҡ„е®һж—¶иҜҶеҲ«е’ҢеҶізӯ–гҖӮ

гҖҖгҖҖATEзӯ–з•Ҙзҡ„жҜ”иҫғ

гҖҖгҖҖдј з»ҹз”ҹдә§жөӢиҜ•зі»з»ҹжңүйқҷжҖҒзҡ„йҖүйҖҡж—¶еәҸд»ҘеҸҠз®ҖеҚ•зҡ„жҜ”иҫғеҠҹиғҪпјҲдҫӢеҰӮHгҖҒLгҖҒXгҖҒMгҖҒVгҖҒеӯҳеӮЁпјүпјҢеӣ жӯӨе®ғ们иҮӘиә«е№¶дёҚе…·еӨҮејәеӨ§зҡ„ж ЎеҮҶиғҪеҠӣпјҢд»Ҙеә”еҜ№DigRFеҷЁд»¶йңҖиҰҒзҡ„йқһзЎ®е®ҡжҖ§гҖӮдёҚиҝҮпјҢиҝҷзұ»жөӢиҜ•д»Әдёӯзҡ„ж•°еӯ—д»ӘеҷЁжңүжүҖйңҖиҰҒзҡ„ж•°еӯ—жҚ•жҚүиғҪеҠӣпјҢдёҖиҲ¬з”ЁдәҺADCпјҲжЁЎж•°иҪ¬жҚўеҷЁпјүиҫ“еҮәж•°жҚ®жҲ–DUTеҜ„еӯҳеҷЁиҜ»еҸ–ж“ҚдҪңгҖӮеӣ жӯӨпјҢдҪ еҸҜд»Ҙдҝқз•ҷеңЁиҝҷеҸ°д»ӘеҷЁдёҠзҡ„жҠ•иө„пјҢ并且йҮҮз”ЁдёҖз§Қжү№йҮҸжҚ•жҚүе’ҢеҗҺеӨ„зҗҶжҠҖжңҜпјҲblock-capture-and-post-processingпјүеә”еҜ№DigRFзҡ„RFжҺҘ收жөӢиҜ•жҢ‘жҲҳгҖӮ

гҖҖгҖҖеҜ№дәҺRFжҺҘ收жөӢиҜ•пјҢдёҖиҲ¬CWпјҲиҝһз»ӯжіўпјүжөӢиҜ•йңҖиҰҒ1kBиҮі4kBзҡ„I/QйҮҮж ·пјҢиҖҢж—ҘзӣҠжҷ®йҒҚзҡ„йҮҮз”Ёи°ғеҲ¶жіўеҪўзҡ„зі»з»ҹзә§жөӢиҜ•еҲҷдҪҝз”Ё16 kBиҮі32 kBзҡ„I/QйҮҮж ·гҖӮжіЁж„ҸиҪ¬жҚўдёәе®һйҷ…зҡ„дёІиЎҢдҪҚпјҡ

гҖҖгҖҖ1k I/Q = 1024 • [8 bits (I) + 8 bits (Q)] • еҚҸи®®_ејҖй”Җ = дёІиЎҢдҪҚж•°

гҖҖгҖҖдёәдәҶи§ЈеҶіе®һж—¶жғ…еҶөдёӢзҡ„йқһзЎ®е®ҡжҖ§иЎҢдёәпјҢжөӢиҜ•д»Әеҝ…йЎ»жҸҗдҫӣдё“дёәDigRF 3G DUTдёҺж•°еӯ—жҚ•жҚүд№Ӣй—ҙзј–з Ғзҡ„ж•°еӯ—йҖ»иҫ‘гҖӮе…¶зӣ®ж ҮжҳҜеңЁж•°жҚ®еҲ°иҫҫжөӢиҜ•д»Әзҡ„DSPпјҲж•°еӯ—дҝЎеҸ·еӨ„зҗҶеҷЁпјүеүҚпјҢеҮҸиҪ»жҚ•жҚүж—¶жүҖеҮәзҺ°зҡ„жүҖжңүж—¶еәҸдёҺж•°жҚ®дёҚзЎ®е®ҡжҖ§й—®йўҳгҖӮ

дёҖз§ҚжөӢиҜ•йҖүжӢ©жҳҜеңЁDIBпјҲеҷЁд»¶жҺҘеҸЈжқҝпјүдёҠи®ҫи®ЎдёҖдёӘFPGAпјҲзҺ°еңәеҸҜзј–зЁӢй—ЁйҳөеҲ—пјүз”өи·ҜгҖӮиҝҷз§Қж–№жі•еҸҜд»Ҙз”ЁдёҖзүҮе»үд»·еҷЁд»¶жҸҗдҫӣе®ҡеҲ¶йҖ»иҫ‘пјҢдҪҶд№ҹжңүдёүдёӘйә»зғҰпјҡ

•жҺҘеҸЈд»ҘеҸҠдёәз”өи·ҜжҸҗдҫӣж”ҜжҢҒдҝЎеҸ·е°ҶдјҡйқһеёёеӨҚжқӮпјӣ

•еңЁйҡ”зҰ»дёҺеұҸи”ҪиғҪеҠӣжңүйҷҗжғ…еҶөдёӢпјҢеңЁдёҺиҝҷдәӣж•Ҹж„ҹRFдҝЎеҸ·еҰӮжӯӨиҝ‘зҡ„ең°ж–№еўһеҠ дёҖдёӘж•°еӯ—еҷӘеЈ°еҸ‘з”ҹеҷЁпјҢеӯҳеңЁзқҖжӣҙеӨҡзҡ„йЈҺйҷ©пјӣ

•дёәжҜҸдёӘеҷЁд»¶иҙҹиҪҪжқҝеўһеҠ е…ғ件дјҡдҪҝжҲҗжң¬дёҠеҚҮпјҢ延й•ҝжөӢиҜ•ејҖеҸ‘ж—¶й—ҙгҖӮ

гҖҖгҖҖдҪңдёәеҸҰдёҖз§ҚйҖүжӢ©пјҢеҸҜд»ҘйҮҮз”ЁдёҖеҸ°жҸҗдҫӣеөҢе…Ҙе®һж—¶еҠҹиғҪзҡ„ж•°еӯ—жөӢиҜ•д»ӘеҷЁпјҢе®ғеҸҜд»ҘеңЁйҷҚдҪҺжҲҗжң¬зҡ„еҗҢж—¶з®ҖеҢ–DIBеӨҚжқӮжҖ§гҖӮиҝҷз§Қж–№жЎҲзҡ„зјәзӮ№жҳҜзјәд№ҸжөӢиҜ•е·ҘзЁӢеёҲжүҖйңҖиҰҒзҡ„зҒөжҙ»жҖ§пјҢеӣ дёә他们иҰҒжөӢиҜ•дёҖз»„йҖҡдҝЎеҚҸи®®гҖӮеҸӘй’ҲеҜ№DigRFзҡ„и§ЈеҶіж–№жЎҲжҳҜдёҚе®һз”Ёзҡ„гҖӮ

гҖҖгҖҖйҮҮз”Ёиҝҷз§ҚйҖүжӢ©ж—¶пјҢеҪ“жөӢиҜ•зЁӢеәҸзҹҘйҒ“жңүRFжҺҘ收数жҚ®ж—¶пјҢе°ұиғҪеңЁRxDataжҖ»зәҝдёҠжҚ•жҚүеҲ°еӨ§еқ—ж•°жҚ®пјӣиҝҷдёӘеқ—еҝ…йЎ»ж”ҫеӨ§еҲ°иғҪеҸҜйқ ең°жҚ•жҚүи¶іеӨҹзҡ„ж•°жҚ®еҢ…пјҢд»ҺиҖҢжңүи¶іеӨҹж•°йҮҸзҡ„I/QйҮҮж ·з”ЁдәҺеҗҺеӨ„зҗҶз®—жі•гҖӮж•°жҚ®д»Һж•°еӯ—д»ӘеҷЁзҡ„жҚ•жҚүеҶ…еӯҳйҖҒиҮіDSPеј•ж“ҺпјҢеңЁйӮЈйҮҢз”ұдёҖдёӘйў„еӨ„зҗҶз®—жі•жү§иЎҢдёҖдёӘдёүжӯҘеӨ„зҗҶпјҡ

•жүҫеҲ°жҜҸдёӘеҢ…зҡ„иө·е§Ӣзҙўеј•пјӣ

•еҲҶжһҗжҜҸдёӘеҢ…зҡ„еӨҙпјӣ

•йЎәеәҸең°еҜ№жңүж•ҲиҪҪиҚ·дёӯзҡ„I/QйҮҮж ·иҝӣиЎҢеҺ»дәӨй”ҷж“ҚдҪңпјҢ并дҝқеӯҳеңЁж–°зҡ„зӢ¬з«Ӣж•°з»„дёӯгҖӮ

гҖҖгҖҖдёҖж—Ұж•°жҚ®е®ҢжҲҗйў„еӨ„зҗҶпјҢе°ұеҸҜд»ҘеҜ№жүҖйңҖзҡ„I/Qж•°жҚ®йӣҶжү§иЎҢз”ЁжҲ·е®ҡеҲ¶зҡ„еӨ„зҗҶз®—жі•пјҢжҲ–е°Ҷж•°жҚ®йӣҶиҫ“еҮәеҲ°е…¶е®ғATEиҪҜ件е·Ҙе…·пјҢжөӢиҜ•EVMпјҲиҜҜе·®зҹўйҮҸе№…еәҰпјүзӯүзү№жҖ§гҖӮ

гҖҖгҖҖиҝҷдёҖж–№жі•зҡ„жҲҗеҠҹдёҺеҗҰеҸ–еҶіе®ҡдәҺж•°жҚ®з§»еҠЁж—¶й—ҙпјҢд»ҘеҸҠжүҖйңҖеӨ„зҗҶжӯҘйӘӨзҡ„ж•ҲзҺҮгҖӮе°ҪйҮҸеҮҸе°‘жҖ»жөӢиҜ•ж—¶й—ҙзҡ„е…ій”®жҳҜйҒҝе…ҚдёҺдё»жҺ§PCзҡ„дёҚеҝ…иҰҒдәӨдә’пјҢеӣ дёәиҝҷз§ҚдәӨдә’иҰҒжұӮжөӢиҜ•зЁӢеәҸжҡӮеҒңDUTжөӢиҜ•зҡ„жү§иЎҢгҖӮеҰӮжһңжөӢиҜ•д»Әе…·жңүиҫ№еҒҡжЁЎејҸжҚ•жҚүиҫ№з§»еҠЁж•°жҚ®зҡ„иғҪеҠӣпјҢеҲҷеҗ‘DSPдј иҫ“ж•°жҚ®зҡ„ж•ҙдёӘж—¶й—ҙйғҪиў«йҡҗи”ҪеңЁеҗҺеҸ°пјҢжөӢиҜ•ж—¶й—ҙжҳҜйӣ¶жҚҹеӨұгҖӮ

гҖҖгҖҖеҰӮжһңжөӢиҜ•д»ӘжІЎжңүжӯӨйЎ№еҠҹиғҪпјҢеҲҷжөӢиҜ•е·ҘзЁӢеёҲе°ұеҝ…йЎ»еҜ»жүҫиғҪеҮҸ少移еҠЁж•°жҚ®йҮҸзҡ„ж–№жі•гҖӮдёҖдёӘйҖүжӢ©жҳҜеҸӘжҚ•жҚүеӨұж•Ҳж•°жҚ®пјҢдҪҶиҝҷдјҡеңЁDSPдёӯеўһеҠ дёҖдёӘйҮҚжһ„еҺҹе§Ӣж•°жҚ®зҡ„ж–°еӨ„зҗҶжӯҘйӘӨпјӣеҚ•еҚ•иҝҷдёӘдёҚеҝ…иҰҒзҡ„жӯҘйӘӨе°ұдјҡеўһеҠ ж•°жҜ«з§’зҡ„е…ій”®жөӢиҜ•ж—¶й—ҙгҖӮ

гҖҖгҖҖдёҖдёӘе®Ңж•ҙзҡ„DigRFи§ЈеҶіж–№жЎҲйңҖиҰҒе®Ңе…ЁеңЁеҗҺеҸ°жү§иЎҢйў„еӨ„зҗҶз®—жі•е’ҢI/QеӨ„зҗҶгҖӮеӣ жӯӨпјҢ第дёүз§ҚйҖүжӢ©е°ұйңҖиҰҒжөӢиҜ•д»Әжһ¶жһ„иғҪж”ҜжҢҒжү§иЎҢж•°еӯ—дҝЎеҸ·еӨ„зҗҶз®—жі•зҡ„дё“з”ЁеӨ„зҗҶеҷЁпјҢдёҖж—ҰDUTдҝЎеҸ·жҚ•жҚүе®ҢжҲҗпјҢжөӢиҜ•зЁӢеәҸе°ұиғҪз«ӢеҚіејҖе§ӢдёӢдёҖдёӘжөӢиҜ•зҡ„и®ҫзҪ®гҖӮеҸҰеӨ–пјҢеӨҡеқҖжөӢиҜ•д№ҹйңҖиҰҒиҝҷз§ҚеҗҺеҸ°еӨ„зҗҶзҡ„并иЎҢејҸй«ҳж•ҲзҺҮгҖӮ

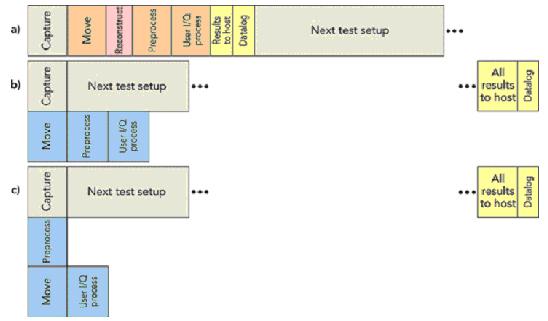

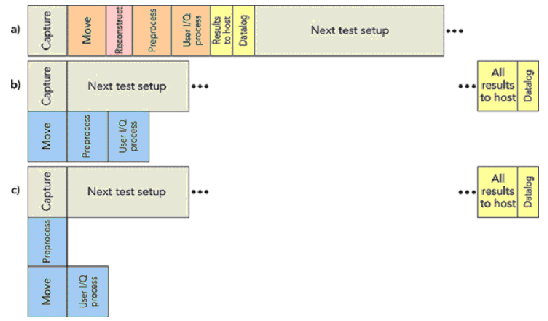

гҖҖгҖҖеӣҫ4иЎЁзӨәиҝҷдёүз§ҚйҖүжӢ©еҜ№жөӢиҜ•ж—¶й—ҙзҡ„еҸҜиғҪеҪұе“ҚгҖӮеҜ№з¬¬дёҖз§ҚйҖүжӢ©пјҢзјәд№ҸеҗҺеҸ°еӨ„зҗҶиҖҢдә§з”ҹдәҶдёҖдёӘдёІиЎҢзҡ„жөӢиҜ•жөҒпјҢжңүжңҖй•ҝзҡ„жөӢиҜ•ж—¶й—ҙгҖӮ第дёүз§Қжғ…еҶөдёӢпјҢйҮҮз”ЁдәҶе®һж—¶еӨ„зҗҶпјҢдјјд№ҺжңҖдёәзҗҶжғіпјҢеӣ дёәе®ғз”Ёе…ЁеҗҺеҸ°еӨ„зҗҶпјҢд»ҘжңҖй«ҳж•Ҳзҡ„ж–№ејҸи§ЈеҶідәҶжөӢиҜ•жҢ‘жҲҳгҖӮ

еӣҫ 4. иҝҷйҮҢжҳҫзӨәзҡ„дёүз§ҚжөӢиҜ•йҖүжӢ©зҡ„жөӢиҜ•ж—¶й—ҙејҖй”Җпјҡ(a) дёІиЎҢжү§иЎҢжөҒпјҢ(b) жү№йҮҸжҚ•жҚүдёҺеҗҺеӨ„зҗҶж–№жЎҲпјҢ(c) е®һж—¶еӨ„зҗҶгҖӮ

гҖҖгҖҖдёҚиҝҮпјҢжү№йҮҸжҚ•жҚүе’ҢеҗҺеӨ„зҗҶж–№жЎҲд№ҹеҸҜд»ҘжңүдҪҺзҡ„жөӢиҜ•ж—¶й—ҙејҖй”ҖпјҢеҸӘиҰҒж•°жҚ®иҪ¬з§»жҳҜеңЁеҗҺеҸ°е®ҢжҲҗпјҢ并且й«ҳж•Ҳең°еӨ„зҗҶпјҢжІЎжңүиў«жөӘиҙ№зҡ„жӯҘйӘӨпјҢ并жңүзӢ¬з«Ӣзҡ„еӨҡеқҖ并иЎҢеӨ„зҗҶеҷЁгҖӮжңүдәҶйҖӮеҪ“зҡ„зі»з»ҹиғҪеҠӣпјҢе…«еқҖзЁӢеәҸзҡ„йў„еӨ„зҗҶеҷЁж—¶й—ҙеҸҜд»ҘдҪҺиҮіж•°жҜ«з§’пјҢи¶ід»Ҙйҡҗи—ҸеңЁдёҖдёӘе…ёеһӢRFжөӢиҜ•ж—¶й—ҙдёӯгҖӮ

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·