"该系统方案利用NI的PXI平台及NI的LabVIEW软件平台进行研发,使我们能专注于802.11ac协议的实现,缩短了研发周期。"

-王孜, 东南大学信息科学与工程学院

挑战:

在WLAN系统开发中,如何设计合理的同步均衡调制等算法,以及达到算法、性能、资源三者之间的折中。此外,在实现数据流实时高速传输时,实现PC,HOST和FPGA三者间的同步通信问题和硬件数据通道测试也十分重要。

解决方案:

在NI-PXI平台上搭建了一个基于IEEE 802.11ac的WLAN原型机,系统主要从PC端、HOST端和FPGA端三个方面进行设计。PC端主要完成视频流的编解码、播放、MAC层协议内容以及系统性能指标的计算和显示。HOST端是连接PC、FPGA、射频卡的重要纽带,主要功能分为对PC端视频流的收发、基带参数和射频参数的传递、DMA_FIFO的建立、FPGA板卡间数据传输及同步配置等。FPGA端的设计是数据处理部分的核心,主要负责射频卡配置、P2P传输,FPGA间同步以及基带数据处理的工作;其中基带数据处理分为发射端和接收端两个部分,发射端实现BCC编码、流解析、调制、插入导频、加CP、IFFT等模块,而接收端实现同步、去CP、FFT、信道估计与均衡、去导频、解SIGB、解调、逆流解析、viterbi译码等各个模块。

作者:

张皓月- 东南大学信息科学与工程学院张晓燕- 东南大学信息科学与工程学院

黄永明- 东南大学信息科学与工程学院

王 孜- 东南大学信息科学与工程学院

杨绿溪- 东南大学信息科学与工程学院

1、引言

面向2020年以后的第五代移动通信技术(5G)是为满足日益增长的移动通信需求而发展的新一代移动通信系统。根据移动通信的发展规律,5G将具有超高的频谱利用率和能效,在传输速率和资源利用率等方面较4G移动通信提高一个量级或更高,其无线覆盖性能、传输时延、系统安全和用户体验也将得到显著的提高。5G移动通信将与其他无线移动通信技术密切结合,构成新一代无所不在的移动信息网络,满足未来10年移动互联网流量增加1000倍的发展需求。5G不再是一种只拥有高速率、高能力、高效率的空口技术,而是一种能够应对不同业务需求并不断提高用户体验的智能网络,5G与其他无线移动通信技术之间的融合将会成为一种必然趋势。Wi-Fi(wireless fidelity)技术已经成为日常生活中必不可少的无线通信技术之一。在热点区域实现Wi-Fi与5G的融合组网将能更有效地起到对现有蜂窝网分流的作用,同时可以大幅提高用户体验,是未来5G的发展方向之一。

无线局域网(Wireless Local Area Network,WLAN)的出现将个人从家中或是办公桌上解放出来,人们可以在宾馆、公园、商店、咖啡厅、机场等任意两点之间进行联网,随时随地获取信息。自1997年IEEE 802.11标准的最初版本完成以来,此后的6年时间里,包括802.11b、802.11a、802.11g在内的标准使得WLAN 的应用日趋广泛并走向成熟。2007年2月,IEEE 802.11n的2.0草案确定,这一新标准的制定具有跨时代意义,在传输速率方面有了突破性的进展,可以达到300 Mbps(20 MHz信道下)甚至600 Mbps(40 MHz信道下)。为应对爆发性增长的流量需求以及提供良好的后向兼容性,被业界认为是第五代Wi-Fi的IEEE 802.11ac呼之欲出。IEEE内部设立了两个项目工作组(Task Group,TG),以甚高吞吐率(Very High Throughput,VHT)为目标,针对未来无线网络应用方向,提出两个项目方案进行立项研究——IEEE 802.11ac与IEEE 802.11ad。2014年1月,802.11ac草案正式获得通过。

IEEE 802.11ac协议在8条空间流、256QAM调制、5/6编码码率、160MHz 传输带宽,400ns保护间隔的条件下,物理层传输速率可高达6933.3Mb/s。作为802.11n标准的一种延续,802.11ac在原有基础上有很大改进。除了使用关键的正交频分复用、多输入多输出技术以及空时编码之外,802.11ac还引入了多用户多输入多输出(MU-MIMO)技术,可以使用更高阶数的调制——256-QAM使得传输速率成倍提升。此外,802.11ac对于信道带宽进行了扩展,在802.11n的20MHz(可选40 MHz)信道的基础上增至40MHz、80MHz,甚至达到160MHz。物理层的帧结构增加了VHT_SIG_B区域,用来描述所要传输的数据长度、调制方式和编码策略(Modulation and Coding Scheme,MCS)以及单用户/多用户模式。当然,满足上述要求也面临着复杂技术带来的更大挑战。

802.11ac能提供高速的传输速率、良好的用户体验等,但由于其机制的复杂性,系统硬件实现的难度加大。目前802.11ac的设备在市场上还不是很多,本文研究基于IEEE 802.11ac的超高速WLAN系统,并借助NI-PXI平台对其原型机进行开发验证,这对新一代Wi-Fi技术及5G技术的研究具有重要意义。

2、设计目标

本文旨在NI-PXI平台上实现一个基于IEEE802.11ac标准的系统原型机。该系统设计的参数指标如下所示:

1)系统基于IEEE 802.11ac协议;2)系统运行在2.4GHz/5GHz频段;

3)系统配置2个发射天线和2个接收天线;

4)系统的传输带宽达到20MHz;

5)调制可选方式:BPSK、QPSK、16QAM、64QAM、256QAM,并可根据接收信噪比实现自适应调制;

6)系统频谱效率:最高可达10 bit/s/Hz(在64QAM映射方式,码率为‘5/6’的条件下);

7)可以显示解调后的接收星座图;

8)可以实现视频的高质量传输。

原型机需要实现的IEEE 802.11ac协议物理层内容有:

1)发射端:BCC编码、流解析、调制、插入导频、加CP、IFFT;2)接收端:同步、去CP、FFT、信道估计与均衡、去导频、解调、逆流解析、维特比译码。

3、基于NI的802.11ac超高速无线局域网原型机

3.1、概述

该项目需要达到百兆数量级的数据传输速率,因而需求高速率的数据处理,在硬件实现中,我们选择了运用高性能FPGA来达到高速率的要求,然而开发这样一个系统需要我们很好的掌握VHDL或者Verilog HDL语言。同时,该项目还涉及了射频方面,这对我们来说也是一个巨大的困难,我们只希望将重点放在802.11ac协议的基带设计上,NI的LabVIEW软件及它的硬件平台对我们来说是一个福音,解决了我们的所有烦恼,让我们能专注于我们想专注的事,极大的缩短了我们的开发周期。

在下文中,我们将具体描述基于NI的802.11ac超高速无线局域网原型机。

3.2、硬件平台

原型机的硬件设计是基于NI-PXI平台来进行的,其硬件实物图如下图所示,两块FPGA板卡连接射频适配器置于机箱中,该平台主要包含机箱、控制器、FPGA模块、射频收发模块四个部分,各模块的性能及主要功能如下:

图1、系统硬件平台实物图

(1)NI PXIe-1082机箱:采用的该机箱包含4个混合插槽, 3个PXI Express插槽, 1个PXI Express系统定时插槽,每插槽高达1 GB/s的专用带宽和7 GB/s的系统带宽,与PXI、PXI Express、CompactPCI和CompactPCI Express模块兼容。机箱主要为控制器和各模块提供了电源、冷却以及PCI和PCI Express通信总线,此外还提供了一系列的I/O模块插槽类型、集成外设。

(2)NI PXIe-8115控制器:本系统采用NI PXI-8115作为控制器,位于机箱最左侧插槽。它是基于Intel Core i5-2510E处理器的高性能嵌入式控制器,适用于PXI系统。具有2.5 GHz基频、3.1 GHz(单核Turbo Boost模式)双核处理器和单通道1333 MHz DDR3内存,配有以太网、串口等标准设备,可自行选择操作系统,本设计选用了Windows系统。

(3)NI PXIe-7966R:针对无线局域网的数据传输,主要考虑数据的运算处理能力,选用FlexRIO模块。它包含两个主要部分:FPGA模块和提供高性能模拟和数字I/O的FlexRIO适配器模块。这些都可以被LabVIEW FPGA软件配置。

其中FPGA模块选用NI PXIe-7966R,它包含了一块Virtex-5 SX95T FPGA和512 MB的板载DDR2双端口RAM。这块FPGA包含了640 DSP slices,可以用它来实现信号处理,数字滤波,FFT逻辑等。另外,板载的双端口RAM理论吞吐量为3.2GB/s。PXIe-7966R支持高性能的P2P数据流传输。本系统中FPGA模块主要实现发射端、接收端的基带数据处理工作。

(4)NI 5791射频适配器: NI 5791是一款具有200 MHz到4.4 GHz连续频率覆盖范围的RF收发器,其中TX和RX端均具有100 MHz的瞬时带宽。它具有单级转向架构,在NI FlexRIO适配器模块的小巧组成结构中提供了超高的带宽。板载合成器(本地振荡器)用于设定采集和生成的中心频率,且可导出至其他模块,以实现多输入多输出(MIMO)同步。用户可直接访问NI FlexRIO FPGA模块的原始ADC和DAC数据。 此外,NI FlexRIO FPGA模块和PXI平台提供了一种实现通道扩展必需的ADC和DAC数据同步方法。

3.3、系统设计

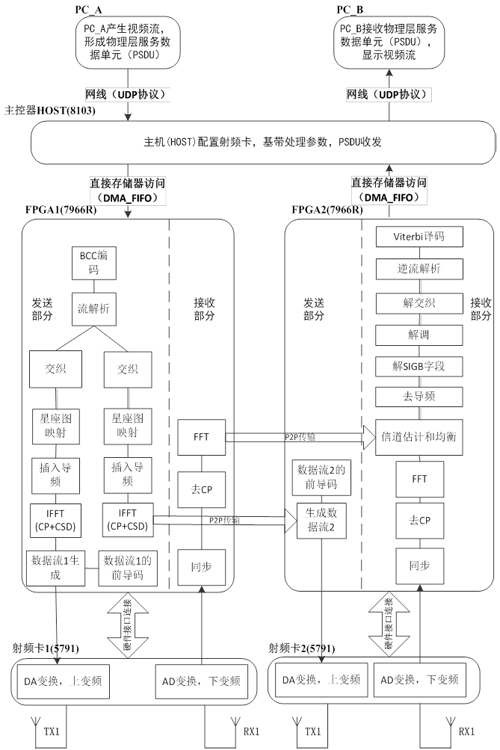

在这样一个实时高速传输系统里,系统架构设计尤为重要,良好的架构设计是系统正确运行的前提,也是提高系统性能的关键所在,本文原型机整个系统的结构框架如图2所示,系统设计主要分为PC端设计、HOST端设计、FPGA端设计三个部分,PC端设计基于C#语言实现视频的编解码等工作,而HOST端和FPGA端设计主要是基于LabVIEW编程实现,前者负责参数配置、数据传输等工作,后者负责实现IEEE 802.11ac协议的物理层模块。这三者之间也要进行数据同步。下文将对各个部分的设计进行详细的叙述。

图2、系统总体架构图

3.3.1、物理层数据通信

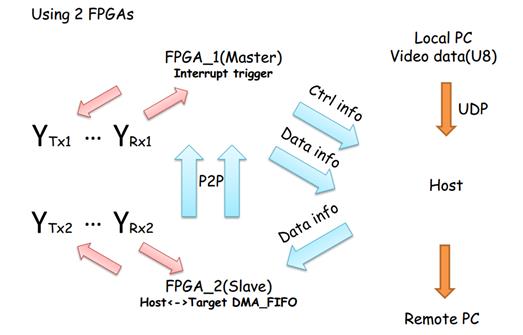

原型机物理层数据通信主要在PC端、HOST端和FPGA端之间进行,其流向如图3所示。系统发送端采用两路数据流形式,因此需要两块FPGA进行数据的生成并与发送射频天线进行对接。为完成无线数据的传输,系统架构中还配有数据发送用户Local_PC以及数据接收用户Remote_PC,另外还有一台控制器Host作为中间载体,对数据的基带收发处理进行LabVIEW算法开发。假设传送的数据为视频流。首先,发送端Local_PC将视频流数据封装成U8格式并打包,FPGA1产生中断向Host请求数据,Host得到该中断请求后,向Local_PC产生新的中断,以请求封装好的数据。Local_PC等待中断请求到来,即向Host发送U8数据包。Host获得U8 数据后会响应FPGA1的中断,通过DMA_FIFO向FPGA2发送数据。FPGA2完成发送端基带处理过程中的各模块操作,形成两路数据流。其中一路数据流通过P2P机制传送给FPGA1。两路数据流通过硬件接口发送至射频卡中,在射频卡中对数据流进行射频信号处理并通过发送天线发出;接收信号经过射频卡传送至两块FPGA中,将FPGA2中的数据通过P2P传送至FPGA1中,在FPGA1中完成后续基带接收过程,将处理完的比特流通过DMA_FIFO传回Host,Host将数据传给Remote_PC,在Remote_PC中显示视频流。

图3、原型机物理层数据流向图

3.3.2、HOST端设计

在此系统设计中,HOST端是连接PC,FPGA,射频卡的重要纽带。其主要完成工作为:

a.完成对PC端视频流的收发,这部分通过网线利用UDP协议,在这方面LabVIEW具有成熟的设计,调用并配置IP地址,包长参数等等。对于接收到的数据,考虑到Viterbi设计时的咬尾操作,必须对数据包进行补零,利用数组转换等设计完成,同样对于发送给PC端的比特流,需要进行去尾操作。

b.完成基带参数的传递及DMA_FIFO的建立。需要考虑的基带参数有:调制方式,每一帧的长度,Viterbi每个Block的长度。DMA_FIFO建立了两个:HOST端的比特流传递给FPGA(HOST to Target),FPGA端的解出的比特流传递给HOST端(Target to HOST)。

c.完成射频参数的传递,主要包含带宽的选择,载波频率的选择,直流偏置修复参数,发送功率值,放大器增益设置等。

d.还需完成两块FPGA板卡间数据传输及同步配置等问题,这一部分在FPGA设计中作详细讨论。

e.完成自动增益控制(AGC)和自适应调制(AMC)功能模块。

下面详细讨论一下HOST端主要功能模块的实现。

(1)视频流收发配置

PC与HOST之间的通信是通过UDP协议完成的。UDP有连接简单,速度快的特点,只要保证发送端PC、NI-PXI的主控器、接收端PC三者都连接在同一个局域网内,即可利用UDP实现数据的高速通信。

HOST具体设置如下:发送端PC将本机IP地址设为回送地址192.168.1.7,目的IP地址设为HOST的实际地址,目的设备端口号设为12270。此外还需设置一个接收HOST发来的数据请求中断的端口号,设其为2000;接收端PC将本机IP地址和远程设备IP地址均设为实际地址,再定义一个接收远程数据的端口号12271。这样就可以利用Socket套接字进行UDP数据的发送和传输了。

(2)自适应调制(AMC)方案

尽管高阶调制、高编码速率可以使频谱效率提高,但这对通信系统的信噪比参数提出了较为严格的要求,如果噪声能量达到一定程度会造成系统误码率上升,误码性能大大下降,从而降低了系统的吞吐量。为确保系统的有效吞吐性能,当信噪比较低时,应选择低阶调制方式与编码速率,当信噪比较高时,可以选择高阶调制方式与编码速率。因此,设计采用自适应调制(AMC)技术,在发射功率恒定的情况下,通过调整无线链路传输的调制方式与编码速率确保链路的传输质量。

实现AMC的过程需要稳定的信号功率,这需要引入自动增益控制(AGC)技术以确保信号能量的稳定性。在AGC的工作过程中,初始化功率p0让射频放大器得到初始化的放大系数,对于接收端来说,需要设置一个预期能量pref,用来确定AGC过程趋于稳定时信号的能量。在通信过程中,当信道环境发生变化时,接收信号的能量pr会不断发生变化,调整功率参数pd也会随之变化(pd是一个负值参数,用于控制射频放大系数)。接收信号能量降低时,接收天线的射频放大器会提高放大系数,接收信号能量提高时,接收天线的射频放大器会降低放大系数,这样使得信号能量维持在预期能量pref附近。在通信过程的开始,调整功率参数pd可以任意设置。AGC过程中调整功率参数pd(对数形式)满足公式(1),其中pd_new为pd的更新值。

(1)

(1)

考虑采用BCC信道编码方式的单用户MIMO2×2系统,固定BCC编码速率为1/2,一种简单的AMC设置方案如下表所示,表中pd所在区间是在NI-PXI平台上使用NI-5791射频适配模块进行测试的一组参考区间,此时对应的预期能量pref = -8dBm。

表1、AMC调制方式与调整功率参数pd的关系

| pd所在区间(dB) | 选择调制方式 |

| (-27,-18) | BPSK |

| (-18,-12) | QPSK |

| (-12,-8) | 16QAM |

| (-8,-5.5) | 64QAM |

| (-5.5,-4) | 256QAM |

3.3.3、FPGA端设计

FPGA的设计比较复杂,也是数据处理部分的核心,这一部分主要完成基带信号处理的关键工作,此外还负责射频卡5791的配置、P2P传输、FPGA间同步设计。

(1)射频卡5791配置

射频卡的配置在FPGA中完成,主要完成将HOST传递过来的参数写入射频卡相应寄存器里,尤其是关于速率的小数变换。

系统基带数据带宽为20MHz,而AD/DA端采样速率为130MHz,为了完成速率的匹配,必须对基带数据作相应处理。对于发送端,通过插值处理将20MHz升至130MHz,实现方式为每隔130/20=6.5个时钟周期从基带数据FIFO中读出数据,并进行扩展,形成130MHz的发送信号;类似的,接收端通过抽取方式实现130MHz降至20MHz,实现方式为每隔6.5个时钟将接收到的数据写入基带处理FIFO中。

(2)P2P传输

P2P将两块FPGA的数据合并到一块FPGA中,并在一块FPGA中完成后续的MIMO基带处理,因此在本系统中,P2P是实现MIMO的重要纽带。

P2P的配置主要包含两方面,在主机(HOST)端将一块FPGA的写入数据流和另一块FPGA的读取连接起来,在FPGA端,P2P数据读取和写入节点为数据交换提供FIFO的接口,这样的接口类似于DMA和本地FPGA 的FIFO,如图4所示。

P2P HOST端配置

P2P FPGA端配置

图4 、P2P配置

(3)FPGA间同步设计

出于硬件平台的局限性,两根发射天线由两块FPGA分别连接,这样的硬件架构带来的问题就是如何保证两根天线发出数据的同步性。这是任何一个设备平台都需要考虑的问题,各个厂家也提供了不同的方案,NI利用其独特的模块化设计,FPGA之间存在trigger总线连接,利用trigger触发实现同步。

当不同的设备之间共享triggers时,信号路径的传播延时会造成trigger到达设备的时间不同步。NI自带的同步库可以利用CPTR(同周期时间相关)减缓trigger的评估速率。关键是所有的设备都必须构建一个CPTR信号,这些CPTR信号之间同频同相。

FPGA端的同步程序构建和关联CPTR信号,这些CPTR信号在不同的FPGA间是同时产生的。CPTR信号是周期性的,采样周期可以控制CPTR的周期。

(4)基带信号处理设计

在基于IEEE802.11ac协议的系统中,发送端包括前导码生成、信道编码、流解析、比特交织、星座映射、插入导频、添加CP、引入CSD以及IFFT转换等过程;接收端包括时间同步、FFT转换、去除CP、信道估计、信号均衡、去除导频、解映射、比特解交织、逆流解析、信道解码等过程。一些主要模块的具体细节如下:

a.BCC编码

采用IP核实现802.11ac标准规定的BCC编码器,其生成多项是g0=133(8)和g1=171(8),分别对应于生成多项式S0(x) = x6 + x5 + x3 + x2 + 1和S1(x) = x6 + x3 + x2 + x1 + 1,可以使用移位寄存器来实现。卷积编码后的两路输出相互合并再进行后续传输。根据不同的规则进行删余打孔,BCC信道编码器支持1/2、2/3、3/4、5/6四种编码速率,以满足更高的传输效率。

b.流解析与逆流解析

在经过信道编码后,流解析将编码比特被重新排成一组新的、等于空间流数(NSS)的比特串。其输出为NSS路并行比特序列,每个串的长度为NCBPSS (每空间流编码比特)。

逆流解析时流解析的逆过程,主要完成两个数据流合并成一个流的过程。

c.调制与解调

星座映射过程是把比特序列以一定的方式映射到星座图中的一个复数星座点。IEEE802.11ac支持的映射(调制)方式包括BPSK、QPSK、16QAM、64QAM和256QAM,各调制方式下每个子载波的复数星座点分别承载1、2、4、8和16个比特的信息,也即调制阶数NBPSCS。前导码字段中的信令字段均采用BPSK调制。生成数据字段时,根据信令字段中的MCS信息,子载波选择相应的映射(调制)方式。在20MHz带宽下,每个OFDM码元是由52个有效的复数星座值组成;4MHz带宽时这个有效值为108个。

解调是星座映射调制的逆过程,以恢复传输传输。

d.IFFT与FFT

实现发射端频域数据到时域数据的转换,同理,FFT则实现了接收端时域数据到频域数据的转换,以用于后续处理。

e.同步

在基于IEEE802.11ac协议的接收机中,同步过程主要包括时间同步,载波频率同步和采样时钟同步。由于NI-PXI平台具有优良的集成工艺和精密性,收发机的本振频率几乎一致,采样时钟也几乎保持完全相同,因此在原型机系统设计中可以暂时忽略系统的载波频率偏差和采样时钟偏差带来的影响。因此本文原型机的接收端采用基于前导码训练序列的MIMO-OFDM系统时间同步方案。

时间同步的处理主要分为捕获和跟踪两个阶段,具体分为帧同步过程和符号同步过程。帧同步又称作粗时间同步,用于检测数据分组的到来,这是时间同步的捕获阶段;符号同步又称作精时间同步,用于精确定位OFDM符号数据的起始位置,这是时间同步的跟踪阶段。

f.信道估计与均衡

信道估计是获取信道信息的重要模块,利用估计出的信道响应可以对接收端数据进行信道均衡操作从而恢复数据。IEEE802.11ac协议的信道估计采用定期发送训练序列的方法,即利用前导码中VHT-LTF的若干字段在频域内进行信道估计。信道均衡则是对接收信号进行一定的补偿操作,即对信号进行恢复与提取,为后续的解调和信道解码过程打下基础。利用之前得到的估计信道进行信道均衡过程,可以减轻或消除码间干扰,使得系统能够对抗无线信道衰落,从而提高无线系统的数据传输速率和频谱效率。本原型机采用基于LS算法的信道估计和基于ZF算法的信道均衡。

g.维特比译码

本系统中采用Xilinx的IP Core实现Viterbi译码,其输入采用基于帧形式的传输方式,需要重点考虑的是咬尾问题。因此需要在每一帧的最后添加6个零,使译码器回到初始状态。

3.3.4、PC端设计

PC端主要完成视频流的编码打包,并加上CRC校验码,同时根据不同调制方式改变发送数据包的大小。之所以选择用两台PC分别处理视频流的收发,是因为考虑到LabVIEW对视频流处理能力的薄弱,如果采用HOST端作视频流的编解码,这会耗用大量的CPU资源。因此NI仪器完全用来处理数据比特部分,而视频流的一系列处理则用C#编写的代码进行。

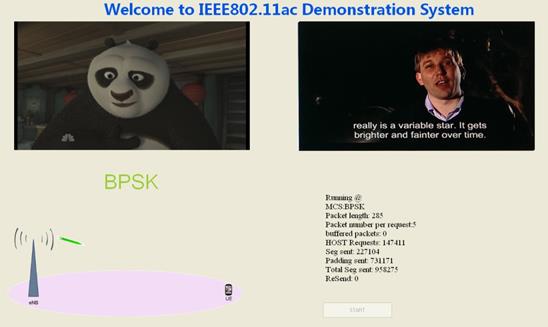

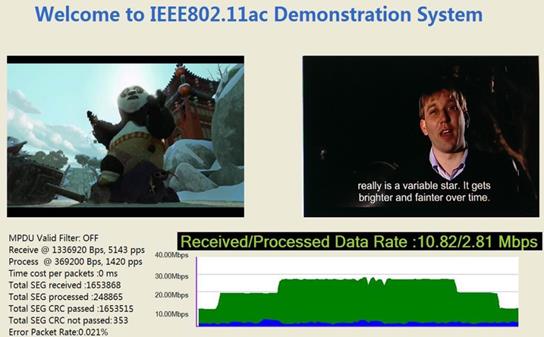

视频数据发送用户和接收用户的用户界面如图5、图6所示。发送用户界面中可以显示发送的视频,当前采取的调制方式MCS,包长的大小,每次请求包的数目(不同调制方式请求的包数不同),HOST中断请求次数等参数。而接收用户界面中可以显示接收到的视频,传输速率、接收到包的总数,误包率等参数。最主要的参数是Received Data Rate和Processed Data Rate。Processed Data Rate为传输的有效数据,也即实际视频流传输数据速率。由于视频流的包比较小,在其中添加了冗余信息来形成完整的包,Received Data Rate表示这种完整包的传输速率,也即物理层传输的数据速率。

图5、PC端发送用户界面

图6、PC端接收用户界面

4、基于NI-PXI的11ac原型机系统演示

关于原型系统的演示,分别从接收星座图演示以及视频流传输两个角度进行分析,以便更好地测试系统的性能。

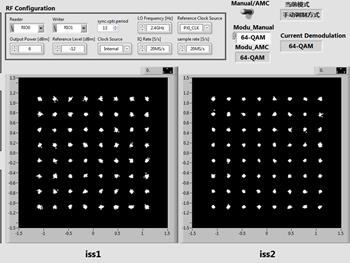

4.1、接收星座图演示

接收星座图演示过程中,可以无需发送端和接收端的PC外设。主控器Host可以随机产生固定OFDM符号数的U8型数据流,并将U8型数据送入FPGA中,通过基带处理和射频收发等一系列过程,Host将接收天线得到的信号通过FFT操作转换到频域后进行输出,观察频域接收数据的星座图变化。在测试中,Host需要实现AGC功能,使得天线自由移动时,接收端仍然能够实现精确的时间同步过程。根据是否采用AMC方案,可以将接收星座图测试分为手动模式和自适应模式两种。手动模式下,无论接收信号强度与信道环境如何,都采取手动设置发送端的星座映射方式,这种模式可以观察固定的星座映射方式下不同天线环境对接收星座图的影响;自适应模式下,采用AMC方案,即系统根据当前的信道环境自动设置理想的星座映射方式,使得数据传输的速率和误码性能达到同时较优的状态。

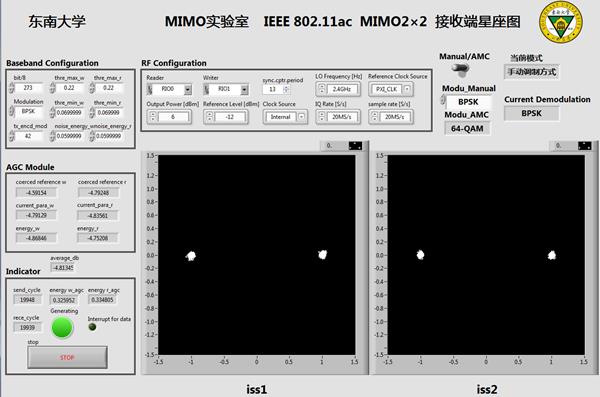

下图反映了MIMO2×2系统在手动模式下,发送端分别采用BPSK映射方式的接收星座图结果。手动模式下,可以通过调整天线的位置与间距改善传输信道环境,使得各映射方式下的接收星座图都能达到准确清晰的水平。

图7、BPSK接收星座图(手动模式)

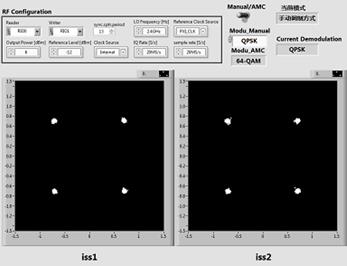

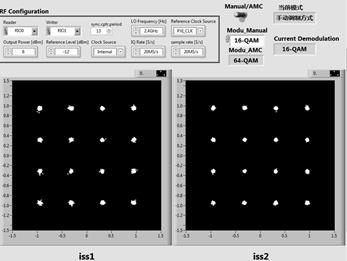

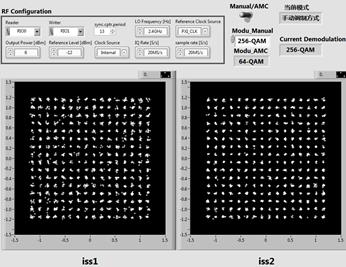

图8给出了其他几种调制方式的星座图结果,从左到右从上到下依次为QPSK、16-QAM、64-QAM和256QAM映射方式。

QPSK接收星座图

16QAM接收星座图

64QAM接收星座图

256QAM接收星座图

图8、各种调制方式接收星座图(手动模式)

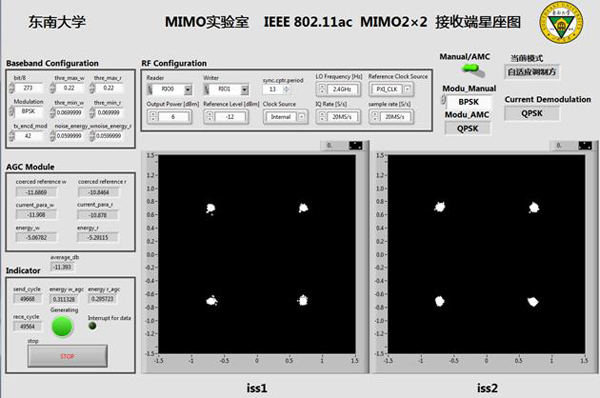

下图9反映了自适应模式下的接收星座图结果,此时自适应调试方式为QPSK。自适应模式下,改变天线的位置与间距意味着信道环境发生变化,系统自动给出一种既保证传输质量又具有尽可能高吞吐率的数据传输方案。

图9、QPSK接收星座图(自适应模式)

4.2、视频流实时传输

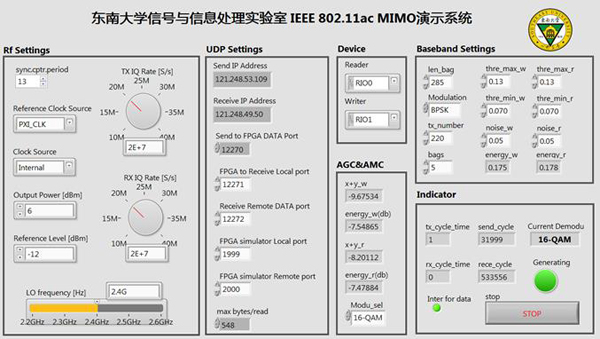

图10显示了在NI-PXI平台上原型系统Host控制器的前面板设计,其主要实现了射频卡、UDP协议、FPGA设备同步、基带参数以及AGC模块等功能设置过程。

图10、原型系统Host控制器的前面板框图

PC端发射、接收用户界面已在3.3.4节通过图5、图6给出。

图11展示了基于NI-PXI平台的IEEE 802.11ac MIMO2×2演示系统,图中右侧PC产生包含两路视频流的数据源信息,通过UDP协议可以将数据源传输到NI-PXI控制器Host中。Host将数据传输到FPGA中生成时域OFDM符号,通过射频卡以无线方式发送并接收数据,接收到的数据送入FPGA做接收端处理,从而恢复出视频数据并传回到Host中,再次通过UDP协议将恢复的视频数据传给图中左侧PC,并对视频数据进行实时显示。

其中,发送端采用BCC信道编码方式,码率固定为1/2。在不同的映射方式下,发送数据帧具有相同的OFDM符号个数,这会使得高阶映射方式下的吞吐率高于低阶映射方式下的吞吐率。

图11、IEEE802.11ac MIMO2×2演示系统

IEEE802.11ac的MIMO2×2原型系统的实际工作速率如表2所示。从表中可以看出,由于硬件实现时存在硬件性能的限制以及各类微小的偏差,系统实际的传输作速率并不能达到理论值,但已经非常接近理论值。同时,当采用高阶的星座映射方式进行传输时,实际物理层传输速率逐渐受限,数据吞吐量不能正常翻倍,这是因为采用高阶映射方式时,控制器Host需要在相同时间内处理更多的数据包,当Host处理能力达到极限时,实际的传输带宽不能充分利用,因此传输的吞吐量不能按照预期进行提升。如果采用256QAM映射方式,在相同时间内进行与低阶映射方式具有相同OFDM发送符号数的传输过程,系统将不能正常工作,这是由于原型系统所需的时钟速率达到控制器Host的工作极限,因而无法支持256QAM进行正常的物理层传输。同时,256QAM正常工作所需的接收信噪比要求也较高,在接收星座图测试中可以看出该映射方式下的星座点性能不甚理想。

表2、原型系统在各映射方式下的传输速率

| 映射方式 | BPSK | QPSK | 16QAM | 64QAM |

| 理论工作速率 | 13.0M/s | 26.0M/s | 52.0M/s | 78.0M/s |

| 实际工作速率 | 11.2M/s | 22.4M/s | 44.8M/s | 46.7M/s |

5、结论

该系统方案利用NI的PXI平台及NI的LabVIEW软件平台进行研发,使我们能专注于802.11ac协议的实现,缩短了研发周期。LabVIEW图形化的编程语言以及提供的IP接口也为开发者提供了不少的便利。系统的核心运算都在高速的FPGA模块内完成,能满足原型机设计目标的高速要求。整个系统的测试结果在上一章有详细叙述,能正确显示接收数据在不同调制方式下的星座图,系统工作速率也能达到要求,能高质量的进行视频流的传输。我们的原型机只是阶段性的成果,还有更进一步的空间,如将基带带宽拓展到40MHz、扩展到4×4的MIMO系统以及开展毫米波的研究。

6、参考文献

1] Perahia E, Gong M X. Gigabit wireless LANs: an overview of IEEE 802.11 ac and 802.11 ad [J]. ACM SIGMOBILE Mobile Computing and Communications Review, 2011, 15(3): 23-33.2] IEEE 802.11 Working Group. IEEE Standard for Information Technology–Telecommunications and information exchange between systems–Local and metropolitan area networks–Specific requirements–Part 11: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) specifications Amendment 6: Wireless Access in Vehicular Environments [J]. IEEE Std, 2010, 802: 11p.

3] Eldad Perahia, Robert Stacey. 下一代无线局域网802.11n的吞吐率、强健性和可靠性[M]. 罗训,赵利,译. 北京:人民邮电出版社, 2010.

4] Foschini G J, Gans M J. On limits of wireless communications in a fading environment when using multiple antennas [J]. Wireless personal communications, 1998, 6(3): 311-335.

5] Jiang M, Hanzo L. Multiuser MIMO-OFDM for next-generation wireless systems [J]. Proceedings of the IEEE, 2007, 95(7): 1430-1469.

6] Bolcskei H. MIMO-OFDM wireless systems: basics, perspectives, and challenges [J]. IEEE Wireless Communications, 2006, 13(4): 31-37.

7] Breit G, Sampath H, Vermani S. TGac channel model addendum [J]. Institute of Electronic, 2010.

8] "802.11 Amendment 5: Enhancements for Very High Throughput for Operation in Bands below 6 GHz"[S]. IEEE P802.11ac D1.4, Nov. 2011.

9] 刘凯明. OFDM 系统中的自适应调制技术研究[D]. 北京: 北京邮电大学, 2006.

10] Pham T H, McLoughlin I V, Fahmy S A. Robust and efficient OFDM synchronization for FPGA-based radios [J]. Circuits, Systems, and Signal Processing, 2014, 33(8): 2475-2493.

11] 史治国, 洪少华, 陈抗生. 基于XILINX FPGA 的OFDM 通信系统基带设计[M]. 浙江大学出版社, 2009.

12] Nguyen M D, Nguyen V T, Nguyen T D, et al. FPGA implementation of the synchronization for IEEE 802.11 n WLAN systems [C]. IEEE Fifth International Conference on Communications and Electronics, 2014: 280-284.

13] Wang K, Singh J, Faulkner M. FPGA implementation of an OFDM-WLAN synchronizer [C]. IEEE International Conference on Field-Programmable Technology, 2004: 89-94.

14] Wubben D, Bohnke R, Kuhn V, et al. Near-maximum-likelihood detection of MIMO systems using MMSE-based lattice reduction [C]. IEEE International Conference on Communications, 2004, 2: 798-802.

15] Kaur J, Singh M. Performance analysis of various channel estimation techniques for higher order modulation in a MIMO system [J]. International Journal of Engineering and Innovative Technology, 2012, 2(2).

16] Wubben D, Bohnke R, Kuhn V, et al. MMSE extension of V-BLAST based on sorted QR decomposition [C]. IEEE 58th Vehicular technology conference, 2003, 1: 508-512.

17] Lal M, Arora H. BER performance of different modulation schemes for MIMO systems [J]. International Journal of Computer Science and Network Security, 2011, 11(3): 69-73.

18] Guide U. January. “Virtex-5 FPGA XtremeDSP Design Considerations,” Version 3.3, Xilinx Inc [J]. 2009.

19] National Instruments. USER MANUAL AND SPECIFICATIONS NI 5791R Transceiver Adapter Module [EB/OL]. www.ni.com.

粤公网安备 44030902003195号

粤公网安备 44030902003195号