йқўеҗ‘5GжҜ«зұіжіўйҖҡдҝЎзі»з»ҹзҡ„жң¬жҢҜжәҗи®ҫи®ЎдёҺе®һзҺ°

ж‘ҳиҰҒпјҡй’ҲеҜ№5G жҜ«зұіжіўйҖҡдҝЎзі»з»ҹеҜ№жң¬жҢҜжәҗйў‘зҺҮгҖҒзӣёдҪҚеҷӘеЈ°гҖҒжқӮж•ЈжҠ‘еҲ¶иҰҒжұӮзҡ„жҸҗеҚҮпјҢжҸҗеҮәдәҶдёҖз§Қз»“еҗҲADF4002 е’Ң2 дёӘADF5355 йў‘зҺҮеҗҲжҲҗеҷЁиҠҜзүҮпјҢеҸҜеҗҢж—¶з”ЁдәҺдёӯйў‘е’Ңе°„йў‘з”өи·Ҝзҡ„й«ҳжҖ§иғҪжң¬жҢҜжәҗгҖӮиҜҘжң¬жҢҜжәҗдёәзі»з»ҹдёӯйў‘жЁЎеқ—жҸҗдҫӣ5.4 GHz зҡ„еҚ•йҹіжң¬жҢҜдҝЎеҸ·е№¶дё”еҲ©з”Ёж•°жҺ§иЎ°еҮҸеҷЁе’Ңж”ҫеӨ§еҷЁе®һзҺ°дәҶиҫ“еҮәеҠҹзҺҮеҸҜи°ғпјҢеҗҢж—¶д№ҹеҲ©з”ЁADF5355 зҡ„й”ҒзӣёзҺҜпјҲPLLпјүе’ҢеҖҚйў‘еҷЁдёәе°„йў‘жЁЎеқ—жҸҗдҫӣ8.4пҪһ11.2 GHz е®Ҫйў‘еёҰе®ҪгҖҒжӯҘиҝӣдёә100 MHz зҡ„еҸҜи°ғйў‘жң¬жҢҜдҝЎеҸ·пјҢжңҖз»ҲйҖҡиҝҮ硬件з”өи·Ҝзҡ„и®ҫи®ЎдёҺи°ғиҜ•пјҢд»ҘеҸҠеҚ•зүҮжңәпјҲSCMпјүжҺ§еҲ¶зЁӢеәҸзҡ„зј–еҶҷпјҢе®һзҺ°дәҶдҪҺзӣёеҷӘгҖҒдҪҺжқӮж•Јзҡ„зЁіе®ҡйў‘зҺҮжәҗгҖӮ

е…ій”®иҜҚпјҡеӨ§и§„жЁЎеӨҡиҫ“е…ҘеӨҡиҫ“еҮәпјҲMIMOпјүпјӣжң¬жҢҜпјӣй”ҒзӣёзҺҜпјӣдҪҺзӣёдҪҚеҷӘеЈ°пјӣйў‘зҺҮеҸҜи°ғ

еңЁ5G жҜ«зұіжіўйҖҡдҝЎзі»з»ҹдёӯпјҢеӨ§и§„жЁЎеӨҡиҫ“е…ҘеӨҡиҫ“еҮәпјҲMIMOпјүжҠҖжңҜиў«з”ЁжқҘеӨ§е№…еәҰжҸҗй«ҳж•°жҚ®дј иҫ“йҖҹзҺҮе’ҢдҝЎйҒ“е®№йҮҸгҖӮеӨ§и§„жЁЎMIMO жҠҖжңҜд№ҹжҳҜ5GеҢәеҲ«дәҺзҺ°жңүзі»з»ҹзҡ„ж ёеҝғжҠҖжңҜд№ӢдёҖ[1]гҖӮеңЁеӨ§и§„жЁЎMIMO еңәжҷҜдёӢпјҢйҖҡиҝҮеҹәз«ҷй…ҚзҪ®ж•°зҷҫж №еӨ©зәҝпјҢеҸҜд»ҘдҪҝеӨ§йҮҸзҡ„з»Ҳз«Ҝз”ЁжҲ·дҪҝз”ЁеҗҢдёҖдёӘж—¶йў‘иө„жәҗпјҢеӣ жӯӨзі»з»ҹдёӯеҗҢж—¶еӯҳеңЁеӨҡи·Ҝ射频收еҸ‘дҝЎйҒ“пјҢд№ҹе°ұйңҖиҰҒеӨҡи·Ҝжң¬жҢҜдҝЎеҸ·гҖӮжң¬жҢҜзҡ„з ”з©¶жҳҜжҜ«зұіжіўйҖҡдҝЎзі»з»ҹз ”з©¶зҡ„е…ій”®д№ӢдёҖ[2]гҖӮ

жң¬жҢҜжЁЎеқ—дёҺ收еҸ‘зі»з»ҹзӣёдә’зӢ¬з«ӢеҸҜд»Ҙжңүж•Ҳең°жҠ‘еҲ¶жң¬жҢҜжі„йңІе’Ңе°„йў‘дёІжү°зӯүй—®йўҳпјҢеҮҸ少收еҸ‘зі»з»ҹеҚ°еҲ¶з”өи·ҜжқҝпјҲPCBпјүзүҲзҡ„йқўз§ҜпјҢ并且еҸҜд»ҘдҪҝжҜҸдёӘжЁЎеқ—жӣҙзҒөжҙ»пјҢдҫҝдәҺи°ғиҜ•е’ҢеҗҺжңҹз»ҙжҠӨгҖӮз»јеҗҲиҖғиҷ‘зі»з»ҹжҖ§иғҪе’ҢжҲҗжң¬зӯүж–№йқўзҡ„еӣ зҙ пјҢйҮҮз”ЁеӨ–зҪ®жң¬жҢҜжҳҜзҺ°д»Јз§»еҠЁйҖҡдҝЎзі»з»ҹдёӯеёёи§Ғзҡ„йҖүжӢ©[2-3]гҖӮ

1гҖҒжң¬жҢҜзі»з»ҹи®ҫи®Ў

йў‘зҺҮеҗҲжҲҗжҠҖжңҜдё»иҰҒеҲҶдёәзӣҙжҺҘеҗҲжҲҗжҠҖжңҜдёҺй—ҙжҺҘеҗҲжҲҗжҠҖжңҜгҖӮзӣҙжҺҘеҗҲжҲҗжҠҖжңҜеҸҲеҢ…жӢ¬зӣҙжҺҘжЁЎжӢҹеҗҲжҲҗжҠҖжңҜдёҺзӣҙжҺҘж•°еӯ—еҗҲжҲҗжҠҖжңҜпјҲDDSпјүгҖӮзӣҙжҺҘжЁЎжӢҹеҗҲжҲҗжҠҖжңҜжҳҜжңҖж—©жңҹзҡ„йў‘зҺҮеҗҲжҲҗжҠҖжңҜпјҢе…¶йҖҡиҝҮдёҖзі»еҲ—зҡ„жЁЎжӢҹеҷЁд»¶иҝӣиЎҢеҖҚйў‘гҖҒж··йў‘гҖҒеҲҶйў‘зӯүз®—жңҜиҝҗз®—д»ҺиҖҢеҗҲжҲҗеӣәе®ҡйў‘зҺҮпјҢеҶҚеҲ©з”ЁзӘ„еёҰж»ӨжіўеҷЁж»ӨеҮәжүҖйңҖйў‘зҺҮгҖӮеңЁиҝҷз§Қж–№ејҸдёӢеҸӮиҖғдҝЎеҸ·зҡ„зӣёдҪҚеҷӘеЈ°зӣҙжҺҘеҶіе®ҡдәҶиҫ“еҮәдҝЎеҸ·зҡ„зӣёеҷӘпјҢеӣ жӯӨе®№жҳ“иҺ·еҫ—зӣёеҷӘеҫҲдҪҺзҡ„иҫ“еҮәдҝЎеҸ·пјҢдҪҶжҳҜиҝҷз§Қз”өи·Ҝзҡ„е®һзҺ°йңҖиҰҒеӨ§йҮҸзҡ„жЁЎжӢҹеҷЁд»¶з»„еҗҲпјҢйӣҶжҲҗеәҰдҪҺпјҢдҪ“з§ҜеӨ§пјҢжқӮж•ЈжҠ‘еҲ¶иҫғе·®пјҢжҲҗжң¬й«ҳжҳӮпјҢзӣ®еүҚиҜҘз§ҚжҠҖжңҜдё»иҰҒз”ЁдәҺе°„йў‘еҫ®жіўжөӢиҜ•жөӢйҮҸд»ӘеҷЁдёӯгҖӮ

зӣҙжҺҘж•°еӯ—еҗҲжҲҗжҠҖжңҜзҡ„зү№зӮ№жҳҜйҖҡиҝҮж•°еӯ—ж–№ејҸзҙҜеҠ зӣёдҪҚпјҢеҶҚеҲ©з”ЁзӣёдҪҚе’ҢеҺ»жҹҘиҜўжӯЈејҰеҮҪж•°иЎЁд»ҺиҖҢеҫ—еҲ°жӯЈејҰжіўзҡ„зҰ»ж•Јж•°еӯ—зі»еҲ—пјҢжңҖз»Ҳз»ҸиҝҮж•°жЁЎпјҲD/AпјүиҪ¬жҚўеҫ—еҲ°жЁЎжӢҹжӯЈејҰжіўгҖӮDDS е…·жңүйў‘зӮ№иҪ¬жҚўйҖҹзҺҮеҝ«гҖҒйў‘зҺҮеҲҶиҫЁзҺҮй«ҳзҡ„дјҳзӮ№пјҢдёҚиҝҮз”ұдәҺиҫ“еҮәйў‘зҺҮжқӮж•ЈеҫҲеӨҡпјҢиҫ“еҮәйў‘зҺҮиҫғдҪҺпјҢдҪҝе…¶дҪҝз”ЁиҢғеӣҙеҸ—йҷҗ[4]гҖӮ

й—ҙжҺҘйў‘зҺҮеҗҲжҲҗжҠҖжңҜеҚідёәй”ҒзӣёзҺҜејҸйў‘зҺҮеҗҲжҲҗжҠҖжңҜпјҲPLLпјүпјҢе®ғдё»иҰҒжҳҜйҖҡиҝҮзӣёдҪҚиҙҹеҸҚйҰҲзҡ„ж–№ејҸжқҘе®һзҺ°еҜ№дёӨи·ҜдҝЎеҸ·зӣёдҪҚзҡ„и·ҹиёӘпјҢд»ҺиҖҢз”Ёй”ҒзӣёзҺҜе°ҶеҺӢжҺ§жҢҜиҚЎеҷЁпјҲVCOпјүзҡ„йў‘зҺҮй”Ғе®ҡеңЁжүҖйңҖиҰҒзҡ„йў‘зӮ№дёҠгҖӮиҜҘз§ҚеҪўејҸз»“жһ„з®ҖеҚ•пјҢзӣёдҪҚеҷӘеЈ°дҪҺпјҢжқӮж•ЈжҠ‘еҲ¶иҫғеҘҪпјҢжҲҗжң¬иҫғдҪҺпјҢдҪҶжҳҜйў‘зҺҮиҪ¬жҚўзҡ„ж—¶й—ҙй•ҝпјҢйў‘зҺҮеҲҶиҫЁзҺҮжҜ”иҫғдҪҺ[5-6]гҖӮ

з»“еҗҲжң¬и®ҫи®ЎдёӯйңҖиҰҒиҫ“еҮәдёӨи·Ҝйў‘зҺҮиҫғй«ҳзҡ„жң¬жҢҜдҝЎеҸ·пјҢ并且其дёӯдёҖи·ҜеёҰе®Ҫиҫғе®Ҫзҡ„зү№зӮ№пјҢз»јеҗҲзӣёдҪҚеҷӘеЈ°гҖҒжқӮж•ЈжҠ‘еҲ¶зӯүеӣ зҙ пјҢеҶіе®ҡйҮҮз”Ёй”ҒзӣёзҺҜйў‘зҺҮеҗҲжҲҗжҠҖжңҜжқҘе®һзҺ°иҜҘжң¬жҢҜжәҗгҖӮ

1.1 ж•ҙдҪ“жЎҶжһ¶

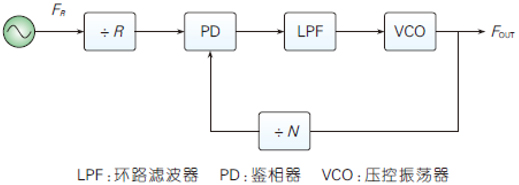

еӣҫ1 жҳҜPLL зҡ„еҹәжң¬з»“жһ„пјҢй”ҒзӣёзҺҜз”өи·Ҝзҡ„з»„жҲҗйғЁеҲҶдё»иҰҒеҢ…жӢ¬еҺӢжҺ§жҢҜиҚЎеҷЁпјҲVCOпјүгҖҒйүҙзӣёеҷЁпјҲPDпјүгҖҒзҺҜи·Ҝж»ӨжіўеҷЁпјҲLPFпјүе’ҢеҲҶйў‘еҷЁ[5]гҖӮ

еӣҫ1гҖҒPLL з»“жһ„жЎҶеӣҫ

еҸӮиҖғжәҗз»ҷеҮәзҡ„иҫ“е…ҘдҝЎеҸ·FR йҖҡиҝҮR еҲҶйў‘еҷЁйҷҚдҪҺдёәйүҙзӣёеҷЁзҡ„жЈҖжөӢйў‘зҺҮFPD пјҢиҖҢVCO зҡ„иҫ“еҮәйў‘зҺҮз»ҸиҝҮN еҲҶйў‘еҷЁеҗҺеҫ—еҲ°иҫ“е…ҘйүҙзӣёеҷЁзҡ„еҸҰдёҖи·ҜдҝЎеҸ·FN пјҢдёӨи·ҜдҝЎеҸ·йҖҡиҝҮйүҙзӣёеҷЁиҝӣиЎҢзӣёдҪҚжҜ”иҫғпјҢе®ғ们дә§з”ҹзҡ„зӣёдҪҚе·®иҪ¬жҚўдёәз”өеҺӢжҲ–з”өжөҒпјҢз»ҸиҝҮдҪҺйҖҡзҡ„зҺҜи·Ҝж»ӨжіўеҷЁпјҲLPFпјүж»ӨйҷӨеҷӘеЈ°е’Ңй«ҳйў‘еҲҶйҮҸеҗҺйҖҒе…ҘVCO з”ЁжқҘжҺ§еҲ¶VCO зҡ„иҫ“еҮәйў‘зҺҮгҖӮеҪ“й”ҒзӣёзҺҜзЁіе®ҡеҗҺпјҢеҚіFPD е’ҢFN еҗҢйў‘еҗҢзӣёзҡ„зҠ¶жҖҒдёӢпјҢй”ҒзӣёзҺҜзҡ„иҫ“еҮәйў‘зҺҮдёәпјҡ

пјҲ1пјү

пјҲ1пјү

зӣёдҪҚеҷӘеЈ°жҳҜиЎЎйҮҸжң¬жҢҜжәҗзҡ„йҮҚиҰҒжҢҮж ҮпјҢ收еҸ‘дҝЎжңәзҡ„и°ғеҲ¶дёҺи§Ји°ғзІҫеәҰпјҲEVMпјүеҸ—зі»з»ҹзҡ„зӣёдҪҚеҷӘеЈ°еҪұе“ҚпјҢиӢҘзӣёдҪҚеҷӘеЈ°иҝҮеӨ§пјҢеҲҷзі»з»ҹи§Ји°ғеҮәзҡ„жҳҹеә§еӣҫдјҡеҮәзҺ°ж—ӢиҪ¬пјҢеӣ жӯӨйҰ–е…ҲиҰҒйҷҚдҪҺжң¬жҢҜжәҗзҡ„зӣёдҪҚеҷӘеЈ°гҖӮеҪұе“ҚзӣёдҪҚеҷӘеЈ°зҡ„еӣ зҙ жңүеҫҲеӨҡпјҢеңЁиҝ‘з«ҜпјҢзӣёдҪҚеҷӘеЈ°дё»иҰҒеҸ–еҶідәҺеҸӮиҖғдҝЎеҸ·гҖҒN еҲҶйў‘еҷЁгҖҒйүҙзӣёеҷЁд»ҘеҸҠз”өжәҗгҖӮйҖҡиҝҮејҸпјҲ2пјүеҸҜд»Ҙдј°з®—еҮәзҺҜи·ҜеёҰе®ҪеҶ…зҡ„зӣёдҪҚеҷӘеЈ°пјҡ

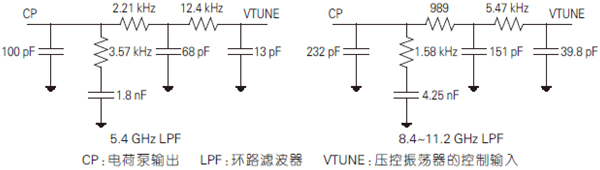

PN = PNfloor + 10log(N) + 10log( fvco )пјҲ2пјү

еңЁиҫ“еҮәйў‘зҺҮдёҚеҸҳзҡ„жғ…еҶөдёӢпјҢйҷҚдҪҺеҲҶйў‘жҜ”N еҸҜд»Ҙж”№е–„зӣёдҪҚеҷӘеЈ°гҖӮдёҖиҲ¬жқҘиҜҙпјҢжң¬жҢҜзі»з»ҹзҡ„еҸӮиҖғжәҗжҳҜе…Ёзҗғе®ҡдҪҚзі»з»ҹпјҲGPSпјүдёӢиЎҢзҡ„10 MHz[5]гҖӮз”ұдәҺеңЁжӯӨи®ҫи®ЎдёӯйңҖиҰҒиҫғй«ҳзҡ„иҫ“еҮәйў‘зҺҮпјҢдёәдәҶиҺ·еҫ—иүҜеҘҪзҡ„зӣёдҪҚеҷӘеЈ°пјҢж•…йҖүжӢ©жҸҗеҚҮеҸӮиҖғйў‘зҺҮгҖӮеңЁж•ҙдёӘзі»з»ҹеүҚз«Ҝе…Ҳи®ҫи®ЎдёҖдёӘй”ҒзӣёзҺҜз”өи·ҜпјҢе°Ҷ10 MHz еҸӮиҖғдҝЎеҸ·жҸҗй«ҳиҮі100 MHzгҖӮз”ұејҸпјҲ2пјүеҸҜзҹҘпјҡзі»з»ҹзҡ„зӣёдҪҚеҷӘеЈ°е°ҶдјҡйҷҚдҪҺ10 dBпјӣиҖҢеңЁзҺҜи·ҜеёҰе®ҪеӨ–пјҢзӣёдҪҚеҷӘеЈ°дё»иҰҒеҸ—VCO еҪұе“ҚгҖӮдёәдәҶеҫ—еҲ°жӣҙеҘҪзҡ„йў‘зҺҮзЁіе®ҡеәҰе’ҢзӣёдҪҚеҷӘеЈ°пјҢжң¬и®ҫи®Ўдёӯз”Ё100 MHz зҡ„жҒ’жё©жҷ¶дҪ“жҢҜиҚЎеҷЁпјҲOCXOпјүд»ЈжӣҝVCO[6]гҖӮ

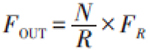

з”ұдәҺдёӨи·Ҝжң¬жҢҜдҝЎеҸ·еңЁзі»з»ҹдёӯиў«еҗҢж—¶дҪҝз”ЁпјҢдёәдәҶдҝқиҜҒдҝЎеҸ·зҡ„дёҖиҮҙжҖ§пјҢйңҖиҰҒйҮҮз”ЁеҗҢдёҖдёӘеҸӮиҖғжәҗпјҢеӣҫ2 дёәжң¬жҢҜжәҗз»“жһ„жЎҶеӣҫгҖӮADI е…¬еҸёзҡ„йў‘зҺҮеҗҲжҲҗеҷЁADF4002пјҢз»“еҗҲеӨ–йғЁжҒ’жё©жҷ¶жҢҜXO5051 д»ҘеҸҠGPS еҸӮиҖғжәҗ10 MHzпјҢ并且组жҲҗPLL йў‘зҺҮеҗҲжҲҗеҷЁгҖӮиҜҘжЁЎеқ—иҫ“еҮә100 MHz зҡ„дҝЎеҸ·з»ҸиҝҮйӣҶжҖ»е…ғ件组жҲҗзҡ„еҠҹеҲҶеҷЁеҗҺеҲҶжҲҗ2 и·ҜпјҢеҲҶеҲ«дҪңдёә2дёӘADF5355 зҡ„еҸӮиҖғйў‘зҺҮпјҢADF5355 жҳҜйӣҶжҲҗVCO зҡ„е®ҪеёҰйў‘зҺҮеҗҲжҲҗеҷЁгҖӮ第1и·ҜеҸӮиҖғдҝЎеҸ·йҖҡиҝҮADF5355 зҡ„й”ҒзӣёзҺҜе’ҢеҖҚйў‘еҷЁеҗҺиҫ“еҮә8.4пҪһ11.2 GHz зҡ„дҝЎеҸ·пјҢд»Ҙ100 MHz жӯҘиҝӣеҸҜи°ғзҡ„жң¬жҢҜдҝЎеҸ·пјҢ然еҗҺз»ҸиҝҮж»ӨжіўеҷЁе’Ңж”ҫеӨ§еҷЁHMC441 еҫ—еҲ°жңҖз»ҲжүҖйңҖзҡ„е°„йў‘жң¬жҢҜпјӣ第2 и·Ҝ100 MHz еҸӮиҖғдҝЎеҸ·йҖҡиҝҮеҸҰдёҖдёӘADF5355 зҡ„й”ҒзӣёзҺҜз”өи·Ҝ并且еҶҚиҫ“еҮә5.4 GHz зҡ„дҝЎеҸ·пјҢеҶҚз»Ҹж•°еӯ—иЎ°еҮҸеҷЁHMC425A е’Ңж”ҫеӨ§еҷЁGVA_83+пјҢеҫ—еҲ°жүҖйңҖеҠҹзҺҮзҡ„дёӯйў‘жң¬жҢҜгҖӮ

еӣҫ2гҖҒжң¬жҢҜжәҗз»“жһ„жЎҶеӣҫ

1.2 зҺҜи·Ҝж»ӨжіўеҷЁи®ҫи®Ў

зҺҜи·Ҝж»ӨжіўеҷЁжҳҜй”ҒзӣёзҺҜз”өи·Ҝдёӯзҡ„йҮҚиҰҒз»„жҲҗеҚ•е…ғпјҢе®ғеҸҜд»ҘдёәVCO жҸҗдҫӣе№ІеҮҖзЁіе®ҡзҡ„и°ғи°җдҝЎеҸ·пјҢз»ҙжҢҒзҺҜи·ҜзЁіе®ҡжҖ§пјҢжҺ§еҲ¶зҺҜи·ҜеёҰеҶ…еӨ–еҷӘеЈ°пјҢжҠ‘еҲ¶еҸӮиҖғиҫ№еёҰжқӮж•Је№Іжү°гҖӮзҺҜи·Ҝж»ӨжіўеҷЁзҡ„йҮҚиҰҒеҸӮж•°дёәзҺҜи·ҜеёҰе®Ҫе’ҢзӣёдҪҚиЈ•еәҰгҖӮзҺҜи·ҜеёҰе®Ҫзҡ„еҮҸе°ҸеҸҜд»Ҙж”№е–„жқӮж•Јзҡ„жҠ‘еҲ¶д»ҘеҸҠVCO иҝ‘з«Ҝзҡ„зӣёдҪҚеҷӘеЈ°пјҢдҪҶеҗҢж—¶еўһеҠ й”Ғе®ҡж—¶й—ҙпјҢ并еҜјиҮҙиҝңз«ҜзӣёдҪҚеҷӘеЈ°зҡ„жҒ¶еҢ–пјӣиҖҢзҺҜи·ҜеёҰе®ҪеўһеӨ§еҲҷдјҡеҮҸе°‘й”Ғе®ҡж—¶й—ҙпјҢдёҚиҝҮж— жі•дҝқиҜҒVCO иҝ‘з«Ҝзҡ„жқӮж•Је’ҢзӣёдҪҚеҷӘеЈ°жҠ‘еҲ¶гҖӮжӯӨеӨ–пјҢеҪ“зҺҜи·ҜеёҰе®Ҫдёәйүҙзӣёйў‘зҺҮзҡ„1/10 еҲ°1/5 ж—¶пјҢй”ҒзӣёзҺҜдјҡеӨұй”Ғ[4-5]гҖӮ

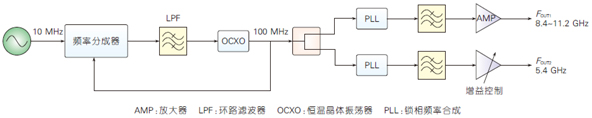

з»јеҗҲзҺҜи·ҜзЁіе®ҡжҖ§гҖҒжқӮж•ЈжҠ‘еҲ¶гҖҒзӣёдҪҚеҷӘеЈ°гҖҒй”Ғе®ҡж—¶й—ҙзӯүеӣ зҙ пјҢжңҖз»ҲзЎ®е®ҡиҫ“еҮәйў‘зҺҮдёә100 MHz зҡ„й”ҒзӣёзҺҜзҺҜи·ҜеёҰе®Ҫдёә30 HzпјҢеҗҢж—¶иҫ“еҮә5.4 GHz д»ҘеҸҠ8.4пҪһ11.2 GHz зҡ„PLL зҺҜи·ҜеёҰе®ҪеҲҷдёә100 kHzгҖӮеӣҫ3 з»ҷеҮәдәҶдёӨи·Ҝй”ҒзӣёзҺҜз”өи·Ҝдёӯеӣӣйҳ¶ж»ӨжіўеҷЁзҡ„з»“жһ„е’ҢеҸ–еҖјгҖӮ

еӣҫ3гҖҒзҺҜи·Ҝж»ӨжіўеҷЁз»“жһ„

1.3 еҚ•зүҮжңәйғЁеҲҶи®ҫи®Ў

жң¬и®ҫи®ЎдёӯйҮҮз”ЁеҚ•зүҮжңәC8051F320еҜ№ADF4002гҖҒ2 дёӘADF5355 иҠҜзүҮд»ҘеҸҠж•°жҺ§иЎ°еҮҸеҷЁHMC425A иҝӣиЎҢиҫ“еҮәйў‘зҺҮе’ҢеҠҹзҺҮзҡ„жҺ§еҲ¶пјҢе…¶дёӯдёӨи·ҜADF5355 е…ұз”Ёж•°жҚ®дј иҫ“е’ҢдёІиЎҢж—¶й’ҹзәҝгҖӮеӣҫ4 дёәеҚ•зүҮжңәжҺ§еҲ¶з”өи·Ҝз»“жһ„еӣҫгҖӮ

еӣҫ4гҖҒеҚ•зүҮжңәжҺ§еҲ¶з”өи·Ҝ

2гҖҒжөӢиҜ•з»“жһңдёҺе®һзү©еӣҫ

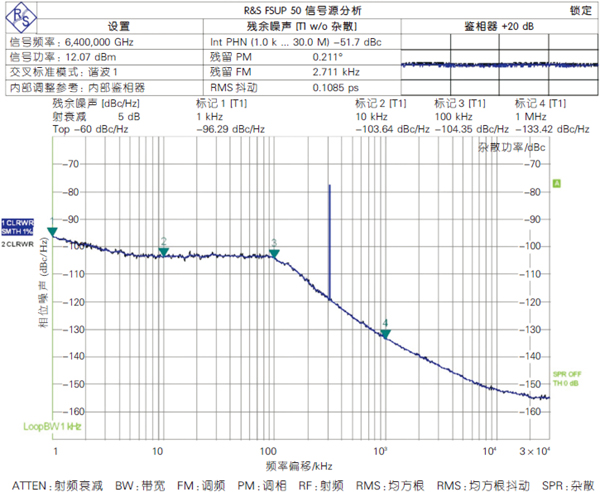

жң¬и®ҫи®Ўе®һзҺ°дәҶдёӨи·ҜдёҚеҗҢйў‘зҺҮзҡ„жң¬жҢҜдҝЎеҸ·иҫ“еҮәпјҢе…·жңүиҫғеҘҪзҡ„зӣёдҪҚеҷӘеЈ°гҖӮеҲ©з”ЁRS зҡ„зӣёдҪҚеҷӘеЈ°еҲҶжһҗд»ӘеҲҶеҲ«еҜ№дёӨи·Ҝиҫ“еҮәдҝЎеҸ·зҡ„зӣёдҪҚеҷӘеЈ°иҝӣиЎҢдәҶжөӢйҮҸпјҢз»“жһңеҰӮеӣҫ5гҖҒ6 жүҖзӨәгҖӮеңЁ8.4пҪһ11.2 GHz йў‘еёҰеҶ…йҖүжӢ©10 GHz дҝЎеҸ·зҡ„зӣёдҪҚеҷӘеЈ°жөӢиҜ•з»“жһңпјҢеҸӮиҖғйў‘зҺҮжәҗдёәзӣёеҷӘд»ӘиҮӘеёҰзҡ„10 MHzгҖӮ

еӣҫ5гҖҒADF5355 иҫ“еҮә5.4 GHz зӣёдҪҚеҷӘеЈ°

еӣҫ6гҖҒADF5355 иҫ“еҮә10 GHz зӣёдҪҚеҷӘеЈ°

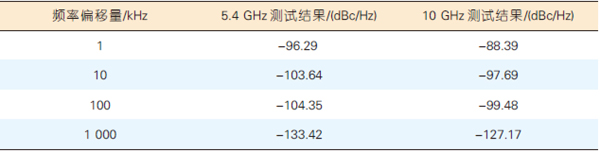

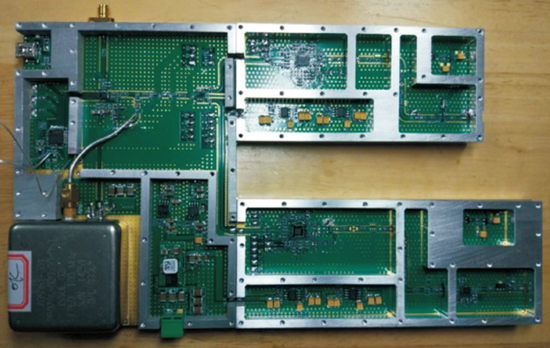

д»Һеӣҫ5гҖҒ6 дёӯеҸҜд»ҘзҹҘйҒ“пјҡ5.4 GHz дҝЎеҸ·иҫ“еҮәеҠҹзҺҮдёә12.07 dBmпјҢ10 GHzзҡ„дҝЎеҸ·иҫ“еҮәеҠҹзҺҮзәҰдёә13.8 dBmпјҢ 并且дёӨи·ҜADF5355 й”ҒзӣёзҺҜз”өи·Ҝзҡ„иҫ“еҮәдҝЎеҸ·зҡҶе…·жңүиүҜеҘҪзҡ„зӣёдҪҚеҷӘеЈ°пјҢе…·дҪ“з»“жһңеҰӮиЎЁ1жүҖзӨәгҖӮйҖҡиҝҮдёҠдҪҚжңәиҝӣиЎҢйў‘зҺҮжҺ§еҲ¶пјҢеҲ©з”ЁзӣёеҷӘд»ӘеҜ№йў‘зҺҮиҢғеӣҙдёә8.4~11.2 GHz,жӯҘиҝӣ100 MHz зҡ„жң¬жҢҜдҝЎеҸ·иҫ“еҮәеҠҹзҺҮиҝӣиЎҢдәҶжөӢиҜ•пјҢз»“жһңеҰӮеӣҫ7 жүҖзӨәгҖӮеңЁиҜҘйў‘еёҰеҶ…иҫ“еҮәжңҖеӨ§еҠҹзҺҮдёә14.57 dBmпјҢжңҖе°ҸеҠҹзҺҮдёә6.7 dBmгҖӮеҖјеҫ—жіЁж„Ҹзҡ„жҳҜпјҡеңЁиҜҘйў‘еёҰеҶ…дҝЎеҸ·иҫ“еҮәеҠҹзҺҮжө®еҠЁиҫғеӨ§пјҢиҝҷдё»иҰҒжҳҜз”ұдәҺADF5355 зҡ„иҫ“еҮәеҠҹзҺҮжңү8 dBm зҡ„еҸҳеҢ–иҢғеӣҙгҖӮеңЁеҗҺз»ӯй“ҫи·Ҝи®ҫи®ЎдёӯеҸҜд»Ҙз»“еҗҲж•°жҺ§иЎ°еҮҸеҷЁжқҘе№іиЎЎеҗ„дёӘйў‘зӮ№зҡ„иҫ“еҮәеҠҹзҺҮгҖӮжӯӨеӨ–пјҢеӣҫдёӯи°ұзәҝзҡ„дёҚжё…жҷ°дё»иҰҒжҳҜз”ұдәҺдёҠдҪҚжңәеҸҳжҚўйў‘зҺҮзҡ„йҖҹеәҰеӨ§дәҺжң¬жҢҜдҝЎеҸ·й”Ғе®ҡзҡ„йҖҹеәҰпјҢеңЁе®һйҷ…еә”з”ЁдёӯеҸҜд»ҘзӯүеҚ•дёӘйў‘зӮ№й”Ғе®ҡеҗҺпјҢеҶҚиҝӣиЎҢйў‘зҺҮеҲҮжҚўпјҢд»ҘдҝқиҜҒжң¬жҢҜдҝЎеҸ·иүҜеҘҪзҡ„жҖ§иғҪгҖӮеӣҫ8 дёәжң¬жҢҜжәҗе®һзү©еӣҫгҖӮ

иЎЁ1гҖҒжң¬жҢҜжәҗзӣёдҪҚеҷӘеЈ°жөӢиҜ•з»“жһң

еӣҫ7гҖҒ8.4пҪһ11.2 GHz жң¬жҢҜдҝЎеҸ·иҫ“еҮәеҠҹзҺҮ

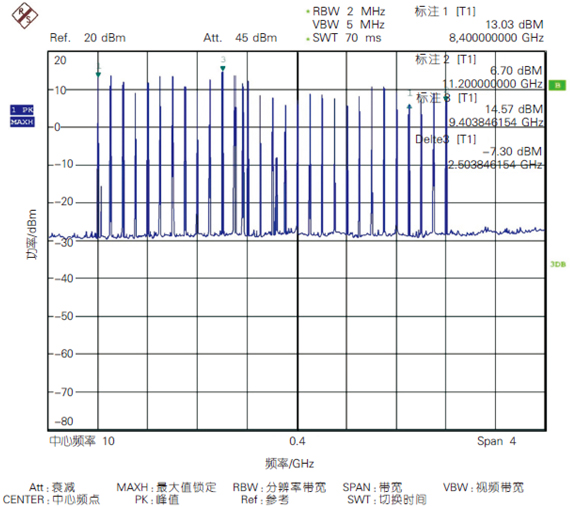

еӣҫ8гҖҒжң¬жҢҜзі»з»ҹе®һзү©еӣҫ

3гҖҒз»“жқҹиҜӯ

ж–ҮдёӯйҖҡиҝҮз»“еҗҲ3 дёӘй”ҒзӣёзҺҜз»“жһ„жҲҗеҠҹе®һзҺ°дәҶеҸӮиҖғйў‘зҺҮзҡ„жҸҗеҚҮе’Ң2 дёӘдёҚеҗҢйў‘ж®өжң¬жҢҜжәҗзҡ„иҫ“еҮәпјҢеҸҜеҗҢж—¶з”ЁдәҺдёӯйў‘д»ҘеҸҠе°„йў‘жЁЎеқ—пјҢ并且йҷҚдҪҺдәҶзӣёдҪҚеҷӘеЈ°гҖӮиҫ“еҮәзҡ„дёӨи·Ҝжң¬жҢҜдҝЎеҸ·дёӯпјҢдёҖи·Ҝ5.4 GHz дҝЎеҸ·еҠҹзҺҮеҸҜи°ғпјҢеҸҰдёҖи·Ҝ8.4пҪһ11.2 GHz дҝЎеҸ·еҸҜе®һзҺ°иҫғе®Ҫйў‘еёҰеҶ…жң¬жҢҜжәҗзҡ„иҫ“еҮәгҖӮеңЁеҗҺз»ӯз ”з©¶дёӯпјҢжҲ‘们еҸҜд»ҘйҖҡиҝҮеҠҹеҲҶжЁЎеқ—пјҢй…ҚеҗҲж”ҫеӨ§еҷЁе®һзҺ°еӨҡи·ҜеҗҢйў‘еҗҢзӣёзҡ„жң¬жҢҜдҝЎеҸ·зҡ„иҫ“еҮәд»Ҙж»Ўи¶іеӨ§и§„жЁЎMIMO зі»з»ҹеҜ№дәҺжң¬жҢҜзҡ„зӣёе…ійңҖжұӮгҖӮ

еҸӮиҖғж–ҮзҢ®

[1] е°ӨиӮ–иҷҺ.5G 移еҠЁйҖҡдҝЎеҸ‘еұ•и¶ӢеҠҝдёҺиӢҘе№Іе…ій”®жҠҖжңҜ[J].дёӯеӣҪ科еӯҰ,2014,5(44):551-563[2] еҲҳе…Ҷж Ӣ.йқўеҗ‘5G 移еҠЁйҖҡдҝЎзі»з»ҹзҡ„жң¬жҢҜжҠҖжңҜз ”з©¶[C]//2015 е№ҙе…ЁеӣҪеҫ®жіўжҜ«зұіжіўдјҡи®®и®әж–ҮйӣҶ.еҗҲиӮҘ:дёӯеӣҪз”өеӯҗеӯҰдјҡ,2015

[3] еҚ•жңҲеҝ .еҹәдәҺADF4351 зҡ„йў‘зҺҮжәҗи®ҫи®ЎдёҺе®һзҺ°[J].ж— зәҝз”өйҖҡдҝЎжҠҖжңҜ,2014,40(6):85-88

[4] иөөжё…жҪҮ.еҹәдәҺе®ҪеёҰеӨҡйҖҡйҒ“еҫ®жіўж”¶еҸ‘дҝЎжңәзҡ„жң¬жҢҜжәҗи®ҫи®ЎдёҺе®һзҺ°[D].йқ’еІӣ:еұұдёңеӨ§еӯҰ,2015

[5] иӨҡйў–йў–.еӨ§и§„жЁЎMIMO зі»з»ҹе°„йў‘е…ій”®жҠҖжңҜз ”з©¶[D].еҚ—дә¬:дёңеҚ—еӨ§еӯҰ,2015

[6] жһ—жіў.еӨ§и§„жЁЎMIMO еӨ–йғЁжң¬жҢҜзҡ„з ”з©¶[D].еҚ—дә¬:дёңеҚ—еӨ§еӯҰ, 2018

[7] й»„з»ҙиҫ°.йқўеҗ‘дёӢдёҖ代移еҠЁйҖҡдҝЎзі»з»ҹзҡ„еӨҡйҖҡйҒ“射频收еҸ‘дҝЎжңәд»ҘеҸҠйў‘зҺҮжәҗзҡ„з ”з©¶[D].еҚ—дә¬:дёңеҚ—еӨ§еӯҰ,2017

[8] BANERJEE D. PLL Performance, Simulation, and Design 5th Edition [M]. USA: National, 2017:3-8

дҪңиҖ…пјҡиғЎи’ҷзӯ гҖҒе‘ЁеҒҘд№үпјҢдёңеҚ—еӨ§еӯҰ

жқҘжәҗпјҡдёӯе…ҙйҖҡи®ҜжҠҖжңҜ

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·