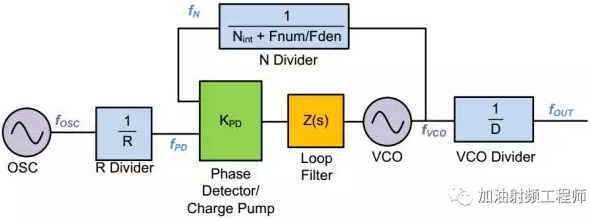

现在很多集成VCO的频率合成器的设计思想,都是利用输出端加分频器来扩展输出范围,如图1所示。比如ADI的HMC832,其VCO的频率为1500~3000MHz,利用其后的分频器(1/2/4/6/…60/62),最终获得25MHz~3000MHz的频率覆盖范围。

图1、PLL withVCO divider

在文献【1】中讲到,当VCO的输出信号通过D分频时,其相噪下降20log10(D);杂散幅度亦下降20log10(D),但频率偏移量(offset frequency)保持不变。

这是为什么呢?我们可以从相位噪声的本质说起。

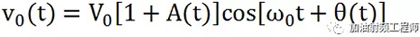

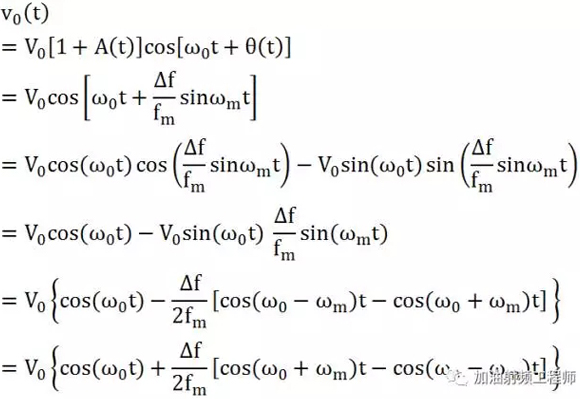

VCO的输出信号可以表示为【2】:

A(t)为振幅变化,θ(t)为相位变化。输出信号频率的微小变化,可以表示为载波的相位调制:

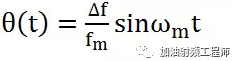

假设幅度变化为0,且

,则:

,则:

如果把偏离载波wm的噪声理解为相位噪声的话,则相噪为20log(Δf/2fm) dBc/Hz;同样,如果是看成杂散的话,则杂散的幅度为20log(Δf/2fm) dBc。

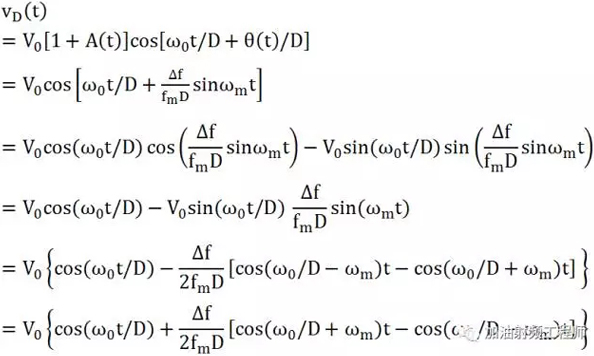

当输出信号经过D分频器时,相位被整个除以D【3】:

如果把wm处的能量看成是相噪的话,相噪的幅度减小20logDdB;若看成杂散的话,杂散的幅度亦减小20logD,但是偏移量不变,还是在偏移载波wm处。

PS:我能理解如果是倍频器的话,因为倍频器的模型可以当成y=a0+a1v+a2v2+a3v3+….,这样的话,倍频的话,是直接在整个相位上倍频。但是分频器的模型是什么呢?请高手赐教!

参考文献:

【1】 Dean Banerjee PLL Performance, Simulation, and Design 5th Edition【2】 David M. Pozar 微波工程

【3】 http://www.ko4bb.com/~bruce/IdealFreqMultDiv.html

粤公网安备 44030902003195号

粤公网安备 44030902003195号