DARPA是美国最尖端的政府研究机构,每年都会资助一批其认为会对未来社会和科技发展起到重要影响的项目,因此它的资助方向可以看作业界新潮流的风向标。最近,DARPA召开了电子复兴计划峰会(ERI Summit),并在峰会上公布了其最新资助的一批项目。这些项目主要在敏捷设计和超高效计算领域,DARPA对这些项目的资助可谓一掷千金,一个团队往往可以获得五百到数千万美元的项目经费(在美国电子类项目的经费都不好拿,往往拿了五十万的经费都已经足够一个IEEE Fellow级别的教授举杯庆祝了)。接下来让我们来看看这些项目的具体情况。本文中的资助信息来自于IEEE Spectrum的公开报道。

敏捷设计

如我们在之前文章错过这个点,中国芯要再落后十年?中提到的,DARPA在半导体敏捷设计领域一直在积极布局。美国的科技中心即位于北加州湾区的“硅谷”,可是现在“硅谷”中最活跃的早已不是那些靠“硅”(芯片)吃饭的公司,而是软件/互联网公司。究其原因,一个很重要的方面是芯片公司资产太“重”,需要大量的投资才能开始运营。在软件/互联网领域,往往几个主创人员有了新的创意后搬几台电脑在车库里一两个月就能把产品雏形做出来,然后就可以快速融资并走上正轨。相反,在芯片领域,主创人员从脑子里构思一个新的idea到做出成品的道路太漫长而且需要大量资本投入,这就大大降低了产业和创业公司的活跃度。许多人所鄙视的“ppt造芯”,其实恰恰折射出了芯片领域创业人员的无奈:正是因为需要大量先期资本做出样品才不得不先拿个幻灯片去以较低估值融资,如果几个人不需要资本就能先把芯片样品做出来想必就可以直接靠样品芯片而非ppt去说事了。

为什么芯片设计又贵又慢?相比软件行业,芯片行业除了需要流片之外,还有两点问题给芯片公司的效率加上了瓶颈。首先是版图设计,尤其是模拟/混合信号版图设计。这一点可以类比软件领域的编译器,如果你做软件的话把代码写完只要按一下“编译”就能把最终可执行文件生成出来;但是在芯片领域可就没那么简单了,你在电路设计完成之后不存在点个按钮就能出成品芯片的事情,而必须要花很多时间去做版图设计生成GDS,相当于在软件行业你还要亲自把你的代码翻译成机器码。第二个问题就是设计复用问题。软件行业的开发可以站在巨人肩膀上,很多函数都有现成的函数库,调用一下就行不用重复造轮子,相反在芯片领域目前绝大多数模块都必须从头开始设计,很难实现设计复用。如果这两个问题能得到解决,那么芯片行业的资产过“重”问题就能得到有效改善,从而会有大量新兴公司冒出来,对整个行业的创新和自我迭代效率都能带来深远影响。

DARPA今年在ERI峰会上提出的两个项目IDEA和POSH就是针对这两点,其终极目标是实现在24小时内即可实现全自动设计迭代。

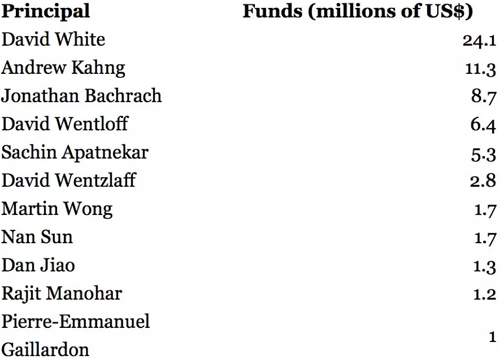

IDEA针对的是全自动芯片版图生成器。众所周知,数字电路的版图生成自动化程度已经相当高,但是模拟和混合信号电路仍然非常依赖手工去做版图。所以DARPA希望能在这个领域有所突破。这次资助的最大赢家是来自Cadence的David White组,豪取两千四百万美元的资助。Cadence在相关声明中表示,将继续在Virtuoso工具中加入更多机器学习和人工智能来帮助版图生成自动化。除此之外,来自UCSD的Andrew Kahng也拿到了一千一百万美元,UT Austin的华人教授Nan Sun也获得了一百七十万美元的资助。

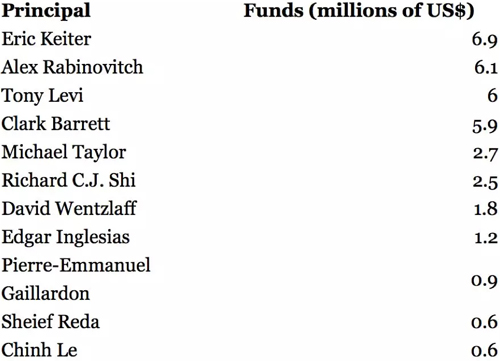

POSH针对的则是开源硬件项目。POSH项目的负责人Andreas Olofsson表示,“POSH的终极目标是让高性能SoC设计民主化。POSH希望能发展出可持续的开源硬件生态以及相应的验证工具。POSH同时希望能提供一个经过广泛认证的开源硬件基础模组库,大家都可以自由调用这些库里的模块,从而避免在硬件领域重复造轮子的问题。”在POSH项目中,我们可以看到来自Princeton的Eric Keiter获得了六百九十万美元的资助,而University of Washington的Richard Shi教授也获得了二百五十万美元的资助。

超高效计算

除了敏捷设计之外,超高效计算芯片也是DARPA这次重点支持的另一个方向。超高效计算可以分为两个领域:芯片架构创新和芯片工艺创新。当然,如下面我们会看到的,这两个领域并非完全割裂,芯片工艺的创新也会影响芯片架构的创新。

在芯片架构创新领域,DARPA关注的重点是软件定义架构(softwaredefined hardware项目,SDH)和domain-specific片上系统(domain-specific SoC项目,DSSoC)。软件定义架构和domain-specific可谓是“阴”与“阳”,阴阳互生,在矛盾中发展。在架构发展历史上,我们总是看到软件定义可配置的通用架构发展到一定阶段遇到瓶颈后,domain-specific以其高效率得到更多应用,然而domain-specific又会遇到利用率低的问题,于是新的软件可配置架构在吸取之前domain-specific设计精华的基础上,又诞生了效率更高的可配置架构成为主流,直到再次遇到新的问题domain-specific再次出场。这次DARPA对于SDH和DSSoC的投资,可谓是看透了其中的道理,内外兼修,不错过硬币的任何一面。

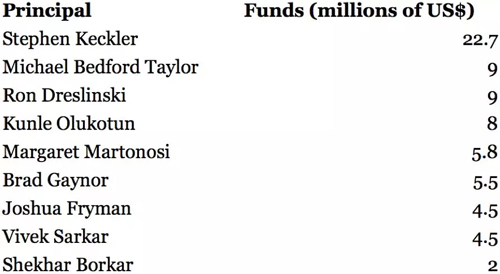

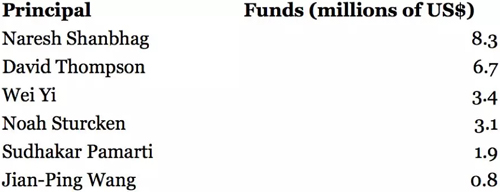

在SDH项目,Nvidia的Stephen Keckler获得了接近两千三百万美元的项目资金,此外华盛顿大学的Michael Taylor(以解决Dark Silicon问题为己任,提出了511核的RISC-V处理器Celerity,并且是矿机芯片领域学术研究先驱)和斯坦福大学的Kunle Olukotun(多核处理器的先驱,SUN Ultra SPARCT1 “Niagara”的架构师,同时也是初创公司SambaNova的创始人前一阵刚拿了Google Ventures领投的四千多万美元)也获得了一千万美元左右的资助。从这些研究组的研究方向来看,DARPA的SDH主要资助的是下一代多核处理器芯片系统的研究。

在DSSoC领域,DARPA资助了一些和通信芯片有关的研究,可见类似software-defined radio和cognitive radio之类的研究还得继续。DSSoC的项目主管Tom ondeau表示,灵活而适应性强的无线电系统在面对复杂的信号环境时仍然是至关重要,而这些DSSoC系统必须可以像传统处理器一样编程,同时在处理信号处理算法时又能以低功耗完成大量运算。DSSoC资助的项目组虽然数量较少,但是资助的金额却是不小。

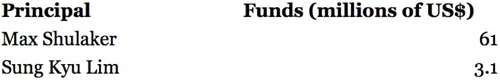

在芯片工艺创新领域,DARPA又分为两个计划,即致力于三维集成的3D-SoC计划和新型计算基础技术(Foundations Required for Novel Compute,FRANC)。3D-SoC顾名思义是为了资助能使用高级封装集成技术把各种芯片以三维方式集成到一起。MIT的Max Shulakar研究组拿到了六千万美元的巨额资助,其研究方向就是把多块使用成熟的CMOS工艺芯片(如90nm工艺)用3D方式集成到一起从而让整体模组达到7nm芯片的性能。相关技术也可参见我们之前的文章摩尔定律何去何从之二:More Moore or More Than Moore?。

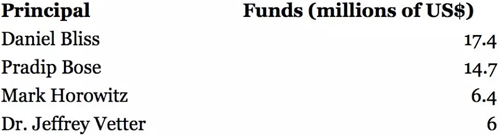

最后,FRANC项目这次的资助目标是新一代存储器架构,包括内存内计算。FRANC的项目负责人陈阳闿博士在访谈中表示,FRANC希望能资助利用新材料和器件把嵌入式非易失性存储器的性能提升十倍,而这样的提升能支持新兴的以内存为中心的心计算机架构从而克服传统冯诺伊曼架构的内存墙问题。

结语

DARPA的资助代表了电子行业发展的新方向。这次的关键词有:敏捷设计:包括下一代EDA以及开源硬件,超高效计算:软件定义可配置架构——主要指下一代众核处理器系统;domain-specific SoC——目前主要集中在通信信号处理领域;下一代3D集成技术——超越摩尔;下一代内存技术——包括内存内计算,突破冯诺伊曼架构的瓶颈。

粤公网安备 44030902003195号

粤公网安备 44030902003195号