зІҫзЎ®жҺ§еҲ¶е·®еҲҶдҝЎеҸ·зҡ„е·®еҲҶзӣҙжөҒиҖҰеҗҲADCиҫ“е…Ҙ

гҖҖгҖҖйҡҸзқҖADCзҡ„дҫӣз”өз”өеҺӢзҡ„дёҚж–ӯйҷҚдҪҺпјҢиҫ“е…ҘдҝЎеҸ·ж‘Ҷе№…зҡ„дёҚж–ӯйҷҚдҪҺпјҢиҫ“е…ҘдҝЎеҸ·зҡ„е…ұжЁЎз”өеҺӢзҡ„зІҫзЎ®жҺ§еҲ¶жҳҫеҫ—и¶ҠжқҘи¶ҠйҮҚиҰҒгҖӮдәӨжөҒиҖҰеҗҲиҫ“е…ҘзӣёеҜ№жҜ”иҫғз®ҖеҚ•пјҢиҖҢзӣҙжөҒиҖҰеҗҲиҫ“е…Ҙе°ұжҜ”иҫғеӨҚжқӮгҖӮ

гҖҖгҖҖе…ёеһӢзҡ„дҫӢеӯҗжҳҜжӯЈдәӨдёӢеҸҳйў‘пјҲж··йў‘еҷЁпјүиҫ“еҮәеҲ°ADCиҫ“е…Ҙзҡ„з”өи·Ҝи®ҫи®ЎгҖӮж··йў‘еҷЁиҫ“еҮәзҡ„жҳҜе·®еҲҶдҝЎеҸ·пјҢе…¶е…ұжЁЎз”өеҺӢиҜҜе·®еҫҖеҫҖжҜ”иҫғеӨ§пјҢеңЁйҖҒеҲ°ADCиҫ“е…Ҙз«Ҝд№ӢеүҚйңҖиҰҒиҝӣиЎҢж»Ө波并且иҰҒжҠҠзӣҙжөҒз”өе№іиҪ¬жҚўеҲ°ADCиҫ“е…ҘжүҖйңҖзҡ„з”өе№ідёҠгҖӮиҝҷж ·зҡ„и®ҫи®Ўе°ұжҜ”иҫғжңүжҢ‘жҲҳжҖ§гҖӮ

гҖҖгҖҖеңЁж”ҫеӨ§еҷЁиҫ“еҮәз«Ҝе’ҢADCиҫ“е…Ҙз«Ҝд№Ӣй—ҙпјҢеҫҖеҫҖйңҖиҰҒдәҢйҳ¶ж»Өжіўз”өи·ҜгҖӮдёҖж–№йқўпјҢйңҖиҰҒеңЁADCиҫ“е…Ҙз®Ўи„ҡеүҚйқўж”ҫзҪ®з”өе®№жқҘеҗёж”¶ADCеҶ…йҮҮж ·дҝқжҢҒз”өи·Ҝзҡ„ејҖе…іе№Іжү°гҖӮеҸҰдёҖж–№йқўпјҢйңҖиҰҒеңЁж”ҫеӨ§еҷЁиҫ“еҮәз«Ҝж”ҫзҪ®з”өйҳ»жҲ–з”өж„ҹжқҘйҡ”зҰ»иҝҷдёӘе®№жҖ§иҙҹиҪҪпјҢд»ҺиҖҢзЎ®дҝқж”ҫеӨ§еҷЁзҡ„иҫ“еҮәзЁіе®ҡгҖӮи®ҫи®ЎдәҢйҳ¶ж»Өжіўзҡ„зӣ®зҡ„жҳҜиҺ·еҫ—жӣҙеҘҪзҡ„ж»Өжіўзү№жҖ§е’ҢжҲӘиҮійў‘зҺҮгҖӮеҰӮжһңADCеҶ…йғЁиҫ“е…Ҙз«ҜжІЎжңүbufferпјҢдҫӢеҰӮIntersilзҡ„FemtoChargeзі»еҲ—ADCпјҢADCиҫ“е…Ҙз«ҜдјҡжңүжҳҺжҳҫзҡ„е‘ЁжңҹжҖ§пјҲдёҺйҮҮж ·йў‘зҺҮдёҖиҮҙпјүеҗёж”¶з”өжөҒгҖӮиҝҷж ·пјҢзЎ®дҝқиҫ“е…ҘдҝЎеҸ·зӣҙжөҒз”өе№іжҺ§еҲ¶еңЁADCжүҖйңҖзҡ„з”өе№іиҢғеӣҙеҶ…е°ұжҳҫзҡ„йқһеёёйҮҚиҰҒгҖӮ

гҖҖгҖҖж–°еһӢзҡ„е…Ёе·®еҲҶж”ҫеӨ§еҷЁпјҲFDAпјүеҸҜд»ҘжҺ§еҲ¶иҫ“еҮәе·®еҲҶдҝЎеҸ·зҡ„е…ұжЁЎз”өеҺӢпјҢиҖҢиҝҷдёӘиҫ“еҮәе…ұжЁЎз”өеҺӢе®Ңе…ЁдёҺиҫ“е…Ҙз”өеҺӢж— е…ігҖӮиҜ·и®°дҪҸпјҢиҝҷжҳҜйҖҡиҝҮеңЁADC Vcmз®Ўи„ҡдёҠиҫ“еҮәзү№е®ҡз”өеҺӢе®һзҺ°зҡ„пјҢдёҺиҫ“е…Ҙз«ҜдҝЎеҸ·й“ҫдёҠзҡ„е…ұжЁЎз”өеҺӢе®Ңе…Ёж— е…ігҖӮиҖҢд»ҺFDAиҫ“еҮәеҲ°ADCиҫ“е…Ҙз«Ҝд№Ӣй—ҙдёҚеҸҜйҒҝе…Қдјҡжңүз”өеҺӢйҷҚпјҢиҝҷжҳҜз”ұдәҺзәҝи·ҜдёҠзҡ„зӯүж•Ҳйҳ»жҠ—йҖ жҲҗзҡ„гҖӮиҝҷж ·пјҢе®һйҷ…еҲ°иҫҫADCиҫ“е…Ҙз«Ҝзҡ„е…ұжЁЎз”өеҺӢдёҚеҸҜйҒҝе…ҚдјҡжңүдёҖе®ҡиҜҜе·®пјҢиҜҜе·®еӨ§е°ҸдёҺADCиҫ“е…Ҙз”өжөҒд»ҘеҸҠдёҚеҗҢеҷЁд»¶иҰҒжұӮзҡ„дёҚеҗҢе…ұжЁЎз”өеҺӢзӣёе…іпјҢеӯҳеңЁдёҖе®ҡзҡ„дёҚзЎ®е®ҡжҖ§гҖӮзӣ®еүҚеӨ§йғЁеҲҶзҡ„й«ҳйҖҹADCйғҪжҳҜ1.8Vдҫӣз”өпјҢжүҖйңҖиҫ“е…Ҙе…ұжЁЎз”өеҺӢеӨ§еӨҡеңЁ0.4-0.8Vд№Ӣй—ҙпјҢиҖҢдё”еҸҜд»ҘжҺҘеҸ—зҡ„иҜҜе·®иҢғеӣҙйғҪиҫғе°ҸгҖӮеӨ§еӨҡж•°ж–°жҺЁеҮәзҡ„ADCйғҪдјҡеҲ—еҮәSFDR vs Vcmзҡ„жӣІзәҝпјҢVcmдёҺVcmе…ёеһӢеҖјд№Ӣй—ҙдёҚи¶…иҝҮ+/-200mVгҖӮ

гҖҖгҖҖеҸҰеӨ–дёҖдёӘй—®йўҳжҳҜпјҡеңЁFDAзҡ„зӣҙжөҒиҖҰеҗҲе·®еҲҶиҫ“еҮәеә”з”ЁдёӯпјҢеҝ…然дјҡжңүе…ұжЁЎз”өжөҒжөҒиҝҮж”ҫеӨ§еҷЁеҸҚйҰҲз”өи·ҜпјҢеңЁжҹҗдәӣFDAеһӢеҸ·жҲ–иҖ…еә”з”ЁдёӯпјҢиҝҷдёӘз”өжөҒдјҡиҫғеӨ§пјҢз”ҡиҮіи¶…иҝҮж··йў‘еҷЁзҡ„йўқе®ҡз”өжөҒпјҢ并且/жҲ–иҖ…еҸҚиҝҮжқҘеҜ№FDAеүҚйқўзҡ„иҫ“е…Ҙз”өжөҒзҡ„е…ұжЁЎз”өеҺӢдә§з”ҹеҪұе“ҚпјҢз”ҡиҮіеҜјиҮҙдҝЎеҸ·йҘұе’ҢгҖӮиҝҷдәӣй—®йўҳеҝ…йЎ»еңЁи®ҫи®ЎзӣҙжөҒиҖҰеҗҲADCиҫ“е…Ҙз”өи·Ҝзҡ„ж—¶еҖҷеҠ д»Ҙе……еҲҶиҖғиҷ‘гҖӮ

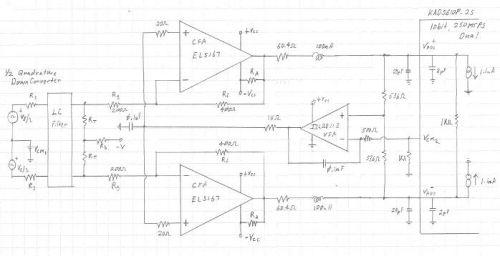

гҖҖгҖҖдёӢеӣҫзҡ„и®ҫи®ЎжҳҜдёҖдёӘдёҚй”ҷзҡ„жӣҝд»Јж–№жЎҲгҖӮз”ЁдёӨдёӘз”өжөҒеҸҚйҰҲж”ҫеӨ§еҷЁпјҲCFAпјүдҪңдёәдҝЎеҸ·йҖҡи·ҜдёҠзҡ„ж”ҫеӨ§еҷЁпјҢз”ЁдёҖдёӘдҪҺжҲҗжң¬зҡ„з”өеҺӢеҸҚйҰҲж”ҫеӨ§еҷЁеҪўжҲҗдёҖдёӘеҸҚйҰҲзҪ‘з»ңжқҘжҺ§еҲ¶дҝЎеҸ·йҖҡи·Ҝзҡ„е…ұжЁЎз”өеҺӢгҖӮ

гҖҖгҖҖд»Һе·ҰеҲ°еҸіпјҡ

гҖҖгҖҖдёӢеҸҳйў‘еҷЁиҫ“еҮәдёҖдёӘдәӨжөҒе·®еҲҶдҝЎеҸ·пјҢе…ұжЁЎз”өеҺӢжҳҜжҹҗдёӘзү№е®ҡзҡ„еҖјVcm1гҖӮ然еҗҺйҖҡиҝҮдёҖдёӘLCж»Өжіўз”өи·ҜжқҘж»ӨйҷӨй«ҳйў‘еҷӘеЈ°е’Ңй•ңеғҸйў‘зҺҮгҖӮж»ӨжіўеҷЁз”ұдёҖдёӘе°Ҹз”өйҳ»пјҢдёІиҒ”дёҖдёӘз”өж„ҹпјҢеҶҚдёӢжӢүдёҖдёӘз”өе®№еҪўжҲҗгҖӮж»ӨжіўеҷЁеҗҺйқўжҳҜжңүRgе’ҢRtз»„жҲҗзҡ„йҳ»жҠ—еҢ№й…ҚзҪ‘з»ңгҖӮиҜ·еҲ«еҝҳдәҶпјҢеҰӮжһңйңҖиҰҒдҝқжҢҒдҝЎеҸ·зҡ„зӣҙжөҒеҲҶйҮҸпјҢж»ӨжіўеҷЁйҮҢйқўеҸӘйңҖиҰҒLе°ұеҸҜд»ҘдәҶгҖӮ

гҖҖгҖҖRtе’ҢRbдёҚжҳҜеҝ…йңҖзҡ„гҖӮRt>RgпјҢRtи®ҫзҪ®дәҶж»ӨжіўеҷЁз«ҜжҺҘйҳ»жҠ—зҡ„дёҖйғЁеҲҶпјҲCFAзҡ„иҙҹиҫ“е…Ҙз«ҜжҳҜдҪҺйҳ»жҠ—зҡ„пјҢRgеңЁиҝҷйҮҢеҸҜд»ҘзңӢдҪңжҺҘең°иҝһжҺҘпјүгҖӮиҝҷдёӘз”өйҳ»зҪ‘з»ңзҡ„дҪңз”Ёд№ӢдёҖжҳҜеҲ©з”Ёж··йў‘еҷЁзҡ„иҫ“еҮәе…ұжЁЎз”өжөҒеңЁRgдёҠеҪўжҲҗз”өеҺӢйҷҚпјҢд»ҺиҖҢжҠҠе…ұжЁЎз”өеҺӢжҺ§еҲ¶еңЁCFAиҙҹиҫ“е…Ҙз«Ҝзҡ„еҠЁжҖҒиҢғеӣҙеҶ…гҖӮеҫҲеӨҡжғ…еҶөиҝҷдёӘз”өйҳ»зҪ‘з»ңдёҚжҳҜеҝ…йЎ»зҡ„пјҢиҖҢеҸӘйңҖиҰҒRgеҒҡз«ҜжҺҘе°ұеҸҜд»ҘдәҶгҖӮдёҚиҝҮпјҢRbзҡ„зЎ®еҸҜд»Ҙжңүж•Ҳзҡ„е°Ҷе…ұжЁЎз”өеҺӢжҺ§еҲ¶еңЁжүҖйңҖиҰҒзҡ„з”өе№ідёҠиҖҢдёҚеҪұе“ҚдәӨжөҒдҝЎеҸ·гҖӮд»Јд»·жҳҜеўһеӨ§дәҶдёҖзӮ№з”өжөҒгҖӮ

гҖҖгҖҖRgе’ҢRFе…ұеҗҢз»„жҲҗиҝҗж”ҫзҡ„еўһзӣҠгҖӮдёҺVFAдёҚдёҖж ·пјҢCFAзҡ„Rf еҖјйңҖиҰҒеҸӮиҖғеҷЁд»¶жҺЁиҚҗзҡ„еҖјгҖӮRfиҝҮеӨ§пјҢдјҡеҜ№иҝҗж”ҫиҝҮиЎҘеҒҝпјҢйҷҚдҪҺеёҰе®ҪпјҢеўһеӨ§з”өжөҒеҷӘеЈ°гҖӮRfиҝҮе°ҸпјҢдјҡеңЁиҫ“еҮәз«Ҝдә§з”ҹиҝҮеҶІгҖӮеӣҫдёӯзҡ„еҖјжҳҜй’ҲеҜ№EL5167еёҰе®ҪеӨ§дәҺ400MHzеә”з”Ёзҡ„е…ёеһӢеҖјгҖӮ

гҖҖгҖҖиҝҗж”ҫиҫ“еҮәз«ҜжҳҜдёҖеҜ№е·®еҲҶRLCж»ӨжіўеҷЁгҖӮйҖүжӢ©еҷЁд»¶еҸӮж•°ж—¶йҰ–е…ҲжҳҜйҖүжӢ©з¬ҰеҗҲADCиҫ“е…Ҙзү№жҖ§зҡ„з”өе®№еҖјгҖӮз”өж„ҹеҖјиҫғе°ҸжӣҙеҗҲйҖӮпјҢд»Ҙе…Қз”өж„ҹиҮӘиә«и°җжҢҜйў‘зҺҮиҗҪеңЁж»ӨжіўеҷЁйҖҡеёҰд№ӢеҶ…гҖӮдёІиҒ”з”өйҳ»зҡ„дҪңз”ЁжҳҜе°Ҷиҝҗж”ҫдёҺе…¶ж„ҹжҖ§/е®№жҖ§иҙҹиҪҪйҡ”зҰ»пјҢдҝқжҢҒиҝҗж”ҫзЁіе®ҡпјҢиҝҳиғҪеҜ№ADCиҫ“е…Ҙиө·еҲ°дёҖе®ҡзҡ„дҝқжҠӨдҪңз”ЁпјҢйҒҝе…ҚиҝҮеӨ§зҡ„з”өжөҒжөҒе…ҘADCпјҢдҪҶжҳҜдјҡйҖ жҲҗдёҖе®ҡзҡ„дҝЎеҸ·иЎ°еҮҸгҖӮжңҖеҗҺжҳҜдёҖдёӘ并иҒ”з”өйҳ»пјҢе®һйҷ…дёҠADCеҶ…йғЁиҫ“е…Ҙз«Ҝд№ҹжңүиҝҷж ·дёҖдёӘз”өйҳ»пјҢиҝҷдёӨдёӘз”өйҳ»е№¶иҒ”е°Ҷйҳ»еҖјеҮҸеҚҠгҖӮиҝҷдёӘз”өйҳ»ж„ҹеә”дҝЎеҸ·зҡ„е…ұжЁЎз”өеҺӢпјҢиҖҢеҸҲеҜ№дҝЎеҸ·жң¬иә«дёҚдә§з”ҹеҪұе“ҚгҖӮиҝҷдёӘж»ӨжіўеҷЁдёәдәҢйҳ¶дҪҺйҖҡж»ӨжіўеҷЁпјҢжҲӘжӯўйў‘зҺҮ102MHzпјҢQеҖј0.9гҖӮиҝҷж ·дҝЎеҸ·дјҡжңүиҪ»еҫ®иҝҮеҶІпјҢдҪҶжҳҜдәҢйҳ¶-3dBеёҰе®Ҫ123MHzгҖӮз»“еҗҲKAD5610P-25пјҢеҸҢ10bitпјҢ250MSPS FemtoCharge ADCпјҢж»ӨжіўеҷЁеҸҜд»Ҙжңүж•Ҳзҡ„ж»ӨйҷӨдҝЎеҸ·й“ҫеҸҠж”ҫеӨ§еҷЁеёҰжқҘзҡ„еҷӘеЈ°гҖӮеңЁйҮҮж ·зҺҮ250MSPSж—¶пјҢADCиҫ“е…ҘDCз”өжөҒеӨ§зәҰжҳҜ1.1mAпјҢиҖҢд»Һж”ҫеӨ§еҷЁеҲ°ADCд№Ӣй—ҙзҡ„йҳ»жҠ—дёә60.4欧е§ҶпјҢйӮЈд№ҲDCз”өеҺӢйҷҚдёә66.4mVгҖӮиҝҷдёӘз”өеҺӢйҷҚеҸҜд»Ҙз”ЁISL28113з»„жҲҗзҡ„еҸҚйҰҲиЎҘеҒҝзҪ‘з»ңжқҘиЎҘеҒҝгҖӮ

гҖҖгҖҖеңЁ+/-5Vдҫӣз”өж—¶пјҢEL5167иҫ“еҮәж‘Ҷе№…дёә+/-3.9VгҖӮADCдҫӣз”өдёәеҚ•1.8VгҖӮеҶ…йғЁзҡ„дҝқжҠӨдәҢжһҒз®ЎеңЁиҫ“е…ҘдҝЎеҸ·и¶…еҮәиҢғеӣҙ0.6Vд»ҘдёҠж—¶жү“гҖӮ60.4欧е§Ҷзҡ„дёІиҒ”з”өйҳ»дҝқиҜҒдәҶдәҢжһҒз®Ўжү“ејҖж—¶зҡ„з”өжөҒдёҚи¶…иҝҮ24mAпјҲжӯЈз«Ҝпјүе’Ң54mAпјҲиҙҹз«ҜпјүпјҢиҝҷж ·еҸҜд»Ҙжңүж•Ҳзҡ„дҝқжҠӨеҷЁд»¶дёҚеҸ—жҚҹеқҸгҖӮ

гҖҖгҖҖADCдјҡжҸҗдҫӣдёҖдёӘVcmеҸӮиҖғз”өеҺӢиҫ“еҮәгҖӮиҝҷдёӘеҠҹиғҪйқһеёёжңүз”ЁпјҢе°Өе…¶й’ҲеҜ№еӨҡи·ҜADCпјҲжҜ”еҰӮKAD5610P-25пјүдёҠз”өж ЎеҮҶпјҢеҸҜд»Ҙж¶ҲйҷӨеҷЁд»¶д№Ӣй—ҙзҡ„VcmиҜҜе·®пјҢи®©еӨҡи·ҜADCд№Ӣй—ҙзҡ„VcmеҖјдҝқжҢҒй«ҳеәҰдёҖиҮҙпјҢиҖҢдё”зІҫзЎ®жҖ§еҫҲй«ҳгҖӮе°Ҷеӣҫдёӯзҡ„Vcm2дёҺж”ҫеӨ§еҷЁеҮәи·ҜдҝЎеҸ·дёҠзҡ„VcmиҝӣиЎҢжҜ”иҫғпјҢ然еҗҺйҖҡиҝҮISL28113зҡ„еҸҚйҰҲзҪ‘з»ңпјҢеҸҜд»Ҙе®һзҺ°иҝҷдёӘеҠҹиғҪгҖӮдҪҺйҖҹзҡ„ISL28113 VFAе°ҶдёӨдёӘз”өеҺӢзҡ„е·®йҖҒеҲ°й«ҳйў‘CFAзҡ„жӯЈеҗ‘иҫ“е…Ҙз«ҜпјҢеҸҜд»ҘдҪҝCFAиҫ“еҮәзҡ„Vcmе§Ӣз»ҲдёҺVcm2дҝқжҢҒдёҖиҮҙгҖӮиҝҷж ·пјҢжҲ‘们дёҚеҶҚйңҖиҰҒиҖғиҷ‘ж··йў‘еҷЁжҲ–иҖ…е…¶е®ғеҷЁд»¶дә§з”ҹзҡ„VcmиҜҜе·®дәҶгҖӮ

гҖҖгҖҖеӣҫдёӯе…¶е®ғдёҖдәӣеҷЁд»¶жҳҜеҸҜйҖүзҡ„жҲ–иҖ…жҳҜй’ҲеҜ№жүҖйҖүеҷЁд»¶зҡ„гҖӮ

гҖҖгҖҖVcm2з«ҜжҺҘең°зҡ„1k欧е§Ҷз”өйҳ»жҳҜз”ЁжқҘдёӢжӢүзҡ„пјҢдә§з”ҹдёҖдёӘдёӢжӢүз”өжөҒгҖӮз”ұдәҺKAD5610-25еҸӘиғҪиҫ“еҮәз”өжөҒпјҢиҖҢиҝҗж”ҫз”өи·ҜйңҖиҰҒеҸҢеҗ‘з”өжөҒгҖӮдёӢжӢүз”өйҳ»еҸҜд»ҘжҸҗдҫӣеҸҢеҗ‘з”өжөҒгҖӮ

гҖҖгҖҖдёӨдёӘRaз”өйҳ»д»Һиҝҗж”ҫиҫ“еҮәз«ҜиҝһжҺҘиҙҹз”өеҺӢпјҢиҝҷж ·еҸҜд»Ҙдә§з”ҹдёҖдёӘClass Aз”өжөҒгҖӮиҝҷж ·еҸҜд»ҘеҮҸе°ҸдҝЎеҸ·иҫ“еҮәзҡ„еӨұзңҹеҗҢж—¶еҸҲдёҚеҪұе“Қз”өи·Ҝзҡ„йў‘зҺҮе“Қеә”гҖӮйҖҡеёёпјҢеўһеҠ дёҖдёӘClassAдёӢжӢүз”өжөҒпјҲ<5mAпјүеҸҜд»Ҙжҳҫи‘—зҡ„ж”№е–„е·®еҲҶдҝЎеҸ·дёӯзҡ„дёүйҳ¶и°җжіўеӨұзңҹгҖӮдёҚиҝҮпјҢиҝҷз§Қй«ҳйҳ¶и°җжіўеӨұзңҹеңЁе·®еҲҶжһ¶жһ„дёӯжң¬жқҘе°ұжҜ”иҫғејұгҖӮ

гҖҖгҖҖVFAиҫ“еҮәз«Ҝзҡ„з”өеҺӢиҰҒйҖҡиҝҮдёҖдёӘдҪҺйҖҡж»ӨжіўеҷЁеҶҚйҖҒеҲ°CFAжӯЈеҗ‘иҫ“е…Ҙз«ҜгҖӮе®ғжҳҜз”ұдёҖдёӘ1k欧е§Ҷз”өйҳ»е’Ң0.1uFз”өе®№з»„жҲҗзҡ„гҖӮеҸҜд»Ҙжңүж•Ҳзҡ„ж»ӨйҷӨдҝЎеҸ·дёӯзҡ„еҷӘеЈ°пјҢ20欧е§Ҷз”өйҳ»еҸҜд»ҘйҷҚдҪҺзі»з»ҹQеҖјпјҢдҝқжҢҒзі»з»ҹзЁіе®ҡгҖӮ

гҖҖгҖҖж··йў‘еҷЁе’Ңиҝҗж”ҫд№Ӣй—ҙзҡ„LCж»ӨжіўеҷЁз”ЁдёҖдёӘз”өйҳ»RgеҒҡз«ҜжҺҘгҖӮйҖҡеёёпјҢеҰӮжһңиҝҗж”ҫжҳҜVFAпјҢиҝҷдёӘз«ҜжҺҘз”өйҳ»дјҡеҜјиҮҙж»ӨжіўеҷЁйҖҡеёҰд№ӢеӨ–иҝҗж”ҫвҖңиҷҡең°вҖқзӮ№зҡ„зӯүж•Ҳйҳ»жҠ—еўһеӨ§гҖӮдҪҶжҳҜпјҢеҰӮжһңз”ЁCFAпјҢе°ұдёҚдјҡз”ЁиҝҷдёӘй—®йўҳгҖӮCFAејҖзҺҜеўһзӣҠдјҡеңЁ300MHzе·ҰеҸідёӢйҷҚпјҢеҸҚеҗ‘иҫ“е…Ҙз«Ҝдҫқ然еҸҜд»ҘдҝқжҢҒдҪҺйҳ»жҠ—пјҢеӣ дёәCFAеҶ…йғЁжңүејҖзҺҜbufferй©ұеҠЁиҫ“е…Ҙзә§пјҢеҸҜд»ҘдҝқжҢҒиҫ“е…Ҙзә§зҡ„дҪҺйҳ»жҠ—гҖӮиҝҷдәӣbufferзҡ„еёҰе®ҪеӨ§дәҺ1.5GHzпјҢжүҖд»ҘеҚідҪҝдҝЎеҸ·йў‘зҺҮй«ҳдәҺCFAеёҰе®ҪпјҢиҙҹиҫ“е…Ҙз«Ҝдҫқ然еҸҜд»ҘдҝқжҢҒдҪҺйҳ»жҠ—гҖӮ

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·