完成VCO后根据所选路的PLL频率合成芯片设计环路滤波器。PLL频率合成芯片MB15E03SL是Fujitsu公司生产的串行输入吞脉冲PLL频率合成器,最高支持1.2 GHz的工作频率,内部集成了低噪声数字鉴相器,可设置双模比例因子M/M+1,14 bit可编程参考分频比R及18 bit的可编程N分频器,芯片提供非常简单的三线SPI串行输入设定上述各项参数得到所需频率,输出频率计算式为

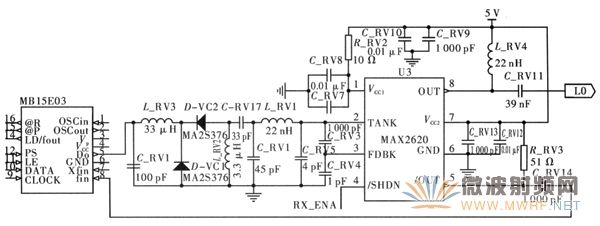

MB15E03SL其他参数详见数据手册,锁相环频率合成器设计原理图,如图4所示。

图4 本振锁相环电路原理图

根据系统要求:信道间隔12.5 kHz,容差±2 ppm,锁定时间<4 ms,根据文献[2]计算得环路带宽必须满足Fc≥1.6 kHz。由于增大环路带宽可以减小锁定时间,而环路太宽则会严重影响相位噪声,并且一般要求Fc不超过比较频率FPD的1/5,选择Fc=2.5.kHz。在VCO调制灵敏度等于20 MHz/V,电荷泵增益选择为Kφ=±1.5 mA,比较频率fPD=1 2.5 kHz,输出频率范围为420~470 MHz,环路滤波带宽Fc=2.5 kHz,相位裕量φ=48°,环路滤波极点比T3/T1=45%,参考输入频率13 MHz的条件下计算环路滤波器的各项参数。得到环路滤波器参数为:R_LF1=3.3 kΩ,R_LF2=5.6 kΩ,C_LF1=4.7 nF,C_LF2=47 nF,C_LF3=2.2 nF 。理论计算结果表明,在此环路条件下锁相环锁定时间Lock-time=1.3 ms,相位噪声能达到PN=-94.07 dBe/Hz@10kHz,环路带宽Fc=2.56 kHz,相位裕量为39.52°,已经能够达到系统需求,根据此环路滤波条件建立调频锁相环原理图,如图4所示。图5为锁相环430 MHz时的杂波测试图。

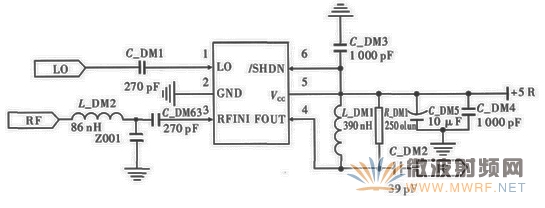

(3)下变频混频器电路设计。

Maxim公司的MAX2680是一低功耗、低噪声系数,专门适用于低电压操作的下变频混频器。它的适用频率为400~2 500 GHz,供电电压为2.7~5.5 V,具有较高的三阶输入截止点(IIP3在2 450 MHz)和<0.1μA的低功率关闭模式,是手持通信设备的理想器件,因此本设计采用此芯片。电路设计,如图5所示。

图5 430MHz载频处参考杂波

本接收机采用两次下变频进行鉴频,MAX2680为第一次下变频,产生一个45.05 MHz的中频信号。/SHDN为开关控制使能端,当为低电平时芯片不工作,当为高电平时芯片正常工作。接收的RF信号范围为400~450MHz,满足MAX2680的适用范围,本振信号L0由锁相环混频器产生。理论上,当RF为400 MHz,L0为445 MHz时,混频的增益为11 dB;而实际测量:当RF为405 MHz,功率为-48 dBm,L0为450.05 MHz,功率为-16 dBm时,输出IF为45.05 MHz,功率为-54 dBm。满足后续模块(鉴频芯片TA31136对输入信号的要求)对功率信号的要求。

图6 下变频混频器原理图

(4)鉴频器的电路设计。

TA31136是一个低电压操作的FM中频检测芯片,它主要适用于无线电话机中。TA31136的工作电压为1.8~5.5 V,它内部包含了一个输入中频信号为10~100 MHz的2ndIF混频器,一个噪声检测电路、一个高增益的限幅中频放大器和一个陶瓷,中周均可适用的积分鉴频器,另外该芯片还具有RSSI功能。由于该接收机采用两次下变频鉴频,第二次下变频和鉴频均可在TA31136中实现,因此本设计采用该鉴频芯片,鉴频器电路设计,如图7所示。

粤公网安备 44030902003195号

粤公网安备 44030902003195号