设计包含了估算与优化。估算可以对多个可能的实现选择做出比较。另外,优化可以自动完成,或者可以在各种抽象水平上,用工具辅助完成。Apache/Ansys应用工程总监Arvind Shanmugavel认为,只有当拥有了一个完整设计和一组正确的矢量时,功率估算才是一种精确的科学。在未完成设计以前,根据定义,所有事物都是一种即将在设计中发生的估计。在设计早期的功率预算阶段,应着眼于大的和相对的变化,而不是绝对的值。Atrenta公司的工程总监Venki Venkatesh认为,可以预期在RTL(寄存器传输级)到硅片之间有20%的偏差,而从门到硅片有10%的偏差。

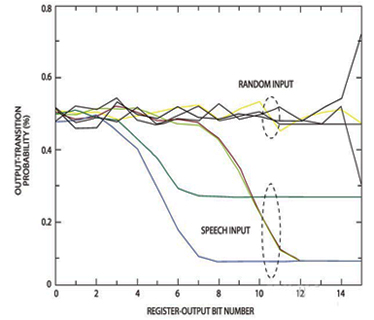

如果某个工具表示, 一种可能的方案会较另一种方案消耗更少的总能量,则这种概述一定是正确的;否则,工具就可能促使选择了次级的方案。与面积和性能不同,功率是矢量相关的,因此可能需要运行多次仿真,来获得有关设计活动的一种典型性样本。例如,考虑两种选择,一种是为音频处理器加随机数据,一种是用更多的典型语音数据。图2给出了一个有限脉冲响应滤波器中几个寄存器的转换动作(参考文献1)。对于一个不会破坏数据相关性的架构,语音数据开关电容的次数要比随机输入数据少80%。由于这些临时的相关性,运行顺序可能造成切换动作的巨大差异。

图2,对于一个不会破坏数据相关性的架构,语音数据开关电容的次数要比随机输入数据少80%。由于这些临时的相关性,运行顺序可能造成切换动作的巨大差异。

不过, 有些公司认为可以用统计方法获得近似值, 即采用来自计数器或其它可识别逻辑片的预期活动。现在, 功耗优化有很多种方式,大多数为RTL或以下。Shanmugavel称,时钟门控是尽量减少动态功耗的常见技术。切断某个电路的时钟,可阻止一个设计中时钟或寄存器的切换动作。另一种技术是采用电压岛,它降低了设计的工作电压,从而使开关元件的动态功耗前后比值为电压前后比值的平方。设计者将电压岛用于芯片的某些区域,这些区域的性能与速度不是关键,这样可以节省功耗。

DVFS(动态电压/频率缩放)是迄今最为复杂的动态功率控制技术。这种方法会根据负载的需求,改变有效工作电压和频率。在高负载情况下,电压与频率处于额定状态,芯片或设备为满负荷工作。在低负载情况下,电压或频率缩减,以低速工作,从而获得了较低的动态功耗。设计者可通过软硬件方案的组合,实现这种技术。

片芯上的稳压器满足了对多种动态与静态功率的需求。各IC通常有片外的稳压模块,可提供动态状态下需要的电压与电流。但是,设计者越来越多地采用片芯上的稳压器,因为电压域的数量在增加,这些电压域更快响应需求的要求也在增加。

堆叠IC间的相互通信尽量减少了信号互连,它是低功耗设计中一种新兴的趋势。Apache的Shanmugavel认为,制造商一般是将处理器和存储器堆叠在一个硅插入层上, 用TSV(硅通孔)做连接。这些插入层提供了片芯之间的低电容信号互连,从而降低了I/O的动态功耗。随着3D IC的成本开始下降,以及设计者对于热效应有了更多的理解,整个行业都将出现一个向3D IC的迁移。

要尽量减少静态功耗, 设计者可以采用电源门控方法,为一个待机状态的设备节省最多的泄漏功。关闭功能单位的时钟可降低动态功耗,但单元仍然有泄漏功耗。设计者必须在设计实现以前,了解有关电源门控的几个折中问题。

减少泄漏功耗的一种最古老技术是用高阈值电压门代换标称阈值电压的门。在CMOS中,亚阈值泄漏与阈值电压成反比。较高阈值电压器件的泄漏包络低于较小阈值电压的器件,但付出的代价是较大的延迟。设计者必须做一个仔细的权衡分析,才能用此技术获得最佳的减少泄漏效果。

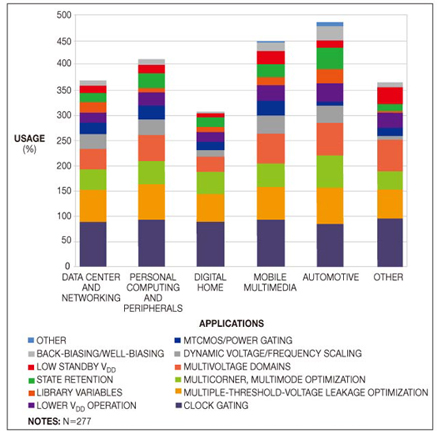

另外一种降低静态功耗的方法是有源反偏,它是增加CMOS门中基材结点的偏置电压,从而降低泄漏电流。这种偏置技术根本上是在待机模式期间增加一个单元或整个芯片的阈值电压,从而减少泄漏功耗。为了感受一下这些技术的采纳率,Synopsys通过自己的一个“全球用户调查”,收集了用户数据(图3)。

粤公网安备 44030902003195号

粤公网安备 44030902003195号