随着现代无线通信技术发展迅速,RF技术和射频器件深深根植于我们的生活,没有它们,现代文明可能就不会存在。对于无线电设计人员来说,前端设备的小型化、高性能以及高速数据吞吐量的技术要求给系统设计带来了巨大挑战。作为一家拥有涵盖整个RF领域的专门知识和技术的公司,亚德诺半导体(ADI)凭借广泛的RF、微波和毫米波解决方案的组合,以及深厚的系统设计专业知识,引领业界有效降低了RF和微波设计的复杂性,并降低了开发成本。本文将重点关注本振(LO)和时钟产生信号链,展示ADI如何降低设计复杂性并缩短开发时间,并让一般RF更好地为RF设计系统所用。

LO和时钟主信号链及时钟缓冲的备选应用案例

上图是一个相当典型的LO和时钟主信号链。左侧有参考时钟,其为LO或JESD函数生成解决方案提供参考源。顺着主信号路径,首先有超低相位噪声信号,它是LO或时钟产生解决方案的输出,通过该信号链中的可调谐滤波器——这里的可调谐滤波器用于移除信号源中存在的一些潜在谐波,可能会影响后续混频过程中的上下变频。之后,是一个低相位噪声放大器,该器件会尽最大努力为信号添加增益,但它会优化近载波或1/f相位噪声性能。这对于为混频器提供LO源以进行上下变频至关重要,因为放大器增加的额外相位噪声,特别是近载波相位噪声,最终会影响发射器的动态范围性能。因此,这里需要使用低相位噪声放大器来优化。随后,是一个开关,上图展示的是单刀双掷开关,但也可能要使用更多开关,比如四掷或八掷开关。开关可以用于校准信号,用于将信号路由到校准功能的另一个源,然后再次路由回来,例如送到混频器的LO源。请注意主路径上面时钟缓冲器所在的模块,这是一个备选应用案例。因为在更高速数据通信中,对数模和模数转换的要求使得采样速率越来越高。因此,系统需要提供非常高频率、极低抖动的时钟源,尤其是针对那些RF ADC。

ADI开发的很多技术都被用于LO产生和馈送混频器的PLL VCO技术,而且用于时钟产生使用场景。回到宽带频率覆盖,这是通用平台设计的关键点之一,ADI所做的宽带频率覆盖范围涵盖了整个LO和时钟信号链。每个器件的开发都是为了可以在很多情况下覆盖尽可能多的频率,同时保持良好的性能,从而创建通用平台设计,以便客户可以为不同频率的不同平台需求复用信号链。基于此,接下来我们看看ADI产品组合中的PLL和VCO以及PLL VCO集成技术。

在系统中实现LO生成有不同的方法。首先是分立VCO或电压控制振荡器,ADI提供了非常多的窄带和宽带VCO产品,例如带输出分频器的VCO HMC1160至HMC1169系列,该系列覆盖了8.45 GHz至14.07 GHz频率,其优点在于窄带,能够将相位噪声优化得尽可能低;HMC733是一款非常受欢迎的宽带10到20 GHz VCO,集成谐振器、负电阻器件和变容二极管,由于该器件采用单芯片结构,因此在温度范围内具有出色的输出功率和相位噪声性能,其扩展版ADF5709频率范围更宽,从9.85 GHz一直到20.5 GHz,在100 kHz偏置时保持83 dBc/Hz相位噪声,而无次谐波音,该器件宽频率调谐范围和低相位噪声支持适合各种频段的锁相环解决方案,同时限制了对多个窄带VCO的需求;四频段VCO HMC8074的优点是将VCO分为四个不同的窄带VCO,现在只能一次操作一个频段,但由于它是窄带,所以相位噪声非常低,本质上就是利用宽带器件实现了非常低的相位噪声,此外,这些器件内部有基波振荡器。因此没有内部倍频,不会产生不需要的子谐波音。

其次是锁相环(PLL),如果用户决定实现分立PLL和分立VCO,则需要上述提到的器件,ADI可以提供100多种PLL产品,有整数N分频PLL、小数N分频PLL,以及可同时提供整数N分频和小数N分频功能的PLL。HMC703是最受欢迎的8 GHz小数N分频PLL之一,该器件的优点之一就是提供雷达解决方案所必需的扫描功能。

当今更流行的方法是将PLL和VCO集成在一个封装中。传统单封装PLL VCO的缺点之一是内部存在倍频器,例如基波VCO核心为6.8 GHz,内部倍频器将其提升到13.6 GHz,这时此倍频器会插入不需要的次谐波。ADI提供的ADF4371和ADF4372内部集成了跟踪滤波器,这是业界的一项新技术,跟踪滤波器会消除内部倍频器产生的干扰次谐波。

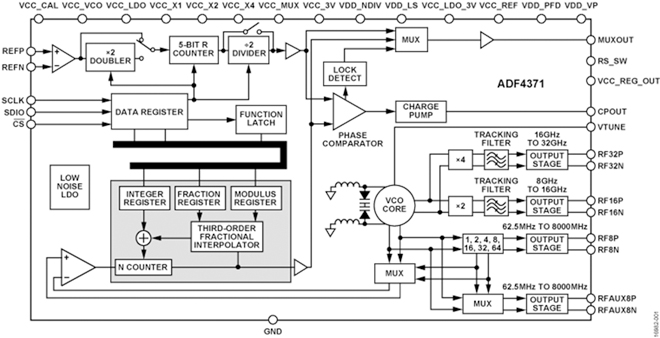

ADF4371是ADI最宽频段、最高频率的PLL VCO,集成到单个封装中,工作频率从62.5 MHz一直到32 GHz。除了宽带、高频率和跟踪滤波器之外,ADF4371还提供整数N分频和小数N分频工作模式,具有非常高的品质因数,PFD工作频率最高可达250 MHz。如果内部跟踪滤波器不能像用户期望的那样抑制内部倍频器所产生的次谐波,客户还可以使用可调谐带通滤波器系列来抑制谐波,例如搭配模拟受控可调谐带通滤波器ADMV8416/8420/8432,将其放在ADF4371的输出端,便可更好地抑制次谐波。ADF4372几乎与ADF4371相同,最大的不同是内部没有x4倍频器,而是一个x2倍频器,使频率提升到最多16 GHz。ADF4372的工作频率最低可达62.5 MHz。如果是不需要产生高于16 GHz的LO,建议使用ADF4372。

带集成 VCO 的微波宽带合成器ADF4371功能框图

ADI的另外一款高频PLL VCO是ADF5610,该器件是最低相位噪声的高频PLL VCO,与ADF4371和ADF4372的不同之处在于该器件内部没有跟踪滤波器,所以其次谐波抑制性能要弱一些,不过搭配ADMV8416或ADMV8420可以提高该性能的表现。ADF5610的优势在于它能在小数和整数模式下工作。与ADF4371和ADF4372相比,可为客户提供更大的灵活性,并且还能输出更高的输出功率。更重要的一点是,ADF5610内部的PLL引擎实际上是基于HMC703/704系列,如果用户拥有使用HMC703/704的经验,那么迁移到ADF5610就很容易。

针对降低设计复杂性和缩短开发时间的目标,在LO和时钟主信号链中如何选择LO生成的方法只是实现整个目标的一部分,ADI广泛的分立式VOC、PLL和集成VCO的PLL方案,为LO生成提供了不同的解决方案。与分立式混合型频率合成器/VCO配置相比,ADI集成VCO的PLL产品具有行业较领先的频率覆盖范围和性能,是微波/毫米波无线电、测试设备、微波传感器、光纤通信以及军事通信和传感器等许多小尺寸应用的理想之选。

粤公网安备 44030902003195号

粤公网安备 44030902003195号