иҪҜд»¶ж— зәҝз”өжҠҖжңҜдёҺеҸҜйҮҚй…ҚзҪ®и®Ўз®—дҪ“зі»з»“жһ„

1пјҺжҠҖжңҜи¶ӢеҠҝ

гҖҖгҖҖзҺ°д»Јж— зәҝйҖҡдҝЎзҡ„дё»дҪ“жҳҜ移еҠЁйҖҡдҝЎгҖӮеҸӮз…§ITUе»әи®®M1225пјҢ移еҠЁйҖҡдҝЎжҳҜеңЁеӨҚжқӮеӨҡеҸҳзҡ„移еҠЁзҺҜеўғдёӢе·ҘдҪңзҡ„пјҢеӣ жӯӨеҝ…йЎ»иҖғиҷ‘дёҘйҮҚзҡ„ж—¶еҸҳе’ҢеӨҡеҫ„дј ж’ӯзҡ„еҪұе“ҚгҖӮеңЁзҺ°д»Јж— зәҝйҖҡдҝЎзі»з»ҹдёӯпјҢзү№еҲ«жҳҜеңЁз ҒеҲҶеӨҡеқҖ(CDMA)зі»з»ҹдёӯпјҢдёәдәҶжҸҗй«ҳзі»з»ҹе®№йҮҸпјҢжҸҗй«ҳзі»з»ҹзҒөж•ҸеәҰе’ҢеңЁиҫғдҪҺзҡ„еҸ‘е°„еҠҹзҺҮдёӢиҺ·еҫ—иҫғиҝңзҡ„йҖҡдҝЎи·қзҰ»пјҢдёҖиҲ¬йғҪеёҢжңӣдҪҝз”ЁжҷәиғҪеӨ©зәҝдёҺиҒ”еҗҲжЈҖжөӢжҠҖжңҜгҖӮ

гҖҖгҖҖеңЁи®ёеӨҡе…¬ејҖеҸ‘иЎЁзҡ„жҠҖжңҜж–ҮзҢ®дёӯпјҢйғҪж¶үеҸҠеҲ°еҜ№жҷәиғҪеӨ©зәҝзҡ„жіўжқҹиөӢеҪўз®—жі•зҡ„з ”з©¶пјҢе…¶з ”з©¶з»“и®әжҳҜеҠҹиғҪи¶ҠејәеҲҷз®—жі•и¶ҠеӨҚжқӮгҖӮ然иҖҢеңЁз§»еҠЁйҖҡдҝЎзҺҜеўғдёӢпјҢиҒ”еҗҲжЈҖжөӢжҠҖжңҜе’ҢжіўжқҹиөӢеҪўжҳҜеҝ…йЎ»е®һж—¶е®ҢжҲҗзҡ„пјҢдё”е®ҢжҲҗз®—жі•зҡ„ж—¶й—ҙеҸӘиғҪд»Ҙеҫ®з§’и®Ўз®—гҖӮиҖҢеҸ—зҺ°д»Јеҫ®з”өеӯҗжҠҖжңҜж°ҙе№ізҡ„йҷҗеҲ¶пјҢеңЁеҰӮжӯӨзҹӯзҡ„ж—¶й—ҙеҶ…пјҢж•°еӯ—дҝЎеҸ·еӨ„зҗҶеҷЁ(DSP)жҲ–дё“з”ЁиҠҜзүҮ(ASIC)иҝҳдёҚиғҪе®һзҺ°иҝҮдәҺеӨҚжқӮзҡ„е®һж—¶еӨ„зҗҶгҖӮ

гҖҖгҖҖеҸҰдёҖж–№йқўпјҢ移еҠЁйҖҡдҝЎжҠҖжңҜе’Ңж ҮеҮҶиҝҳеңЁдёҚж–ӯжҸҗеҮәе’Ңжӣҙж–°пјҢиҪҜд»¶ж— зәҝз”өжҠҖжңҜж—ҘзӣҠеҸ—еҲ°й«ҳеәҰйҮҚи§ҶгҖӮзҫҺеӣҪFCCз”ҡиҮіеҸ‘ж–ҮиҰҒжұӮеҗ„е…¬еҸёеҜ№жӯӨжҠҖжңҜзҡ„еә”з”ЁжҸҗдҫӣж–№жЎҲгҖӮеҰӮдҪ•з”ЁDSPпјҲж•°еӯ—дҝЎеҸ·еӨ„зҗҶеҷЁпјүжҲ–FPGAпјҲзҺ°еңәеҸҜзј–зЁӢйҖ»иҫ‘йҳөеҲ—пјүзӯүе…¶д»–еҸҜзј–зЁӢеҷЁд»¶пјҢеңЁе…¬е…ұ硬件平еҸ°дёҠи§ЈеҶіеҗ„з§ҚдёҚеҗҢеҲ¶ејҸзҡ„з©әй—ҙжҺҘеҸЈе·ІжҲҗдёәеҫҲеӨҡдё–з•Ңеҗ„еӣҪйҖҡдҝЎе…¬еҸёз ”究зҡ„дё»иҰҒиҜҫйўҳгҖӮ

гҖҖгҖҖиҝҮеҺ»пјҢж— зәҝйҖҡдҝЎзі»з»ҹзҡ„и®ҫи®ЎеӨҡйҮҮз”ЁйқҷжҖҒи®ҫи®ЎпјҢеҸӘиғҪеңЁи§„е®ҡиҢғеӣҙеҶ…зҡ„зү№е®ҡйў‘ж®өдёҠдҪҝз”Ёдё“з”Ёи°ғеҲ¶еҷЁгҖҒзј–з ҒеҷЁе’ҢдҝЎйҒ“еҚҸи®®гҖӮеҚідҪҝжҳҜеҸҢйў‘гҖҒдёүйў‘иңӮзӘқз”өиҜқд№ҹеҸӘеңЁйў„е…Ҳе®ҡд№үзҡ„дёӨдёӘжҲ–дёүдёӘж ҮеҮҶд№Ӣй—ҙеҲҮжҚўгҖӮйқҷжҖҒи®ҫи®ЎйҖҡеёёжҳҜж №жҚ®жңҖеқҸжғ…еҶөзҡ„и®ҫи®ЎпјҢеңЁжғ…еҶөиүҜеҘҪж—¶е°ұдёҚиғҪе……еҲҶеҲ©з”Ёе°„йў‘йў‘и°ұгҖӮдҫӢеҰӮпјҢиӢҘиғҢжҷҜеҷӘеЈ°жҜ”жңҖжҒ¶еҠЈзҡ„жғ…еҶөе°ҸпјҢе°ұеҸҜиғҪеҮәзҺ°и®ёеӨҡдёҚеҝ…иҰҒзҡ„зә й”ҷзј–з ҒпјҢиҝҷж ·е°ұдёҚиғҪиҺ·еҫ—жңҖй«ҳзҡ„жҜ”зү№зҺҮгҖӮиҝҷз§Қжғ…еҶөеҜ№ж— зәҝеә”з”Ёзі»з»ҹзҡ„еҪұе“ҚжҜ”жңүзәҝеә”з”Ёзі»з»ҹжӣҙдёҘйҮҚпјҢеӣ дёәж— зәҝдј иҫ“жӣҙжҳ“дәҺеҸ—еҷӘеЈ°гҖҒе№Іжү°е’ҢиЎ°еҮҸзҡ„еҪұе“ҚгҖӮзҗҶжғізҡ„иҪҜд»¶ж— зәҝз”өиғҪеҠЁжҖҒйҖӮеә”дј иҫ“зі»з»ҹзҡ„д»»дёҖзҺҜиҠӮзҡ„еҸҳеҢ–пјҢеҰӮи°ғеҲ¶гҖҒзј–з ҒгҖҒдҝЎйҒ“еҚҸи®®еҸҠеёҰе®ҪпјҢзӯүзӯүпјҢ并иғҪеӨҹйҖӮеә”е®һж—¶жҖ§еҸҳеҢ–пјҢжңҖеӨ§зЁӢеәҰең°еҲ©з”Ёжңүж•Ҳйў‘и°ұгҖӮе·Іжңү专家预жөӢпјҢеңЁжңӘжқҘеҮ е№ҙеҶ…пјҢдҫқйқ дј з»ҹзҡ„дё“з”ЁиҠҜзүҮжқҘеҲ¶йҖ 移еҠЁйҖҡдҝЎж— зәҝи®ҫеӨҮзҡ„жҰӮеҝөе°ҶеҸ—еҲ°йҮҚеӨ§еҶІеҮ»гҖӮиҖҢдё”пјҢиҪҜд»¶ж— зәҝз”өдёҚд»…з”ЁдәҺз”ЁжҲ·з»Ҳз«ҜпјҢи§ЈеҶіеӨҡжЁЎжүӢжҢҒжңәзҡ„й—®йўҳпјҢе®ғиҝҳе°ҶдҪҝз”ЁдәҺж— зәҝеҹәз«ҷгҖӮзү№еҲ«жҳҜеңЁз¬¬дёү代移еҠЁйҖҡдҝЎжҠҖжңҜе’Ңж ҮеҮҶйғҪиҝҳеңЁдёҚж–ӯжӣҙж–°зҡ„жңҖиҝ‘еҮ е№ҙеҶ…пјҢеҸӘжңүдҪҝз”ЁиҪҜд»¶ж— зәҝз”өжҠҖжңҜпјҢжүҚеҸҜиғҪдҪҝдә§е“Ғи·ҹдёҠжҠҖжңҜзҡ„еҸ‘еұ•пјҢ并йҖӮеә”дёҚеҗҢзҡ„ж ҮеҮҶе’ҢзҺҜеўғгҖҒзҪ‘з»ңйҖҡдҝЎиҙҹиҚ·пјҢд»ҘеҸҠз”ЁжҲ·йңҖжұӮзҡ„еҸҳеҢ–гҖӮ

гҖҖгҖҖеңЁзҺ°йҳ¶ж®өиҪҜд»¶ж— зәҝз”өз»“жһ„дҪ“зі»зҡ„жһ„е»әдёӯпјҢе·Іжңүз ”з©¶иЎЁжҳҺеҸҜзј–зЁӢйҖ»иҫ‘еҷЁд»¶е…·жңүиҫғеҘҪзҡ„жҖ§иғҪпјҢе°Өе…¶жҳҜй’ҲеҜ№й«ҳ并иЎҢжҖ§иҝҗз®—жҜ”зӣ®еүҚе№ҝжіӣдҪҝз”Ёзҡ„DSPеңЁжҖ§иғҪдёҠе…·жңүжҳҺжҳҫзҡ„дјҳеҠҝпјҢеүҚиҖ…дёҚдҪҶеҸҜд»ҘжҸҗй«ҳиҝҗз®—йҖҹеәҰпјҢжӣҙйҮҚиҰҒзҡ„жҳҜе®ғеҸҜйҖҡиҝҮжңүж•ҲиҖҢзҒөжҙ»зҡ„и®ҫи®Ўж–№жі•жҸҗй«ҳзі»з»ҹ硬件зҡ„ж•ҙдҪ“е·ҘдҪңж•ҲзҺҮпјҢеҚіе°ҪеҸҜиғҪдҪҝзі»з»ҹдёӯжүҖжңүйҖ»иҫ‘иө„жәҗеӨ„дәҺжңүж•Ҳе·ҘдҪңзҠ¶жҖҒпјҢйҷҚдҪҺзі»з»ҹеҠҹзҺҮгҖӮиҝҷжҳҜзӣ®еүҚдёҖдәӣдё“з”ЁиҠҜзүҮд»ҘиҮіDSPйғҪж— жі•жҜ”жӢҹзҡ„гҖӮ

2пјҺиҪҜд»¶ж— зәҝз”өжҠҖжңҜзҡ„е®һзҺ°е№іеҸ°

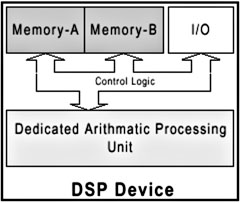

гҖҖгҖҖеңЁиҪҜд»¶ж— зәҝз”өжҠҖжңҜзҡ„е®һзҺ°дёӯпјҢзӣ®еүҚдё»жөҒзҡ„硬件жҠҖжңҜжҳҜйҖҡз”ЁдҝЎеҸ·еӨ„зҗҶеҷЁ(д»ҘDSPдёәд»ЈиЎЁ)е’ҢзҺ°еңәеҸҜзј–зЁӢйҖ»иҫ‘йҳөеҲ—(д»ҘFPGAдёәд»ЈиЎЁ)гҖӮиҷҪ然пјҢзҺ°йҳ¶ж®өдёӨз§ҚжҠҖжңҜдҪңдёәиҪҜд»¶ж— зәҝз”өе®һзҺ°е№іеҸ°иҝҳйғҪжңүеҗ„иҮӘзҡ„еұҖйҷҗжҖ§пјҢд»ҘдёӢеҜ№жҜ”дёӨз§ҚжҠҖжңҜеңЁе®һзҺ°иҪҜд»¶ж— зәҝз”өзҡ„дёҖдәӣзү№зӮ№пјҡ

гҖҖгҖҖз”ұдәҺиҪҜд»¶ж— зәҝз”өжҠҖжңҜеҹәеёҰи®ҫи®ЎдёӯеӨ§йҮҸдҪҝз”Ёд№ҳеҠ иҝҗз®—пјҢDSPеңЁе®ҢжҲҗиҝҷз§Қд№ҳеҠ иҝҗз®—ж—¶пјҢ дёҖиҲ¬йңҖиҰҒиҝӣиЎҢд»ҘдёӢж“ҚдҪңпјҡ

гҖҖгҖҖ1=>иҜ»еӯҳеӮЁеҷЁпјҢ еҸ–ж“ҚдҪңж•°пјҢеҸ–жҢҮд»Ө

гҖҖгҖҖ2=>иҝҗз®—

гҖҖгҖҖ3=>еҶҷеӯҳеӮЁеҷЁпјҢеӯҳеӮЁиҝҗз®—з»“жһң

гҖҖгҖҖдёәдәҶжҸҗй«ҳиҝҗз®—йҖҹеәҰпјҢдәә们дёҖиҲ¬еёҢжңӣеңЁдёҖдёӘжҢҮд»Өе‘ЁжңҹдёӯиғҪеӨҹеӨҡж¬ЎиҝӣиЎҢеӯҳеӮЁеҷЁиҜ»еҶҷж“ҚдҪңпјҢд»Ҙе°ҪйҮҸзј©зҹӯйқһиҝҗз®—ж—¶й—ҙгҖӮ

гҖҖгҖҖзӣ®еүҚDSPе№ҝжіӣйҮҮз”ЁдәҶе“ҲдҪӣз»“жһ„е’Ңж”№иҝӣзҡ„еҶҜ·иҜәдјҠжӣјз»“жһ„пјҢиғҪеӨҹж”ҜжҢҒеңЁдёҖдёӘжҢҮд»Өе‘ЁжңҹиҝӣиЎҢеӨҡж¬ЎеӯҳеҸ–ж“ҚдҪңпјҢиҝҷз§ҚдҪ“зі»з»“жһ„йҖӮз”ЁдәҺйқһе…іиҒ”жҖ§йЎәеәҸз®—жі•зҡ„е®һзҺ°гҖӮеҪ“йҮҮз”ЁдёҖдёӘеҸӘиғҪеҲҶж—¶иҝҗиЎҢзҡ„ж•°еӯ—дҝЎеҸ·еӨ„зҗҶеҷЁж—¶пјҢи°ғеәҰеӨҡдёӘж—¶й—ҙиҰҒжұӮзҙ§иҝ«зҡ„д»»еҠЎйңҖиҰҒйқһеёёеӨҚжқӮзҡ„зј–зЁӢгҖӮе°Өе…¶жҳҜпјҢеҪ“з®—жі•жЁЎеқ—е…іиҒ”еӨҡдёӘеҪ“еүҚе’ҢиҝҮеҺ»еҸҠжңӘжқҘзҡ„зҠ¶жҖҒж—¶пјҢDSPзҡ„ж•ҲзҺҮдёҚй«ҳгҖӮиҝҷдё»иҰҒжҳҜз”ұдәҺDSPеңЁеӨ„зҗҶдёҖдәӣ并иЎҢе’ҢеӣһйҰҲж•°жҚ®жөҒж—¶пјҢеӯҳеңЁйўқеӨ–зҡ„зӯүеҫ…ж—¶й—ҙгҖӮ

гҖҖгҖҖйҡҸзқҖйҖҡдҝЎжҠҖжңҜзҡ„еҸ‘еұ•пјҢеҜ№зі»з»ҹжҖ§иғҪзҡ„иҰҒжұӮд№ҹеңЁдёҚж–ӯеўһй«ҳпјҢиҖҢи®ҫи®Ўй«ҳжҖ§иғҪеӨҚжқӮDSPиҠҜзүҮзҡ„е‘ЁжңҹеҸҠеҚҠеҜјдҪ“е·Ҙиүәзҡ„еҸ‘еұ•иҝҳжІЎжңүи·ҹдёҠйңҖжұӮзҡ„еҸ‘еұ•гҖӮдәҺжҳҜпјҢеӨҚжқӮйҖҡдҝЎзі»з»ҹеҫҖеҫҖдҪҝз”ЁеӨҡзүҮDSPжқҘжҸҗй«ҳзі»з»ҹжҖ§иғҪгҖӮ

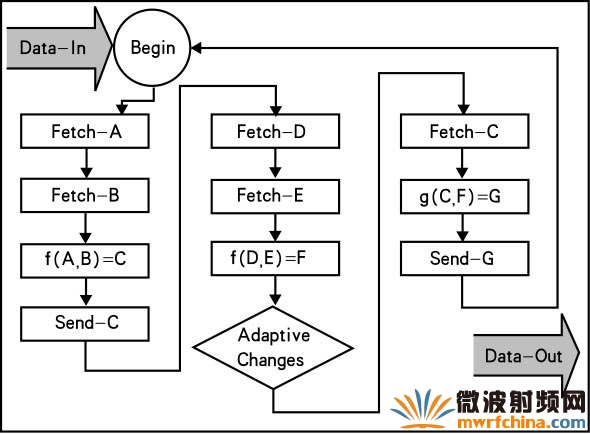

гҖҖгҖҖеҰӮеӣҫ2жүҖзӨәпјҢе…ёеһӢзҡ„дҝЎеҸ·еӨ„зҗҶз®—жі•дёҖиҲ¬еҢ…жӢ¬и®ёеӨҡеӣһйҰҲзҺҜи·Ҝе’Ң并иЎҢиҝҗз®—з»“жһ„гҖӮйҖҡз”ЁDSPе®һзҺ°иҝҷзұ»з®—жі•йҖҡеёёд»Јз Ғж•ҲзҺҮ并дёҚй«ҳгҖӮ

гҖҖгҖҖиҖҢз”ЁзҺ°еңәеҸҜзј–зЁӢй—ЁйҳөеҲ—(FPGA)е®һзҺ°дёҠиҝ°з®—жі•пјҢеҲҷеҸҜд»Ҙе…ӢжңҚдёҠиҝ°и®ҫи®Ўзҡ„дёҚи¶іпјҢиҝҷдё»иҰҒжҳҜз”ұдәҺFPGAжҸҗдҫӣдәҶжӣҙеӨ§зҡ„и®ҫи®ЎзҒөжҙ»жҖ§гҖӮз”ЁFPGAи®ҫи®ЎиҪҜд»¶ж— зәҝз”өж—¶е…·жңүи®ёеӨҡзӢ¬зү№зҡ„дјҳеҠҝпјҢдё»иҰҒдҪ“зҺ°еңЁпјҡ

гҖҖгҖҖ2.1 и®ҫи®ЎзҒөжҙ»жҖ§дёҺй«ҳжҖ§иғҪ

гҖҖгҖҖдёҺDSPзӣёжҜ”пјҢFPGAжңүжӣҙеӨ§зҡ„зҒөжҙ»жҖ§пјҢеҸҜж №жҚ®з®—жі•зү№зӮ№иҮӘе®ҡеҲ¶и®Ўз®—дҪ“зі»з»“жһ„пјӣеҲ©з”Ёе№¶иЎҢжҖ§и®Ўз®—и®Ўз®—дҪ“зі»з»“жһ„е’ҢеҗҲзҗҶзҡ„жөҒж°ҙзәҝи®ҫи®ЎеҸҜд»Ҙе®һзҺ°й«ҳз«ҜDSPеә”з”ЁпјҢдё”жҖ§иғҪжӣҙй«ҳгҖӮдҪҝз”ЁFPGAжһ„жҲҗеӨҡеӨ„зҗҶеҷЁи®Ўз®—дҪ“зі»з»“жһ„пјҢеҸҜе°ҶеҠҹиғҪжЁЎеқ—еҫҲе®№жҳ“жҳ е°„еҲ°зӢ¬з«Ӣе’Ң并иЎҢзҡ„硬件иҠӮзӮ№дёҠпјҢе®һзҺ°д»»ж„ҸеӨҡдёӘ并иЎҢж•°жҚ®еӨ„зҗҶи·Ҝеҫ„гҖӮйҒҝе…ҚдәҶйҮҮз”ЁдёҖдёӘеҸӘиғҪеҲҶж—¶иҝҗиЎҢзҡ„ж•°еӯ—дҝЎеҸ·еӨ„зҗҶеҷЁж—¶пјҢи°ғеәҰеӨҡдёӘж—¶й—ҙиҰҒжұӮзҙ§иҝ«зҡ„д»»еҠЎжүҖйңҖзҡ„йқһеёёеӨҚжқӮзҡ„зј–зЁӢгҖӮ

гҖҖгҖҖ2.2 еңЁзәҝйҮҚй…ҚзҪ®

гҖҖгҖҖзӣ®еүҚи®ёеӨҡFPGAиҠҜзүҮеҸҜдҪңеҲ°йғЁеҲҶеңЁзәҝйҮҚй…ҚзҪ®гҖӮжңҖж–°жҺЁеҮәзҡ„Xilinx Virtex-IIзі»еҲ—иҠҜзүҮе·Іе…·еӨҮд»ҘеҲ—дёәеҚ•дҪҚйғЁеҲҶйҮҚж–°й…ҚзҪ®зҡ„еҠҹиғҪпјҢиҝҷеҜ№дәҺжңӘжқҘи®ҫи®ЎеӨҡжЁЎзі»з»ҹе°ҶжҸҗдҫӣдҫҝеҲ©гҖӮе®һйҷ…дёҠпјҢChameleon е…¬еҸёзҡ„еҸҜйҮҚй…ҚзҪ®иҠҜзүҮеңЁжҰӮеҝөдёҠдёҺжӯӨжҳҜзұ»дјјзҡ„пјҢе®ғжҳҜзІ’еәҰжӣҙеӨ§зҡ„зҺ°еңәеҸҜзј–зЁӢйҖ»иҫ‘еҷЁд»¶пјҢжӣҙдҫҝдәҺи®ҫи®ЎдҪҝз”Ёе’ҢйҮҚй…ҚзҪ®гҖӮ

гҖҖгҖҖ2.3 еҲҶеёғејҸи®Ўз®—пјҲDAпјүжҠҖжңҜ

гҖҖгҖҖдәҢеҚҒеӨҡе№ҙеүҚе°ұжңүдәҶеҲҶеёғејҸи®Ўз®—пјҲDAпјүжҠҖжңҜпјҢе·Із»ҸиҜҒе®һе®ғдёҚйҖӮдәҺеҸҜзј–зЁӢDSPзҡ„е®ҡзӮ№жҢҮд»ӨйӣҶз»“жһ„гҖӮ然иҖҢпјҢDAйқһеёёйҖӮдәҺFPGAе®һзҺ°гҖӮз”ЁXilinx XC3000зі»еҲ—зҡ„FPGAи®ҫи®ЎDA FIRж»ӨжіўеҷЁж—©еңЁ1992е№ҙе°ұе·ІжҸҗеҮәгҖӮDAжҳҜдё“й—Ёй’ҲеҜ№д№ҳз§Ҝе’Ңж–№зЁӢзҡ„дёҖз§Қи®Ўз®—жҠҖжңҜпјҢж–№зЁӢдёӯзҡ„дёҖйЎ№д№ҳз§Ҝеӣ еӯҗжҳҜеёёж•°гҖӮDAи®ҫи®ЎеҸҜе®һзҺ°й—Ёзә§й«ҳж•ҲзҺҮгҖҒдёІиЎҢдҪҚз®—жі•еҸҠй«ҳжҖ§иғҪдҪҚ并иЎҢиҝҗз®—пјҢе®ғжҳҜз»Ҹе…ёзҡ„дёІ/并综еҗҲж–№жЎҲгҖӮDAжҠҖжңҜеҸҜеә”з”ЁдәҺеҫҲеӨҡйҮҚиҰҒзҡ„зәҝжҖ§гҖҒж—¶дёҚеҸҳж•°еӯ—дҝЎеҸ·еӨ„зҗҶз®—жі•пјҢеҰӮж»ӨжіўеҷЁ(FIRе’ҢIIR)гҖҒеҸҳжҚў(еҝ«йҖҹеӮ…з«ӢеҸ¶еҸҳжҚў[FFT])еҸҠзҹ©йҳөеҗ‘йҮҸд№ҳз§ҜпјҢеҰӮ8×8зҰ»ж•ЈдҪҷејҰеҸҳжҚў(DCT)гҖӮ

гҖҖгҖҖ2.4 еҲҶеёғејҸеӯҳеӮЁеҷЁжҠҖжңҜеўһеӨ§дәҶж•°жҚ®еёҰе®Ҫ

гҖҖгҖҖеҲҶеёғејҸеӯҳеӮЁеҷЁжҠҖжңҜжҳҜеҲ©з”ЁFPGAеҶ…йғЁзҡ„LUTжһ„жҲҗзҡ„еӯҳеӮЁеҚ•е…ғпјҢдёҺеқ—еӯҳеӮЁеҷЁзӣёжҜ”пјҢе®ғжӣҙжҳ“дәҺж №жҚ®дёҚеҗҢзҡ„з®—жі•з»“жһ„иҝӣиЎҢиЈҒеҮҸпјҢдҫҝдәҺ并иЎҢз®—жі•зҡ„и®ҫи®Ўе®һзҺ°гҖӮе°ҶеҲҶеёғејҸеӯҳеӮЁеҷЁжҠҖжңҜдёҺеҲҶеёғејҸи®Ўз®—пјҲDAпјүжҠҖжңҜз»“еҗҲиө·жқҘеҸҜд»Ҙе®һзҺ°й«ҳжҖ§иғҪиҝҗз®—гҖӮ

гҖҖгҖҖ2.5 жөҒж°ҙзәҝжҠҖжңҜ

гҖҖгҖҖйҮҮз”ЁжөҒж°ҙзәҝжҠҖжңҜпјҢе°ҶеӨҚжқӮзҡ„иҝҗз®—еҲ’еҲҶеҲ°еӨҡдёӘж—¶й’ҹе®ҢжҲҗпјҢжҸҗй«ҳдәҶзі»з»ҹзҡ„жҖ»еӨ„зҗҶиғҪеҠӣпјҢиҖҢдё”йҮҮз”Ёиҝҷз§ҚжҠҖжңҜжүҖеҲ©з”Ёзҡ„иө„жәҗд»Јд»·жҳҜеҫҲе°Ҹзҡ„гҖӮ

гҖҖгҖҖ2.6 FPGAдёҺASICжҠҖжңҜзҡ„иһҚеҗҲи¶ӢеҠҝ

гҖҖгҖҖAltera зҡ„ExcalibarеҶ…еөҢдәҶARM922TгҖҖ32дҪҚ RISCеӨ„зҗҶеҷЁпјҢXilinx зҡ„Virtex-II PROд№ҹеҶ…еөҢдәҶдёҖдёӘжҲ–еӨҡдёӘPowerPC(IBM405)зҡ„ж ё, йҷӨжӯӨд№ӢеӨ–пјҢеҶ…еөҢдёҚеҗҢж•°йҮҸзҡ„硬件д№ҳжі•еҷЁжҲ–д№ҳеҠ еҷЁзҡ„иҠҜзүҮе·Із»ҸеҸҜд»Ҙд№°еҲ°гҖӮ

гҖҖгҖҖ2.7 жЁЎеқ—еҢ–и®ҫи®Ў

гҖҖгҖҖ2000е№ҙ9жңҲXilinxе…¬еҸёжҺЁеҮәзҡ„Modular Designе·Ҙе…·дёәFPGAжЁЎеқ—еҢ–и®ҫи®ЎжӣҙжҸҗдҫӣдәҶдҫҝеҲ©пјҢжҸҗй«ҳдәҶи®ҫи®ЎйҮҚз”ЁжҖ§пјҢд№ҹжӣҙеҲ©дәҺеӣўйҳҹеҗҲдҪңеӨ§еһӢи®ҫи®ЎгҖӮ

гҖҖгҖҖ2.8 ж”ҜжҢҒеӨҡз§Қж ҮеҮҶжҖ»зәҝжҺҘеҸЈпјҢжӣҙжҳ“дәҺе®һзҺ°йҖҡ用硬件平еҸ°

гҖҖгҖҖеҰӮ600зҷҫдёҮй—Ёзҡ„FPGAе·Із»ҸйқўеёӮпјҢе®ғеҗҢж—¶ж”ҜжҢҒеӨҡз§Қж ҮеҮҶжҖ»зәҝжҺҘеҸЈпјҢеҰӮLVDS, LDT, CompactPCI, RapidIOзӯүгҖӮиҝҷе°ұж„Ҹе‘ізқҖжҲ‘们еҸҜиғҪд»Ҙжӣҙе°Ҹзҡ„жҺҘеҸЈи®ҫи®ЎејҖй”ҖжқҘиҺ·еҸ–жӣҙй«ҳзҡ„зі»з»ҹжҖ§иғҪгҖӮиҖҢйҮҮз”ЁеӨ§и§„жЁЎFPGAиҠҜзүҮдҪҝеҫ—и®Ўз®—еҚ•е…ғд№Ӣй—ҙзҡ„йҖҡдҝЎеҮҸе°‘пјҢжҸҗй«ҳдәҶзі»з»ҹзҡ„еҸҜйқ жҖ§гҖӮ

гҖҖгҖҖ2.9 еҠ еҜҶжҠҖжңҜ

гҖҖгҖҖXilinx Virtex-II зі»еҲ—FPGAеҶ…йғЁе·ІйӣҶжҲҗдәҶзүҮдёҠDESжҲ–triple DESеҠ еҜҶжҠҖжңҜпјҢе®ғжҳҜдёҖз§ҚеҜ№з§°еҠ еҜҶз®—жі•пјҢDESеҠ еҜҶеҜҶй’Ҙдёә56bit, д»ҺиҖҢдҪҝи®ҫи®Ўе…·жңүжӣҙеҘҪзҡ„дҝқеҜҶжҖ§гҖӮ

гҖҖгҖҖ2.11 ејәеӨ§зҡ„ж—¶й’ҹз»јеҗҲиғҪеҠӣ

гҖҖгҖҖж–°дёҖд»ЈVirtex-IIзі»еҲ—FPGAе…·еӨҮејәеӨ§зҡ„зі»з»ҹж—¶й’ҹз®ЎзҗҶзҡ„иғҪеҠӣпјҢ并йҮҮз”ЁDSS(ж•°еӯ—жү©йў‘жҠҖжңҜ)жңүж•ҲйҷҚдҪҺEMIгҖӮ

гҖҖгҖҖиҷҪ然FPGAеңЁе®һзҺ°еҚ·з§Ҝзј–з ҒеҷЁзӯүеӨҚжқӮйҖ»иҫ‘еҠҹиғҪдёҠе·Із»ҸжңүжҜ”иҫғжҲҗзҶҹзҡ„и®ҫи®ЎпјҢдҪҶеҹәдәҺжҖ§д»·жҜ”иҖғиҷ‘пјҢз”ЁFPGAе®һзҺ°еӨ§йҮҸеӨҚжқӮи®Ўз®—ж–№йқўзӣ®еүҚиҝҳжңүеҫҲеӨ§зҡ„зјәйҷ·гҖӮйҡҸзқҖеҲҶеёғејҸи®Ўз®—(DA)жҠҖжңҜзҡ„еә”з”ЁпјҢд»ҘеҸҠж—Ҙи¶ӢжҳҺжҳҫзҡ„FPGAдёҺASICжҠҖжңҜзҡ„иһҚеҗҲи¶ӢеҠҝпјҢз”ЁеҸҜйҮҚй…ҚзҪ®йҖ»иҫ‘еҷЁд»¶жһ„жҲҗиҪҜд»¶ж— зәҝз”өжҠҖжңҜе®һзҺ°е№іеҸ°е°ҶдјҡжҲҗдёәдёҚеҸҜйҖҶиҪ¬зҡ„и¶ӢеҠҝгҖӮ

3пјҺиҪҜд»¶ж— зәҝз”өи®Ўз®—дҪ“зі»з»“жһ„зҡ„еҲқжӯҘиҖғиҷ‘

гҖҖгҖҖеңЁиҪҜд»¶ж— зәҝз”өз»“жһ„дҪ“зі»зҡ„жһ„е»әдёӯпјҢеҹәеёҰдҝЎеҸ·еӨ„зҗҶеҷЁеёёеёёжңүйңҖиҰҒжұӮи§ЈеӨ§йҮҸеӨҡз»ҙзәҝжҖ§ж–№зЁӢз»„зҡ„иҝҗз®—пјҢиҝҷзұ»иҝҗз®—йҖҡеёёиҝӯд»ЈжҖ§иҫғй«ҳпјҢдәә们дёҖиҲ¬и®ӨдёәиҫғйҡҫдәҺеңЁзҺ°еңәеҸҜзј–зЁӢйҖ»иҫ‘йҳөеҲ—дёӯд»Ҙиҫғй«ҳзҡ„жҖ§иғҪд»·ж јжҜ”жқҘе®һзҺ°пјҢиҖҢеҖҫеҗ‘дәҺз”ЁDSPжқҘе®һзҺ°пјҢз”ұжӯӨпјҢдәә们дёҚеҫ—дёҚе°ҶдёҖдёӘе®Ңж•ҙзҡ„иҝҗз®—жЁЎеқ—еҲ’еҲҶжҲҗеӨҡдёӘиҝҗз®—еӯҗжЁЎеқ—пјҢеҚіеҜ№жҖ§иғҪиҰҒжұӮиҫғй«ҳзҡ„并иЎҢжҖ§иҝҗз®—ж”ҫеңЁFPGAдёӯе®һзҺ°пјҢиҖҢе°Ҷиҝӯд»ЈжҖ§иҫғй«ҳзҡ„иҝҗз®—ж”ҫеңЁDSPдёӯе®һзҺ°гҖӮз”ұжӯӨеёҰжқҘдәҶдёҖзі»еҲ—иҙҹйқўж•Ҳеә”пјҢжңҖзӘҒеҮәзҡ„е°ұжҳҜеўһеҠ дәҶжЁЎеқ—й—ҙж•°жҚ®йҖҡдҝЎжүҖеёҰжқҘзҡ„ејҖй”ҖпјҢйҷҚдҪҺдәҶзі»з»ҹжҖ§иғҪгҖӮеӣ иҖҢжңүеҝ…иҰҒж·ұе…Ҙз ”з©¶иҪҜд»¶ж— зәҝз”өи®Ўз®—дҪ“зі»з»“жһ„пјҢеӨ§е”җ移еҠЁзӯүе…¬еҸёе·ІжҠ•е…ҘеҲ°зӣёе…ізҡ„з ”з©¶дёӯпјҢ并жҸҗеҮәеӨҡйЎ№дё“еҲ©гҖӮз”ұдәҺж— зәҝйҖҡдҝЎдёӯдёҚж–ӯж”№иҝӣзҡ„жҖ§иғҪжӣҙй«ҳзҡ„жҷәиғҪеӨ©зәҝе’ҢиҒ”еҗҲжЈҖжөӢз®—жі•иҰҒжұӮжӣҙй«ҳзҡ„еҹәеёҰеӨ„зҗҶиғҪеҠӣе’ҢйҖҹеәҰпјҢзӣ®еүҚжҖ§иғҪжңҖй«ҳзҡ„ж•°еӯ—дҝЎеҸ·еӨ„зҗҶеҷЁ(DSP)жҲ–дё“з”ЁиҠҜзүҮ(ASIC)иҝҳдёҚиғҪе®һзҺ°иҝҮдәҺеӨҚжқӮзҡ„е®һж—¶еӨ„зҗҶгҖӮеӣ иҖҢжңүеҝ…иҰҒеҜ»жұӮжҖ§иғҪжӣҙй«ҳзҡ„并еҸҜд»ҘеңЁзәҝйҮҚй…ҚзҪ®зҡ„еӨ„зҗҶж–№жі•гҖӮ

гҖҖгҖҖз»јдёҠжүҖиҝ°пјҢдёәдәҶдҪҝ移еҠЁйҖҡдҝЎзі»з»ҹе…·жңүжӣҙй«ҳзҡ„е®№йҮҸе’ҢжӣҙеҘҪзҡ„жҖ§иғҪпјҢдёҖж–№йқўпјҢеҝ…йЎ»жүҫеҲ°дёҖз§Қз®ҖеҚ•дё”дҫҝдәҺе®һж—¶и®Ўз®—зҡ„з®—жі•пјҢеҸҰдёҖж–№йқўпјҢиҰҒжүҫеҲ°е®һж–ҪиҜҘз®—жі•зҡ„и®Ўз®—дҪ“зі»з»“жһ„пјҢеҰӮе®һж–Ҫиҝӯд»Јз®—жі•зҡ„ж–№жі•е’Ңи®Ўз®—дҪ“зі»з»“жһ„пјҢд»ҘдҫҝдәҺиҝӣдёҖжӯҘжҸҗй«ҳеҹәеёҰеӨ„зҗҶиғҪеҠӣпјҢ并иҺ·еҫ—иүҜеҘҪзҡ„ж•ҲжһңгҖӮ

еӨ§е”җ移еҠЁйҖҡдҝЎе…¬еҸё жұӘдёңиүі

ж‘ҳиҮӘ<<д»Ҡж—Ҙз”өеӯҗ>>

继з»ӯйҳ…иҜ»пјҡ

дәәе·ҘжҷәиғҪеә”з”ЁдәҺSDRзҡ„дҝЎеҸ·еҲҶжһҗзі»з»ҹ

еҲ©з”ЁејҖжәҗиҪҜд»¶ж— зәҝз”өSDR еә”еҜ№ж— дәәжңәеЁҒиғҒ

жҷәиғҪж— зәҝз”өжҠҖжңҜпјҲ3пјүпјҡиҪҜд»¶ж— зәҝз”өпјҲSDRпјүзҡ„ејҖеҸ‘е·Ҙе…·

жҷәиғҪж— зәҝз”өжҠҖжңҜпјҲ2пјүпјҡиҜҰи§ЈиҪҜд»¶ж— зәҝз”өпјҲSDRпјүжһ¶жһ„

жҷәиғҪж— зәҝз”өжҠҖжңҜпјҲ1пјүпјҡиҪҜд»¶ж— зәҝз”өе’Ңи®ӨзҹҘж— зәҝз”өзҡ„жҠҖжңҜжҰӮиҝ°еҸҠеә”з”Ё

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·