GNURadio 也处理数据的缓存。信号处理模块通常以它们被输入的速率来处理,但有时候因为 CPU 的处理速率或者其它因素,数据处理的速度不够快,就需要缓存(buffer)来缓冲。这就要求编程者要注意:当数据传送的速率大于处理速度时,有些缓存有可能会溢出并导致数据丢失;而当数据传送速率小于处理速度时,缓存经常是空的,有可能会产生脉冲。

GNURadio 除了支持 Linux 的多种发行版本外,还可移植到 Mac OS X 、NetBSD以及 Windows 等操作系统。

3.3 USRP 介绍

3.3.1 认知无线电对硬件平台的要求

从第二章 Simon Haykin 教授对认知无线电的理解中,可以看到,认知无线电系统对硬件方面有如下的要求:

(1)对多个频带信道进行监测

认知无线系统的收发器为了能够工作于不同的频段和提供宽带频谱感知能力,收发器的前端要能够调谐到大频谱范围内的任意频带,由此必须选用宽带天线。同时,根据电波传播条件设计天线,使之具有一定的极化或方向图分集控制能力。由于认知无线电能工作在不同的频段,对 A/D 转换器的要求也比较高,这就要求射频前端 A/D 转换器具有宽带、高频、高精度、高采样率、高分辨率、大动态范围的特性。

(2)具有一定的人工智能

认知无线电先对环境进行感知,再进行学习,最后达到决策,这过程是通过大量的算法实现的。因此,硬件平台应该具有运行和实现这些算法的载体,比如说 DSP,FPGA等,并且要对这些算法进行调度和控制。

(3)容易升级和扩展

认知无线电要求需要对多种频段进行支持,而各个频段的调制方式、数据传输数率、传输协议等都不同,这就要求该硬件平台能根据不同的实际情况,进行重新配置;另外,由于目前认知无线电的各种算法并不是很成熟,处于研究阶段,为了便于以后的系统升级,要求硬件平台可以重新配置,具备良好的扩展能力,如可以提供更多各类的接口等。

3.3.2 USRP 硬件结构分析

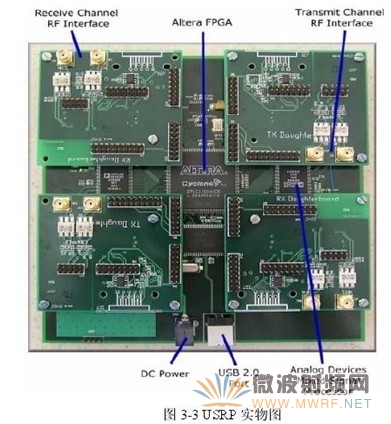

由Matt Ettus发明的硬件系统USRP 射频前端是GNU Radio最重要的硬件“伙伴” ,这个非常灵活的 USB 设备可以把我们的 PC 连接到 RF 世界。与 GNU Radio 软件相同,USRP 也是完全开放的,其所有的电路、设计文档和 FPGA 代码均可从 Ettus Research的站下载。它具有低成本、高效率等特点,是 GNU Radio 使用者的最佳选择。基于GNU Radio 和 USRP 的组合,用户可以构建各种具有想象力的软件无线电应用。

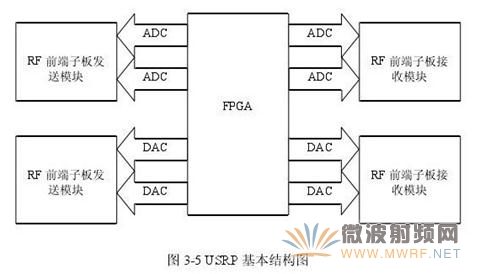

简易来说,USRP 就是一个集成电路板,它由一块主板和最多四块子板构成。USRP包含母板和前端子板。母板包含 4 个 12bit /64M 抽样率的 ADC,4 个 14bit/128M DAC,一个百万门的 FPGA 芯片 Altera Cyclone EP1C12 FPGA10 和一个可编程的 USB2.0 控制器,母板完成信号从模拟到数字的转换、基带信号的生成、与 PC 的通信的功能,它处理的是数字基带和中频信号。每个 USRP 母板支持 4 个子板,2 个接收,2 个发射。RF前端是实现在子板上的,不同的子板处理不同的频率带宽。现在可以覆盖从 DC 到5.9GHz 频段的信号。子板主要在中频上完成初步的滤波和信号混叠。

主板上面包含了 AD/DA 转换器以及 FPGA,主要完成中频采样以及中频信号到基带信号之间的互相转换。而子板主要是负责处理不同频带的射频信号,并进行射频、中频信号之间的转换。所有硬件部分的相关特性都是极为重要的,它们会很大作用地影响无线电设计、软件编程,使用时必须严格按照这些硬件的约束条件和要求来进行操作。

下面将分别介绍 USRP 各部件的相关功能:

(1)AD/DA 转换器

USRP采用两块 Analog Device 的 AD9862 芯片,这是美国模拟器件公司设计的、适合无线宽带通信应用的高性能混合信号前端。每块可提供两路 12bit、64M Sample/s 的AD 变换和两路 14bit、128M Sample/s 的 DA 变换。那么一块主板可提供 4 路模拟数字信号转换器(ADC)和 4 路的数字模拟信号转换器(DAC),也即收/发各两路的复采样。因此,从理论上讲,如果我们用实时采样的话,有四个输入、输出通道。然而,如果我们用复数(IQ)采样会更有灵活性。我们需要进行配对,因此可得到两组复数输入和两组复数输出。

AD9862的接收路径包括用在基带或低中频(IF)上接收多种数据或正交(I&Q)数据的两个高性能 ADC、输入缓冲器、接收端可编程增益放大器(RxPGA)和抽取滤波器。AD9862 还包含一个可编程的延迟锁定环路(DLL)时钟倍频器与集成定时电路(允许使用单个基准时钟)、辅助 ADC 和 DAC(用于对接收信号强度指示进行监视和控制)、温度传感器及增益与失调调整电路。

AD9862的发送路径允许接受多种数据格式并且包括两个高性能 DAC、发送端可编程增益放大器(TxPGA)、2 倍或 4 倍内插滤波器、一个希尔伯特(Hilbert)数字滤波器和用于复合或真实信号上变频的数字混频器。这些特点使系统结构从本质上减少了重构和抗混叠滤波要求。

注意到在 RX 板和 TX 板上的 PGA 都是可编程的,也就是说可以通过 GNU Radio调用 USRP 的相关函数来定义的。

(2)FPGA

明白 FPGA 的作用对 GNU Radio 的使用者来说是最重要的。USRP 采用一块型号为EP1C12 PQ240 的 FPGA,等效门数为 65 万门。它就像一个小的,高性能的并行计算机一样,可以完成所需的设计任务。设计 FPGA 需要一些技能,并且如果不慎还会烧坏硬件电路板。这里 USRP 的设计者提供了一个标准的适应性很广的 FPGA 配置。使用者在应用过程中不需做过多改动。

所有 ADC 和 DAC 都是连接到 FPGA 上,这块 FPGA 扮演的是主角,它要进行高带宽数学处理并降低数据速率以便数据能通过 USB 传到 PC 上处理。在接收通道上,FPGA 对 ADC 采进来的数字信号进行数字下变频 DDC,并通过层叠梳状滤波器 CIC 对数据进行可变速率的抽取。在发送通道上,原理是相同的,只不过要反过来进行。因为数字上变频 DUC 是在 AD9862 里进行的,FPGA 对数据进行的是梳状内插。

因为 FPGA 可以并行处理数据,所以 USRP 能实现全双工数据处理,在这种模式下,接收和发送两路是完全互相独立的。唯一需要注意的是收发复合的速率不能超32MByte/s。

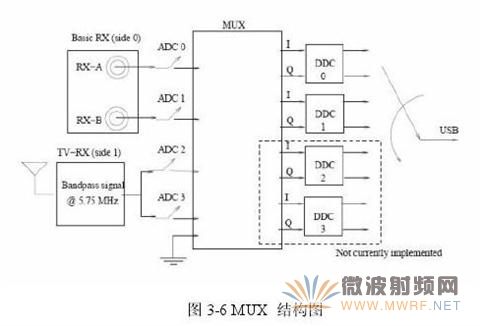

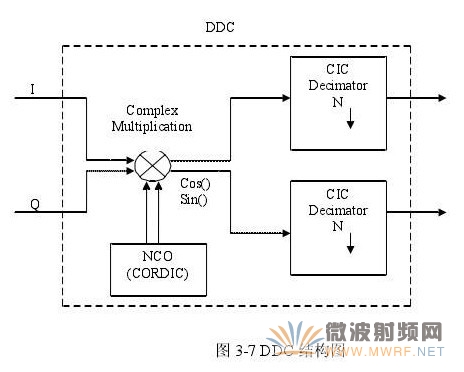

FPGA的两个主要功能:将 ADC 采来的中频信号进行数字下变频 (DDC) 变换到基带,并通过层叠梳状滤波器 CIC 对采样值进行可变速率的抽取以符合用户对信号带宽的要求。FPGA 包含有四个 DDC,每个 DDC 有 I 和 Q 两个输入口。ADC 的每一个输出都会被连接到四个 DDC 当中的一个 I 或者 Q 端口当中。这是由 MUX 来决定的。如下图所示,MUX 就像一个路由或者电路交换器,它决定哪个 ADC 输出连到哪个 DDC的输入端,这可以用 USRP 中的内部函数进行控制。

DDC能实现两个作用:首先,它把中频信号下变频到基带信号。其次,对信号抽取使信号速率能被 USB2.0 采用,并与 PC 的运算能力匹配。其结构图见图 3.5:

抽取器可认为是一个低通滤波器,后面紧接一个下采样器。假设抽取倍数是 N。如果我们看数字频谱,低通滤波器选出[-π/N,π/N]的频带,然后下采样器把频谱扩展到[-π,π]。扩展后的频谱成分与原来的频谱成分在[-π/N,π/N]是一一对应的,或者说前者可以准确地表示后者在[-π/N,π/N]的频率分量。所以,这时对扩展后的频谱进行处理等同于对原来信号频谱的处理,但前者的数据流率只有后者的 N 分之一,大大降低了对之后信号处理(解调分析等)速度的要求。

抽取之后的数据都是以 16 位有符号整数的 I/Q 信号形式通过 USB2.0 接口的,结果形成通过 USB2.0 的 8M Sample/s 的复数采样速率(参见下文有关 USB2.0 的说明)。

数字下变频之后,产生的 IQ 信号通过 USB 接口进入 PC,接下来就是软件编程的世界。

在发送路径,情况则是相反的。我们需要发送一个基带 IQ 信号到 USRP 板上。数字上变频器(DUC)会对信号进行修正,通过内插上变频到中频,最后发送到 DAC 进行模数转换。下来的工作交由子板完成,形成 RF 信号进行发送。

(3)前端子板

在母版上有四个插槽,总共能够被两个接收子板和两个发送子板使用,

粤公网安备 44030902003195号

粤公网安备 44030902003195号