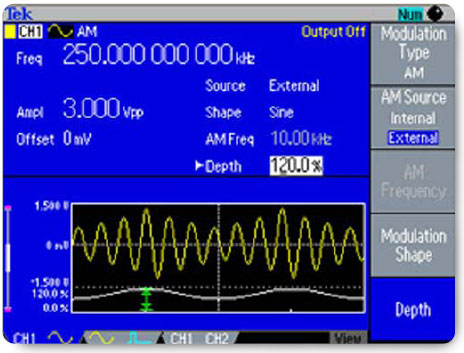

гҖҖгҖҖеңЁз”өеӯҗжөӢиҜ•е’ҢжөӢйҮҸдёӯпјҢз»ҸеёёиҰҒжұӮдҝЎеҸ·жәҗпјҢз”ҹжҲҗеҸӘжңүеңЁеӨ–йғЁжҸҗдҫӣж—¶жүҚдјҡжңүзҡ„дҝЎеҸ·гҖӮдҝЎеҸ·жәҗеҸҜд»ҘжҸҗдҫӣвҖңе·ІзҹҘиүҜеҘҪвҖқзҡ„дҝЎеҸ·пјҢжҲ–иҖ…еңЁе…¶жҸҗдҫӣзҡ„дҝЎеҸ·дёӯж·»еҠ еҸҜйҮҚеӨҚзҡ„ж•°йҮҸе’Ңзұ»еһӢе·ІзҹҘзҡ„еӨұзңҹ(жҲ–иҜҜз Ғ)гҖӮиҝҷжҳҜдҝЎеҸ·жәҗжңҖеӨ§зҡ„зү№зӮ№д№ӢдёҖпјҢеӣ дёәд»…дҪҝз”Ёз”өи·Ҝжң¬иә«пјҢйҖҡеёёдёҚеҸҜиғҪжҒ°еҘҪеңЁйңҖиҰҒзҡ„ж—¶й—ҙе’Ңең°зӮ№еҲӣе»әеҸҜйў„жөӢзҡ„еӨұзңҹгҖӮд»Һи®ҫи®ЎжЈҖйӘҢеҲ°жЈҖе®ҡпјҢд»ҺжһҒйҷҗе’ҢдҪҷйҮҸжөӢиҜ•еҲ°дёҖиҮҙжҖ§жөӢиҜ•пјҢдҝЎеҸ·жәҗеҸҜд»Ҙз”ЁдәҺж•°зҷҫз§Қеә”з”ЁгҖӮ

гҖҖгҖҖеӣ жӯӨпјҢжңүеӨҡз§ҚдҝЎеҸ·жәҗз»“жһ„еҸҜдҫӣйҖүжӢ©д№ҹе°ұдёҚи¶ідёәеҘҮдәҶпјҢиҖҢжҜҸз§Қз»“жһ„йғҪжңүеҗ„иҮӘзҡ„дјҳзӮ№гҖҒеҠҹиғҪе’Ңз»ҸжөҺжҖ§пјҢйҖӮз”ЁдәҺзү№е®ҡзҡ„з”ЁйҖ”гҖӮеңЁжң¬ж–ҮдёӯпјҢжҲ‘们е°ҶжҜ”иҫғдёӨз§ҚдҝЎеҸ·еҸ‘з”ҹз»“жһ„пјҡдёҖз§Қз”ЁдәҺд»»ж„ҸжіўеҪў/ еҮҪж•°еҸ‘з”ҹеҷЁдёӯпјҢдёҖз§Қз”ЁдәҺд»»ж„ҸжіўеҪўеҸ‘з”ҹеҷЁдёӯгҖӮйҖүжӢ©з»“жһңеңЁеҫҲеӨ§зЁӢеәҰдёҠеҸ–еҶідәҺеә”з”ЁгҖӮ

дәҶи§ЈдҝЎеҸ·еҸ‘з”ҹж–№жі•

гҖҖгҖҖд»»ж„ҸжіўеҪў/ еҮҪж•°еҸ‘з”ҹеҷЁ(AFG)йҖҡиҝҮиҜ»еҸ–еҶ…еӯҳзҡ„еҶ…е®№пјҢжқҘеҗҢж—¶еҲӣе»әеҮҪж•°жіўеҪўе’Ңд»»ж„ҸжіўеҪўгҖӮеӨ§еӨҡж•°зҺ°д»ЈAFG йҮҮз”ЁзӣҙжҺҘдҝЎеҸ·еҗҲжҲҗ(DDS)жҠҖжңҜпјҢеңЁе№ҝжіӣзҡ„йў‘зҺҮиҢғеӣҙдёҠжҸҗдҫӣдҝЎеҸ·гҖӮ

гҖҖгҖҖд»»ж„ҸжіўеҪўеҸ‘з”ҹеҷЁ(AWG)еҹәдәҺзңҹжӯЈеҸҜеҸҳж—¶й’ҹз»“жһ„(йҖҡеёёз§°дёә" зңҹжӯЈзҡ„arbs*1")пјҢйҖӮз”ЁдәҺеңЁжүҖжңүйў‘зҺҮдёҠз”ҹжҲҗжҜ”иҫғеӨҚжқӮзҡ„жіўеҪўгҖӮAWG д№ҹиҜ»еҸ–еҶ…еӯҳзҡ„еҶ…е®№пјҢдҪҶе…¶иҜ»еҸ–ж–№ејҸдёҚеҗҢ(еҗҺйқўиҝӣиЎҢдәҶд»Ӣз»Қ)гҖӮеӨ„зҗҶе…ҲиҝӣйҖҡдҝЎе’Ңи®Ўз®—еҚ•е…ғзҡ„и®ҫи®Ўдәәе‘ҳйҖүжӢ©AWGпјҢй©ұеҠЁйҮҮз”ЁеӨҚжқӮи°ғеҲ¶е’ҢеёҰжңүејӮеёёдәӢ件зҡ„й«ҳйҖҹдҝЎеҸ·гҖӮз»“жһңпјҢAWG еҚ жҚ®дәҶз ”з©¶гҖҒејҖеҸ‘е’Ңе·ҘзЁӢеә”з”Ёзҡ„жңҖй«ҳеұӮгҖӮ

гҖҖгҖҖиҝҷдёӨз§Қз»“жһ„еңЁжіўеҪўз”ҹжҲҗж–№жі•дёҠжңүзқҖеҫҲеӨ§е·®ејӮгҖӮжң¬жҠҖжңҜз®Җ

д»Ӣи®Ёи®әдәҶеҹәдәҺеҸҜеҸҳж—¶й’ҹзҡ„д»»ж„ҸжіўеҪўеҸ‘з”ҹеҷЁе’ҢеҹәдәҺDDSзҡ„д»»ж„ҸжіўеҪў/ еҮҪж•°еҸ‘з”ҹеҷЁд№Ӣй—ҙзҡ„е·®еҲ«гҖӮ

йҖҸиҝҮеүҚйқўжқҝпјҡжҜ”иҫғдёӨдёӘе№іеҸ°

AWGпјҡжҰӮеҝөз®ҖеҚ•пјҢзҒөжҙ»жҖ§жңҖеӨ§

гҖҖгҖҖе°Ҫз®ЎAWG еңЁиҝҷдёӨз§Қз»“жһ„дёӯжӣҙеҠ зҒөжҙ»пјҢдҪҶAWG зҡ„еә•еұӮжіўеҪўз”ҹжҲҗжҠҖжңҜйқһеёёз®ҖжҳҺгҖӮAWGзҡ„ж’ӯж”ҫж–№жЎҲеҸҜд»Ҙи§ҶдёәвҖңеҸҚеҗ‘еҸ–ж ·вҖқгҖӮ

гҖҖгҖҖиҝҷжҳҜд»Җд№Ҳж„ҸжҖқе‘ўпјҹзңӢдёҖдёӢдҝЎеҸ·еҸ–ж ·е№іеҸ°-- зӨәжіўеҷЁпјҢе®ғйҖҡиҝҮеңЁиҝһз»ӯж—¶зӮ№дёҠж•°еӯ—еҢ–жЁЎжӢҹдҝЎеҸ·зҡ„з”өеҺӢеҖјпјҢжқҘйҮҮйӣҶжіўеҪўпјҢе…¶еҸ–ж ·йў‘зҺҮеҸ–еҶідәҺз”ЁжҲ·йҖүжӢ©зҡ„ж—¶й’ҹйҖҹзҺҮгҖӮеҫ—еҲ°зҡ„ж ·зӮ№еӯҳеӮЁеңЁеҶ…еӯҳдёӯгҖӮ

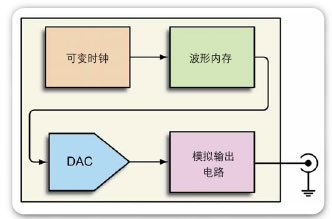

гҖҖгҖҖAWGзҡ„жөҒзЁӢзӣёеҸҚгҖӮAWGејҖе§Ӣж—¶жіўеҪўе·Із»ҸеңЁеҶ…еӯҳдёӯгҖӮжіўеҪўеҚ з”ЁжҢҮе®ҡж•°йҮҸзҡ„еҶ…еӯҳдҪҚзҪ®гҖӮеңЁжҜҸдёӘж—¶й’ҹе‘ЁжңҹдёӯпјҢд»ӘеҷЁд»ҺеҶ…еӯҳдёӯиҫ“еҮәеҸҰдёҖдёӘжіўеҪўж ·зӮ№гҖӮз”ұдәҺд»ЈиЎЁжіўеҪўзҡ„ж ·зӮ№ж•°йҮҸжҳҜеӣәе®ҡзҡ„пјҢеӣ жӯӨж—¶й’ҹйҖҹзҺҮи¶Ҡеҝ«пјҢиҜ»еҸ–еҶ…еӯҳдёӯжіўеҪўж•°жҚ®зӮ№зҡ„йҖҹеәҰи¶Ҡеҝ«пјҢиҫ“еҮәйў‘зҺҮи¶Ҡй«ҳгҖӮжҚўеҸҘиҜқиҜҙпјҢиҫ“еҮәдҝЎеҸ·йў‘зҺҮе®Ңе…ЁеҸ–еҶідәҺж—¶й’ҹйў‘зҺҮе’ҢеҶ…еӯҳдёӯзҡ„жіўеҪўж ·зӮ№ж•°йҮҸ*2гҖӮеӣҫ1 дёӯз®ҖеҢ–зҡ„ж–№жЎҶеӣҫжҰӮжӢ¬дәҶAWG з»“жһ„гҖӮ

гҖҖгҖҖAWG зҡ„зҒөжҙ»жҖ§жәҗиҮӘе…¶еҶ…еӯҳдёӯеӯҳеӮЁзҡ„жіўеҪўгҖӮжіўеҪўеҸҜд»ҘйҮҮеҸ–д»»дҪ•еҪўзҠ¶пјӣе®ғеҸҜд»Ҙжңүд»»ж„Ҹж•°йҮҸзҡ„з•ёеҸҳпјҢжҲ–ж №жң¬жІЎжңүз•ёеҸҳгҖӮеңЁеҹәдәҺPC зҡ„е·Ҙе…·зҡ„её®еҠ©дёӢпјҢз”ЁжҲ·еҸҜд»ҘејҖеҸ‘дәә们жғіеҫ—еҲ°зҡ„еҮ д№Һд»»дҪ•жіўеҪў(еңЁзү©зҗҶйҷҗеҲ¶еҶ…!)гҖӮеҸҜд»ҘеңЁд»ӘеҷЁиғҪеӨҹз”ҹжҲҗзҡ„д»»дҪ•ж—¶й’ҹйў‘зҺҮдёҠпјҢд»ҺеҶ…еӯҳдёӯиҜ»еҸ–ж ·зӮ№гҖӮдёҚз®Ўж—¶й’ҹжҳҜд»Ҙ1 MHzиҝҗиЎҢиҝҳжҳҜд»Ҙ1 GHzиҝҗиЎҢпјҢжіўеҪўзҡ„еҪўзҠ¶зӣёеҗҢгҖӮ

*1 е·ҘзЁӢеёҲйҖҡеёёдҪҝз”Ё"arb" жқҘжҢҮд»»дҪ•зұ»еһӢзҡ„д»»ж„ҸжіўеҪўеҸ‘з”ҹеҷЁгҖӮ

*2 еҪ“然任дҪ•AWG еһӢеҸ·йғҪжңүжңҖеӨ§еҶ…еӯҳе®№йҮҸгҖӮжіўеҪўеҚ з”Ёзҡ„ж·ұеәҰеҸҜиғҪиҰҒе°ҸдәҺе…ЁйғЁе®№йҮҸгҖӮ

AFG еңЁй«ҳйў‘дёӯйҮҮеҸ–й«ҳж•Ҳзҡ„еҝ«жҚ·ж–№ејҸ

гҖҖгҖҖAFGд№ҹдҪҝз”ЁеӯҳеӮЁзҡ„жіўеҪўпјҢдҪңдёәиҫ“еҮәдҝЎеҸ·зҡ„еҹәзЎҖгҖӮе…¶ж ·зӮ№иҜ»ж•°дёӯж¶үеҸҠж—¶й’ҹдҝЎеҸ·пјҢдҪҶз»“жһңзұ»дјјгҖӮ

гҖҖгҖҖAFG зҡ„ж—¶й’ҹд»ҘжҹҗдёӘеӣәе®ҡйҖҹзҺҮиҝҗиЎҢгҖӮз”ұдәҺжіўеҪўж ·зӮ№зҡ„ж•°йҮҸеңЁеҶ…еӯҳдёӯд№ҹжҳҜеӣәе®ҡзҡ„пјҢеӣ жӯӨAFG жҖҺж ·жүҚиғҪеңЁеҸҳеҠЁйў‘зҺҮдёҠжҸҗдҫӣжіўеҪўе‘ўпјҹдҫӢеҰӮпјҢжғіиұЎдёҖдёӢжӮЁжӯЈеңЁдҪҝз”ЁдёҖйғЁAFGпјҢе®ғеӯҳеӮЁз”ұ1000 дёӘж ·зӮ№з»„жҲҗзҡ„жіўеҪўпјҢд»Ҙ1 MHz зҡ„еӣәе®ҡйҖҹзҺҮиҫ“еҮәгҖӮиҫ“еҮәдҝЎеҸ·зҡ„е‘Ёжңҹе°ҶжҒ°еҘҪеӣәе®ҡеңЁ1 ms (1kHz)гҖӮеҫҲжҳҺжҳҫпјҢеҚ•йў‘дҝЎеҸ·жәҗеңЁеӨ§еӨҡж•°еә”з”Ёдёӯз”ЁйҖ”жңүйҷҗгҖӮеӣ жӯӨпјҢDDS жҠҖжңҜжҸҗдҫӣдәҶдёҖдёӘи§ЈеҶіж–№жЎҲгҖӮеҹәдәҺDDSзҡ„д»ӘеҷЁдёҚиҜ»еҸ–жҜҸдёӘж ·зӮ№пјҢиҖҢжҳҜиҜ»еҸ–дёҚеҲ°1000 дёӘж ·зӮ№пјҢжқҘйҮҚе»әжіўеҪўгҖӮ

гҖҖгҖҖеӣҫ2 жҳҜе…ёеһӢзҡ„з®ҖеҢ–зҡ„AFG з»“жһ„пјҢе…¶дёӯеҢ…жӢ¬DDS ж®өгҖӮиҫ“еҮәдҝЎеҸ·з”ұж—¶й’ҹгҖҒд»ЈиЎЁзӣёдҪҚеҖјзҡ„еӯҳеӮЁзҡ„дәҢиҝӣеҲ¶ж•°еӯ—еҸҠжіўеҪўеҶ…еӯҳзҡ„еҶ…е®№жһ„жҲҗгҖӮ

гҖҖгҖҖеҰӮеүҚжүҖиҝ°пјҢAFGдҝқжҢҒеӣәе®ҡзҡ„зі»з»ҹж—¶й’ҹйў‘зҺҮгҖӮ360еәҰж—¶й’ҹе‘ЁжңҹеҲҶеёғеңЁжүҖжңүжіўеҪўж ·зӮ№дёӯпјҢDDS ж®өж №жҚ®жіўеҪўй•ҝеәҰеҸҠз”ЁжҲ·йҖүжӢ©зҡ„йў‘зҺҮиҮӘеҠЁзЎ®е®ҡзӣёдҪҚеўһйҮҸгҖӮ

гҖҖгҖҖй«ҳйў‘и®ҫзҪ®дјҡеҜјиҮҙеӨ§зҡ„зӣёдҪҚеўһйҮҸпјҢдҪҝAFG еңЁйҖҡиҝҮ360 еәҰе‘Ёжңҹж—¶иҝ…йҖҹеҗ‘еүҚи·іпјҢжҸҗдҫӣй«ҳйў‘дҝЎеҸ·гҖӮдҪҺйў‘еҖјеҜјиҮҙе°Ҹзҡ„еўһйҮҸпјҢи§ҰеҸ‘зӣёдҪҚзҙҜеҠ еҷЁд»ҘиҫғдҪҺзҡ„жӯҘй•ҝжӯҘиҝӣйҖҡиҝҮжіўеҪўж ·зӮ№пјҢ

з”ҡиҮідјҡйҮҚеӨҚеҗ„дёӘж ·зӮ№пјҢжһ„жҲҗ360еәҰпјҢз”ҹжҲҗйў‘зҺҮиҫғдҪҺзҡ„жіўеҪўгҖӮ

гҖҖгҖҖиҝҷдёҖеҶізӯ–иғҢеҗҺзҡ„ж•°еӯҰиҝҗз®—и¶…еҮәдәҶжң¬ж–Үзҡ„и®Ёи®әиҢғз•ҙгҖӮеҸҜд»Ҙиҝҷж ·и®ІпјҢAFGж №жҚ®иҮӘе·ұзҡ„еҶ…йғЁз®—жі•и·іиҝҮйҖүжӢ©зҡ„жіўеҪўж•°жҚ®зӮ№гҖӮз”ұдәҺзӣёдҪҚеўһйҮҸж–№жі•пјҢе®ғ并дёҚжҳҜеңЁжҜҸдёӘе‘ЁжңҹдёӯдёҖзӣҙи·іиҝҮзӣёеҗҢзҡ„ж ·зӮ№ж•°гҖӮAFGдёәз”ҹжҲҗеҸҳеҢ–зҡ„жіўеҪўе’Ңйў‘зҺҮжҸҗдҫӣдәҶдёҖз§Қеҝ«жҚ·ж–№ејҸпјҢдҪҶжңҖз»Ҳз”ЁжҲ·дёҚиғҪжҺ§еҲ¶и·іиҝҮе“Әдәӣж•°жҚ®зӮ№гҖӮ

гҖҖгҖҖиҝҷеҝ…然еҜ№иҫ“еҮәжіўеҪўдҝқзңҹеәҰйҖ жҲҗдёҖе®ҡзҡ„еҪұе“ҚгҖӮе…·жңүиҝһз»ӯеҪўзҠ¶зҡ„жіўеҪў(жӯЈејҰгҖҒдёүи§’еҪўзӯүзӯү)йҖҡеёёдёҚжҳҜй—®йўҳпјҢдҪҶеҸҜиғҪдјҡеҪұе“ҚеҪ“еүҚж•°еӯ—зҺҜеўғдёӯеёёи§Ғзҡ„еёҰжңүеҝ«йҖҹиҪ¬жҚўзҡ„дҝЎеҸ·пјҢеҰӮи„үеҶІе’Ңзһ¬еҸҳгҖӮдҫӢеҰӮпјҢеҒҮи®ҫеңЁж–°зҡ„з”өдҝЎдәӨжҚўжңәе…ғ件дёҠиҝӣиЎҢжһҒйҷҗжөӢиҜ•гҖӮжөӢиҜ•жіўеҪўжҳҜдёҖдёІдәҢиҝӣеҲ¶и„үеҶІпјҢе…¶дёӯдёҖдёӘи„үеҶІеңЁдёҠеҚҮжІҝдёҠжңүдёҖдёӘзһ¬еҸҳгҖӮеңЁжҹҗдәӣйў‘зҺҮдёҠпјҢDDSзӣёдҪҚеўһйҮҸеҸҜиғҪдјҡеҲҡеҘҪи·іиҝҮзһ¬еҸҳпјҢиҖҢдёҚдјҡдҪңдёәдҝЎеҸ·зҡ„дёҖйғЁеҲҶеңЁж—¶й’ҹдёӯиҫ“еҮәзһ¬еҸҳгҖӮеҜ№иў«жөӢеҷЁд»¶(DUT)пјҢдҝЎеҸ·зұ»дјјдәҺжІЎжңүе№Іжү°зҡ„и„үеҶІжөҒпјҢз”ұдәҺзјәе°‘д»»дҪ•е®һйҷ…вҖңжһҒйҷҗвҖқпјҢиҝҷз§ҚжһҒйҷҗжөӢиҜ•жҳҜж— ж•Ҳзҡ„гҖӮ

иЎЁ1. AFG дёҺAWG еҸ–ж ·зү№зӮ№жҜ”иҫғ

гҖҖгҖҖAFGз»“жһ„зҡ„е®һзҺ°жҲҗжң¬иҰҒдҪҺдәҺе…ЁеҠҹиғҪAWGе·Ҙе…·йӣҶгҖӮз»“жһңпјҢе®ғйқһеёёз»ҸжөҺпјҢеҸҜд»Ҙдҫӣеҗ„дёӘе·ҘзЁӢеёҲе’Ңз§‘з ”дәәе‘ҳдҪҝз”ЁгҖӮжӯӨеӨ–пјҢAFGжӢҘжңүжҹҗдәӣзӢ¬жңүзҡ„жҖ§иғҪдјҳеҠҝгҖӮйғЁеҲҶйўҶе…ҲеһӢеҸ·жӢҘжңүд»»дҪ•жіўеҪўеҸ‘з”ҹе№іеҸ°дёӯжңҖдјҳз§Җзҡ„йў‘зҺҮжҚ·еҸҳжҖ§пјҢеҚіиғҪеӨҹеңЁдёҚеҗҢйў‘зҺҮд№Ӣй—ҙе№іж»‘еҲҮжҚўпјҢиҖҢдёҚдјҡеңЁдҝЎеҸ·дёӯдә§з”ҹдёҚиҝһз»ӯзӮ№гҖӮ

иЎЁ1 жҰӮжӢ¬дәҶAFG е№іеҸ°е’ҢAWG е№іеҸ°зҡ„ж—¶й’ҹе’ҢеҶ…еӯҳзү№зӮ№гҖӮ

ж·ұе…Ҙз»ҶиҠӮ

гҖҖгҖҖдёәжӣҙеҘҪең°жҜ”иҫғAWGе’ҢAFGз»“жһ„пјҢжҲ‘们е°ҶиҝӣиЎҢз®ҖеҚ•зҡ„вҖңжЎҲдҫӢеҲҶжһҗвҖқгҖӮжҲ‘们е°ҶиҖғеҜҹиҝҷдёӨдёӘе№іеҸ°еӨ„зҗҶе®ҡд№үиҫ“еҮәжіўеҪўзҡ„ж ·зӮ№зҡ„ж–№ејҸгҖӮгҖҖ

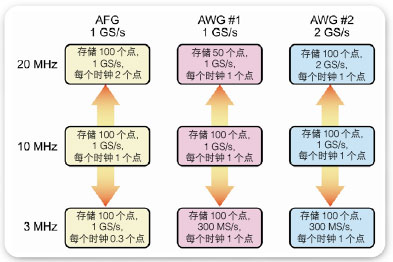

гҖҖгҖҖиҝҷдёҖжҜ”иҫғж¶үеҸҠдёүз§Қд»ӘеҷЁпјҡжңҖеӨ§еҸ–ж ·йҖҹзҺҮ1 GS/sзҡ„AFGпјӣжңҖеӨ§еҸ–ж ·йҖҹзҺҮ1 GS/sзҡ„AWG #1пјӣжңҖеӨ§еҸ–ж ·йҖҹзҺҮ2 GS/s зҡ„AWG #2гҖӮ

гҖҖгҖҖжҲ‘们зҡ„зӣ®ж ҮжҳҜеңЁ3 MHz - 20 MHz зҡ„йў‘зҺҮиҢғеӣҙеҶ…з”ҹжҲҗдёҖдёӘжӯЈејҰжіўгҖӮиҝҷдёӨеҸ°AWGе’ҢAFGйғҪеңЁ100зӮ№зҡ„еҸ–ж ·еҶ…еӯҳдёӯиЈ…жңүдёҖдёӘжӯЈејҰжіўе‘ЁжңҹгҖӮеӣҫ3жҳҫзӨәдәҶиҝҷдёүдёӘе№іеҸ°зҡ„зү№зӮ№жҖҺж ·еҪұе“Қе…¶д»»еҠЎеӨ„зҗҶж–№ејҸгҖӮ

гҖҖгҖҖиҝҷдёүз§Қе·Ҙе…·йғҪд»Ҙ1 GS/s зҡ„еҸ–ж ·йҖҹзҺҮиҜ»еҸ–100 дёӘзӮ№пјҢз”ҹжҲҗ10 MHz жӯЈејҰжіў(еӣҫ3 дёӯзҡ„дёӯй—ҙиЎҢ):

еӣҫ3. T з®ЎзҗҶиҫ“еҮәдҝЎеҸ·йў‘зҺҮзҡ„дёүз§Қж–№жі•гҖӮ

AFG зҡ„DDS еҚ•е…ғ收еҲ°е‘Ҫд»ӨпјҢеңЁиҫ“еҮәдёҠжҸҗдҫӣ10 MHzпјҢе®ғи®Ўз®—еҮә1 GS/s ж—¶й’ҹжҜҸж‘ҶеҠЁдёҖдёӢеўһеҠ 1 дёӘзӮ№гҖӮе®ғжҺҘи§ҰеҲ°100 дёӘж ·зӮ№дёӯзҡ„жҜҸдёӘзӮ№гҖӮ

дёӨдёӘAWGдёӯзҡ„ж—¶й’ҹйғҪиў«жүӢеҠЁи®ҫзҪ®дёә1 GS/sпјҢе®ғ们д№ҹиҜ»еҸ–100 дёӘзӮ№пјҢз”ҹжҲҗ10 MHz жіўеҪўгҖӮ

еңЁжҠҠиҫ“еҮәйў‘зҺҮи®ҫдёә3 MHz (еә•йғЁиЎҢ)пјҢе…¶ж–№жі•еҮәзҺ°еҲҶжӯ§пјҡ

AFG зҡ„ж—¶й’ҹд»Қд»Ҙ1 GS/s зҡ„еӣәе®ҡйҖҹзҺҮиҝҗиЎҢгҖӮдҪҶзҺ°еңЁпјҢDDSжҠҠеўһйҮҸиҮӘеҠЁи®ҫжҲҗж—¶й’ҹжҜҸж‘ҶеҠЁдёҖдёӢ0.3дёӘзӮ№пјӣд№ҹе°ұжҳҜиҜҙпјҢеҗ„дёӘж•°жҚ®зӮ№йҮҚеӨҚдёүж¬ЎжҲ–еӣӣж¬ЎгҖӮ

дёӨдёӘAWGдёӯзҡ„ж—¶й’ҹйў‘зҺҮеҝ…йЎ»жүӢеҠЁйҷҚеҲ°300 MS/sгҖӮж—¶

й’ҹзҺ°еңЁжӣҙж…ўең°иҜ»иҝҮж ·зӮ№пјҢз”ҹжҲҗ3 MHz зҡ„иҫ“еҮәйў‘зҺҮгҖӮ

зҺ°еңЁпјҢиҫ“еҮәйў‘зҺҮеҝ…йЎ»жҸҗй«ҳеҲ°20 MHzгҖӮиҝҷдёүдёӘе№іеҸ°д»ҘдёҚеҗҢж–№ејҸиҝҺжҺҘиҝҷдёҖжҢ‘жҲҳпјҡ

гҖҖгҖҖAFG зҡ„DDS еҚ•е…ғжҠҠеҸ–ж ·еўһйҮҸи®ҫдёәдёӨдёӘж ·зӮ№гҖӮе®ғжҜҸйҡ”дёҖдёӘж ·зӮ№иҜ»еҸ–дёҖдёӘж ·зӮ№пјҢе…ұдҪҝз”Ё50дёӘзӮ№е®ҡд№үжіўеҪўгҖӮе…¶й•ҝеәҰеҸӘжҳҜиҜ»еҸ–100дёӘзӮ№зҡ„дёҖеҚҠгҖӮз»“жһңжҳҜдёҖдёӘ20 MHzиҫ“еҮәдҝЎеҸ·гҖӮ

гҖҖгҖҖдёҺжүҖжңүAWG еңЁд»»дҪ•йў‘зҺҮи®ҫзҪ®дёҠдёҖж ·пјҢAWG #1 ж—¶й’ҹжҜҸж‘ҶеҠЁдёҖдёӢиҜ»еҸ–дёҖдёӘж ·зӮ№гҖӮдҪҶжҳҜпјҢз”ұдәҺе…¶жңҖеӨ§еҸ–ж ·йҖҹзҺҮжҳҜ1 GS/sпјҢеӣ жӯӨе®ғдёҚиғҪеңЁ50 ns зҡ„20 MHz жӯЈејҰжіўе‘ЁжңҹдёӯиҜ»еҸ–100дёӘзӮ№гҖӮеӣ жӯӨпјҢеҝ…йЎ»йҖҡиҝҮз”ЁжҲ·ж•…ж„Ҹе№Ійў„пјҢжҠҠеӯҳеӮЁзҡ„жіўеҪўеӣҫеғҸдёӢйҷҚеҲ°жҖ»е…ұ50 дёӘзӮ№гҖӮз»“жһңжҳҜдёҖдёӘ20 MHz иҫ“еҮәдҝЎеҸ·гҖӮ

гҖҖгҖҖе®ғжҸҗдҫӣдәҶеӨҡз§ҚиҪҜ件

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·