жҠ–еҠЁпјҢжҲ‘зҡ„зҗҶи§Је’ҢдёҖдәӣеҝ…еӨҮзҡ„еҹәжң¬жҰӮеҝө

з”ұдәҺдёҚж–ӯиҝҪжұӮжӣҙй«ҳзҡ„жҖ§иғҪпјҢжңүж•Ҳж•°жҚ®зӘ—зҡ„еҚ•дҪҚй—ҙйҡ”пјҲUIпјү继з»ӯзј©зҹӯгҖӮйҖҹзҺҮдёә1Gb/sж—¶пјҢUIдёә1000 psпјҢ5Gb/sзј©зҹӯдёә200 psпјҢ10Gb/sеҲҷдёә100 psгҖӮеҜ№дәҺ100 psзҡ„жңүж•Ҳж•°жҚ®зӘ—пјҢеҪ“зі»з»ҹжІЎжңүиҝһиҙҜиҖҢеҸҜйқ ең°еҸ‘йҖҒе’ҢжҺҘ收数жҚ®д№ӢеүҚпјҢеҸҜе®№еҝҚеҫҲе°Ҹзҡ„TjпјҲжҖ»жҠ–еҠЁпјүгҖӮд»ҘдёҠиҝ°йҖҹеәҰдј иҫ“ж—¶пјҢTjз»“жһңйңҖеӨ§еӨ§е°ҸдәҺ100psпјҢиҖҢRjпјҲйҡҸжңәжҖ§жҠ–еҠЁпјүеҸӘеңЁ1psзҡ„еӯҗеҢәй—ҙеҶ…гҖӮжңүд»Җд№ҲжҠҖжңҜе’Ңе·Ҙе…·иғҪз”ЁжқҘжЈҖе®ҡиҝҷдәӣйЈһз§’пјҲfsпјүзі»з»ҹе‘ўпјҹ

еҹәжң¬дёҠжқҘиҜҙпјҢйҡҸзқҖйҖҹеәҰзҡ„жҸҗй«ҳпјҢй«ҳйҖҹI/Oи®ҫи®ЎжҜ”д»ҘеҫҖйқўдёҙжӣҙеӨ§жҢ‘жҲҳгҖӮжңҖж–°зҡ„ж ҮеҮҶеӨҡж•°иҰҒжұӮеңЁзү©зҗҶеұӮзҡ„жҜ”зү№иҜҜз ҒзҺҮдёә10вҖ“12гҖӮ然иҖҢпјҢUIзҡ„йҖҗжёҗзј©е°ҸдҪҝдҝқжҢҒиҝҷж ·зҡ„иҜҜз ҒзҺҮеҸҳеҫ—и¶ҠжқҘи¶ҠйҡҫгҖӮеҲ°еӨҙжқҘпјҢиҝҷе°ұж„Ҹе‘ізқҖи®ҫеӨҮзә§жҠ–еҠЁиҰҒ继з»ӯзј©зҹӯгҖӮдҫӢеҰӮпјҢ5Gb/sзҡ„SuperSpeed USB规е®ҡRjдёә2.42ps RMSпјӣ10 Gb/sзҡ„SFP规е®ҡTjдёә28 psпјҢRjдёә1 psе·ҰеҸігҖӮ

е®ҡж—¶еҲҶжһҗ

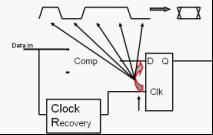

жүҖжңүйҮҮз”Ёз”өеҺӢеҸҳжҚўжқҘдҪ“зҺ°е®ҡж—¶жғ…еҶөзҡ„з”өж°”зі»з»ҹйғҪдјҙжңүи®ЁеҺҢзҡ„е®ҡж—¶жҠ–еҠЁгҖӮеҪ“дҝЎеҸ·еҸ‘йҖҒйҖҹзҺҮдёҚж–ӯжҸҗй«ҳпјҢз”өеҺӢж‘ҶеҠЁзј©е°Ҹд»ҘйҷҚдҪҺеҠҹиҖ—ж—¶пјҢзі»з»ҹзҡ„жҠ–еҠЁеңЁдҝЎеҸ·еҸ‘йҖҒй—ҙйҡ”дёӯеҚ еҲ°зӣёеҪ“еӨ§зҡ„жҜ”йҮҚгҖӮиҝҷз§Қжғ…еҶөдёӢпјҢжҠ–еҠЁжҲҗдёәеҹәжң¬жҖ§иғҪйҷҗеәҰгҖӮжҳҜеҗҰе…·жңүжҠ–еҠЁжЈҖе®ҡиғҪеҠӣпјҢеҜ№жҲҗеҠҹиҝҗз”Ёз¬ҰеҗҲжҖ§иғҪиҰҒжұӮзҡ„й«ҳйҖҹ第дёүд»ЈпјҲGen 3пјүзі»з»ҹиҮіе…ійҮҚиҰҒгҖӮеҰӮеӣҫ1жүҖзӨәпјҢжҜҸдёӘж—¶й’ҹзҡ„ж•°жҚ®зә§гҖҒдёҠеҚҮжІҝе’ҢдёӢйҷҚжІҝйғҪеңЁDеӨ„иЎЁзӨәеҮәжқҘгҖӮж•°жҚ®й”ҒеӯҳжҳҜж•°жҚ®йҖҡдҝЎзҡ„е…ій”®зҺҜиҠӮгҖӮе·Ҙе…·пјҲзӨәжіўеҷЁгҖҒд»ҝзңҹзі»з»ҹпјүдёҠпјҢд»ҘеҸҜи§ҒеӣҫеҪўзҡ„еҪўејҸжҳҫзӨәгҖӮеңЁжҜҸдёӘж—¶й’ҹдёҠпјҢиҫ№жІҝзҡ„е®ҡж—¶дҪҚзҪ®пјҲеҰӮжңүпјүжңүеҠ©дәҺж—¶й’ҹвҖ”ж•°жҚ®е»¶ж—¶з»ҹи®ЎеҲҶеёғгҖӮиҝҷз§ҚдҪҚ移еҚіжҠ–еҠЁжҲ–ж—¶й—ҙй—ҙйҡ”иҜҜе·®пјҲTime Interval Error or TIEпјүгҖӮ

еӣҫ1 дёІиЎҢж•°жҚ® дёӯзҡ„жҠ–еҠЁ

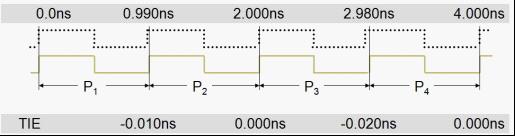

TIEжҠ–еҠЁжҳҜзӣёеҜ№е·ІзҹҘжҲ–е·ІжҒўеӨҚзҡ„ж—¶й’ҹжөӢйҮҸеҮәзҡ„дҝЎеҸ·е®ҡж—¶иҜҜе·®гҖӮеңЁдёІиЎҢж•°жҚ®зҡ„еә”з”ЁдёӯпјҢTIEйҖҡеёёз§°дёәжҠ–еҠЁгҖӮTIEеҫҲйҮҚиҰҒпјҢеӣ дёәе…¶з”ҡиҮіиғҪжҳҫзӨәдёҖж®өж—¶й—ҙеҶ…е°‘йҮҸжҠ–еҠЁзҡ„зҙҜз§Ҝж•Ҳеә”гҖӮд»Ҙеӣҫ2дёәдҫӢпјҢжҜҸжҜ«еҫ®з§’ж—¶й’ҹиҫ№жІҝзҡ„TIEж ҮеҮҶеҒҸе·®жҳҜ9.6 psгҖӮ

еӣҫ2 TIEжҠ–еҠЁжөӢйҮҸжңүе…¶д»–ж–№жі•жөӢйҮҸеҚ•жіўеҪўжҠ–еҠЁпјҢеҢ…жӢ¬е‘ЁжңҹжҖ§жҠ–еҠЁе’Ңcycle-to-cycleжҠ–еҠЁгҖӮ

е‘ЁжңҹжҖ§жҠ–еҠЁжҳҜеҜ№дҝЎеҸ·зҡ„жөӢйҮҸпјҢйҖҡеёёй’ҲеҜ№д»ҺдёҖдёӘиҫ№жІҝеҲ°еҸҰдёҖзӣёдјјиҫ№жІҝзҡ„еӨҚзӨәдҝЎеҸ·гҖӮеёёи§Ғзҡ„е‘ЁжңҹжөӢйҮҸе·Ҙе…·жөӢйҮҸжҹҗдёҖдҝЎеҸ·зҡ„дёҠеҚҮжІҝеҲ°дёӢдёҖдёҠеҚҮжІҝд№Ӣй—ҙзҡ„ж•°еҖјгҖӮйҮҮз”Ёж•°жҚ®дј иҫ“ж–№ејҸпјҲеҰӮDDR еҶ…еӯҳпјүпјҢеҗҢж—¶еҲ©з”ЁдёҠеҚҮжІҝе’ҢдёӢйҷҚжІҝжқҘи®°ж—¶ж•°жҚ®жҜ”зү№пјҢиҝҷж—¶жөӢйҮҸе‘Ёжңҹд»…дёәеҚҠдёӘе‘ЁжңҹгҖӮеңЁйҮҮйӣҶе‘ЁжңҹжөӢйҮҸеҖјзҡ„жңүж•Ҳж ·еҖјеҗҺпјҢеҸҜеҲҶиҫЁж ҮеҮҶеҒҸе·®е’Ңеі°еҖјгҖӮиҜҘз»ҹи®Ўж•°жҚ®еҚідҝЎеҸ·дёӯзҡ„е‘ЁжңҹжҖ§жҠ–еҠЁгҖӮ

еҜ№дәҺcycle-to-cycleжҠ–еҠЁпјҢйҖҡиҝҮеә”з”Ёз®ҖеҚ•з®—жңҜи®Ўз®—еҲҡеҲҡиҺ·еҸ–зҡ„е‘ЁжңҹжөӢйҮҸеҖјгҖӮеҰӮжһңе·ІзҹҘдёӨдёӘзӣёйӮ»е‘Ёжңҹзҡ„е®ҡж—¶ж•°жҚ®пјҢе…¶е·®еҖјдҫҝжҳҜcycle-to-cycleеҸҳеҢ–пјҡе‘Ёжңҹ1еҮҸеҺ»е‘Ёжңҹ2гҖӮжӯӨеӨ–пјҢеҸ–е‘Ёжңҹдёӯзҡ„жңүж•ҲзӨәиҢғе‘ЁжңҹпјҢ并жөӢйҮҸе‘Ёжңҹд№Ӣй—ҙзҡ„е·®еҖјеҗҺпјҢеҚіеҸҜеҫ—еҮәж ҮеҮҶеҒҸе·®е’Ңеі°еҖјгҖӮз»ҹи®ЎеҮәзҡ„ж•°жҚ®еҚіcycle-to-cycleвҖңжҠ–еҠЁвҖқгҖӮ

жҠ–еҠЁеҲҶйҮҸ

е°ҶжҠ–еҠЁеҲҶжҲҗеҗ„дёӘеҲҶйҮҸпјҢеҸҜжҸҗй«ҳзІҫеәҰгҖҒзңӢжё…BERжҖ§иғҪзҡ„ж №жәҗгҖӮжңҖеёёз”Ёзҡ„жҠ–еҠЁжЁЎеһӢеҹәдәҺеӣҫ3жүҖзӨәзҡ„еҲҶзә§з»“жһ„гҖӮиҷҪ然д№ҹжңүеҲҶжһҗжҠ–еҠЁзҡ„е…¶д»–ж–№жі•пјҢдҪҶиҝҷз§Қж–№жі•дёәT11 MJSQжүҖи®ӨеҸҜпјҢзӣ®еүҚжңҖдёәеёёз”ЁпјҢеӣ дёәе®ғзӣҙжҺҘжҳҫзӨәдёҺBERжҖ§иғҪзӣёе…ізҡ„еҲҶйҮҸгҖӮ

еӣҫ3 жҢүжҠ–еҠЁзұ»еһӢиҝӣиЎҢзҡ„жҠ–еҠЁеҲҶжһҗ

еңЁиҝҷз§ҚеҲҶзә§з»“жһ„дёӯпјҢйҰ–е…Ҳе°ҶжҖ»жҠ–еҠЁпјҲTjпјүеҲҶдёәдёӨзұ»пјҢеҚійҡҸжңәжҖ§жҠ–еҠЁпјҲRjпјүе’ҢзЎ®е®ҡжҖ§жҠ–еҠЁпјҲDjпјүпјҢ然еҗҺеҶҚе°ҶзЎ®е®ҡжҖ§жҠ–еҠЁеҲҶдёәиӢҘе№Ізұ»пјҡе‘ЁжңҹжҖ§жҠ–еҠЁпјҲPjпјҢжңүж—¶д№ҹз§°жӯЈејҰжіўжҠ–еҠЁSjпјүгҖҒеҚ з©әжҜ”жҠ–еҠЁпјҲDCDпјүд»ҘеҸҠж•°жҚ®зӣёе…іжҠ–еҠЁпјҲDDjпјҢд№ҹз§°з¬ҰеҸ·й—ҙе№Іжү°ISIпјүгҖӮжңүж—¶д№ҹйҮҮз”ЁеҸҰеӨ–зҡ„зұ»еҲ«пјҲжңүз•ҢдёҚзӣёе…іжҠ–еҠЁBUjпјүгҖӮ

еҰӮжһңиҰҒжөӢйҮҸеңЁй«ҳдҝЎеҸ·еҸ‘йҖҒйҖҹзҺҮж—¶жһ„жҲҗTjзҡ„еҗ„еҲҶйҮҸпјҢеә”йҮҮз”Ёжң¬еә•еҷӘеЈ°дҪҺгҖҒйў‘зҺҮе“Қеә”е№ізЁігҖҒжҠ–еҠЁжөӢйҮҸеә•йҷҗдҪҺе’Ңи§ҰеҸ‘жҠ–еҠЁе°Ҹзҡ„д»ӘеҷЁгҖӮдҫӢеҰӮпјҢ ON SemiconductorеҸ‘зҺ°еңЁжЈҖе®ҡе…¶й«ҳйҖҹECLи®ҫеӨҮж—¶пјҢйңҖйҮҮз”Ёзі»з»ҹжҠ–еҠЁ<200 fs RMSиҖҢдё”еёҰе®Ҫиҫғе®Ҫзҡ„д»ӘеҷЁгҖӮиҠҜзүҮи®ҫи®ЎиҖ…еҸ‘зҺ°еҮ дёӘpsжңҹй—ҙзҡ„дҝЎеҸ·з§»дҪҚпјҢз”ҡиҮіжҳҜеңЁfsиҢғеӣҙеҶ…зҡ„移дҪҚпјҢд№ҹдјҡе№Іжү°еҸ‘йҖҒпјҲTXпјүе’ҢжҺҘ收пјҲRXпјүжҖ§иғҪгҖӮ

еҖјеҫ—жіЁж„Ҹзҡ„жҳҜпјҢе°Ҫз®ЎеӨ§еӨҡж•°дёІиЎҢйҖҡдҝЎж ҮеҮҶйғҪеҜ№жҠ–еҠЁе®№е·®жҲ–жҠ–еҠЁйҷҗеҖјеҒҡеҮә规е®ҡпјҢдҪҶж ҮеҮҶжүҖйҮҮз”Ёзҡ„жҠҖжңҜеҸӮж•°иҫғдёәжЁЎзіҠпјҢжҲ–иҖ…еңЁеҲҶжһҗжҠ–еҠЁж—¶йҮҮз”ЁдәҶдёҚеҗҢзҡ„еҹәжң¬еҺҹзҗҶгҖӮж ҮеҮҶж–Ү件еҖҫеҗ‘дәҺжҰӮиҝ°еҸҜйҮҸеҢ–зҡ„жҠ–еҠЁйҷҗеҖјпјҢдҪҶ并没жңүжҸҗеҮәеӨҡе°‘жҢҮеҜјж„Ҹи§ҒжқҘеё®еҠ©зЎ®е®ҡеңЁзү№е®ҡеә”з”Ёж—¶е“ӘдёҖз§ҚйҷҗеҖјжӣҙдёәйҮҚиҰҒгҖӮеҗ„з§ҚеҪўејҸзҡ„жҠ–еҠЁйғҪжңүеҸҜиғҪе№Іжү°зі»з»ҹBERпјҢдёҚеҗҢзҡ„е·Ҙе…·еңЁжЈҖжөӢжҠ–еҠЁж—¶жңүдёҚеҗҢзҡ„дјҳеҠҝгҖӮ

жҲ‘们еңЁд№ӢеүҚзҡ„еҚҡж–ҮвҖңи§Јзӯ”еӨҙеҸ·йҡҫйўҳпјҡжҠ–еҠЁеҲҶжһҗи®ҫеӨҮзҡ„йҖүжӢ©пјҢд»ҘеҸҠи¶ізҗғеҒҸеҘҪй—®йўҳвҖқдёӯеҲҶжһҗдәҶеҗ„з§ҚжҠ–еҠЁеҲҶжһҗд»ӘпјҢж¬ўиҝҺжӮЁдёҺжҲ‘们еҲҶдә«жӮЁзҡ„жҠ–еҠЁжөӢиҜ•з»ҸйӘҢпјҢжҲ‘们е°ҶеңЁдёӢеӣһ继з»ӯи®Ёи®әгҖӮ

дҪңиҖ…пјҡжі°е…Ӣе…¬еҸё и¶ҠжөӢи¶ҠејҖеҝғеҚҡе®ўеӣўйҳҹ

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·