(3)、高、中、低速逻辑电路在PCB上要用不同区域。

(4)、安排电路时要使得信号线长度最小。

(5)、保证相邻板之间、同一板相邻层面之间、同一层面相邻布线之间不能有过长的平行信号线。

(6)、电磁干扰(EMI)滤波器要尽可能靠近EMI源,并放在同一块线路板上。

(7)、DC/DC变换器、开关元件和整流器应尽可能靠近变压器放置,以使其导线长度最小。

(8)、尽可能靠近整流二极管放置调压元件和滤波电容器。

(9)、印制板按频率和电流开关特性分区,噪声元件与非噪声元件要距离再远一些。

(10)、对噪声敏感的布线不要与大电流,高速开关线平行。

3、PCB布线

3.1、印刷线路板与元器件的高频特性:

一个PCB的构成是在垂直叠层上使用了一系列的层压、走线和预浸处理的多层结构。在多层PCB中,设计者为了方便调试,会把信号线布在最外层。

PCB上的布线是有阻抗、电容和电感特性的。

阻抗:布线的阻抗是由铜和横切面面积的重量决定的。例如,1盎司铜则有0.49mΩ/单位面积的阻抗。

电容:布线的电容是由绝缘体(EoEr)电流到达的范围(A)以及走线间距(h)决定的。

用等式表达为C=EoErA/h,Eo是自由空间的介电常数(8.854pF/m),Er是PCB基体的相关介电常数(在FR4碾压板中该值为4.7)

电感:布线的电感平均分布在布线中,大约为1nH/mm。

对于1盎司铜线来说,在0.25mm(10mil)厚的FR4碾压板上,位于地线层上方的0.5mm(20mil)宽、20mm(800mil)长的线能产生9.8mΩ的阻抗,20nH的电感以及与地之间1.66pF的耦合电容。

在高频情况下,印刷线路板上的走线、过孔、电阻、电容、接插件的分布电感与电容等不可忽略。电容的分布电感不可忽略,电感的分布电容不可忽略。电阻会产生对高频信号的反射和吸收。走线的分布电容也会起作用。当走线长度大于噪声频率相应波长的1/20时,就产生天线效应,噪声通过走线向外发射。

印刷线路板的过孔大约引起0.5pF的电容。一个集成电路本身的封装材料引入2~6pF电容。一个线路板上的接插件,有520nH的分布电感。一个双列直插的24引脚集成电路插座,引入4~18nH的分布电感。

这些小的分布参数对于运行在较低频率下的微控制器系统是可以忽略不计的;而对于高速系统必须予以特别注意。

下面便是避免PCB布线分布参数影响而应该遵循的一般要求:

(1)、增大走线的间距以减少电容耦合的串扰;

(2)、平行地布电源线和地线以使PCB电容达到最佳;

(3)、将敏感的高频线布在远离高噪声电源线的地方以减少相互之间的耦合;

(4)、加宽电源线和地线以减少电源线和地线的阻抗。

3.2、分割:

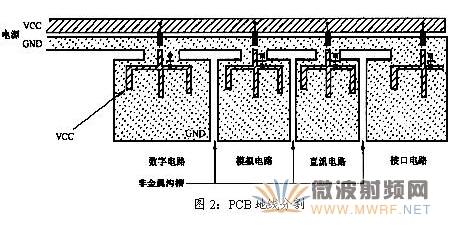

分割是指用物理上的分割来减少不同类型线之间的耦合,尤其是通过电源线和地线的耦合。

图2给出了用分割技术将4个不同类型的电路分割开的例子。在地线面,非金属的沟用来隔离四个地线面。L和C作为板子上的每一部分的过滤器,减少不同电路电源面间的耦合。高速数字电路由于其更高的瞬时功率需求而要求放在靠近电源入口处。接口电路可能会需要抗静电放电(ESD)和暂态抑制的器件或电路来提高其电磁抗扰性,应独立分割区域。对于L和C来说,最好不同分割区域使用各自的L和C,而不是用一个大的L和C,因为这样它便可以为不同的电路提供不同的滤波特性。

3.3、基准面的射频电流抑制:

不管是对多层PCB的基准接地层还是单层PCB的地线,电流的路径总是从负载回到电源。返回通路的阻抗越低,PCB的电磁兼容性能越好。由于流动在负载和电源之间的射频电流的影响,长的返回通路将在彼此之间产生射频耦合,因此返回通路应当尽可能的短,环路区域应当尽可能的小。

3.4、布线分离:

布线分离的作用是将PCB同一层内相邻线路之间的串扰和噪声耦合最小化。

所有的信号(时钟、视频、音频、复位等等)在线与线、边沿到边沿间应在空间上远离。为了进一步的减小电磁耦合,将基准地布放在关键信号附近或之间以隔离其他信号线上产生的或信号线相互之间产生的耦合噪声。

3.5、电源线设计:

根据印刷电路板电流的大小,尽量加粗电源线宽度,减少环路电阻。同时、使电源线、地线的走向和数据传递的方向一致,这样有助于增强抗噪声能力。

粤公网安备 44030902003195号

粤公网安备 44030902003195号