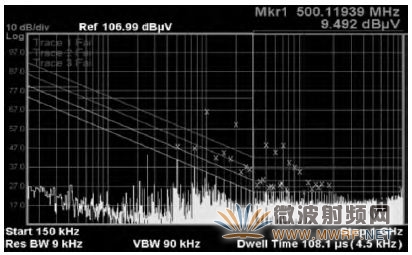

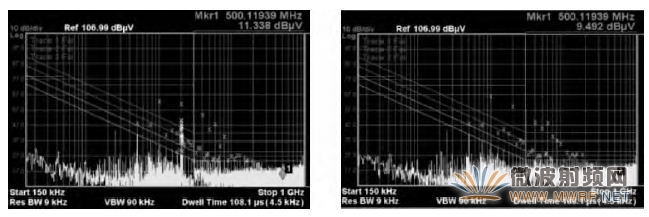

图7 10MHz—ADC测试图

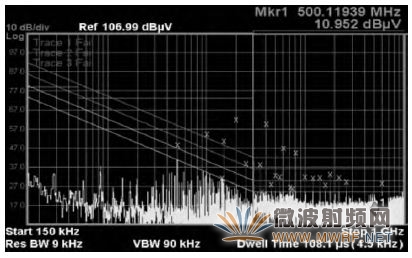

图8 20MHz—ADC测试图

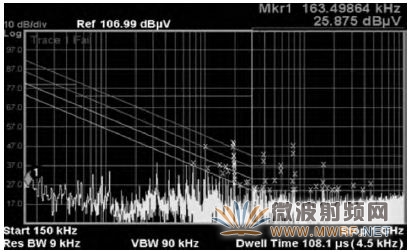

图9 77MHz—ADC测试图

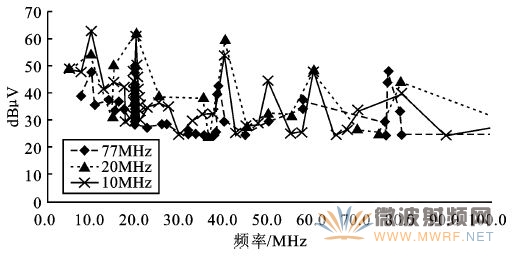

图10 10/20/77MHz—ADC测试数据整理

图7、图8、图9分别是10MHz、20MHz和77MHz的测试图,图10是整理后的数据。通过对比可以得出,频谱大致集中在100MHz以内,在对应工作时钟的主频点处干扰值最大,10MHz、20MHz情况下在相应倍频点(如40MHz、60MHz等频点)附近的干扰值也比较集中。

提取数据得到10 MHz时峰值点为9.999MHz(62.643dBμV),20 MHz 时的峰值点为20.002MHz(61.692dBμV),77MHz时的峰值点为19.264MHz(48.049dBμV)以及77.042MHz(47.316dBμV)。可以看出,77MHz时干扰强度和密度反而要弱于20MHz,可能是由于77MHz是MCU工作的极限时钟,此时工作性能受到一定影响,导致测试的结果有所不同。

③由于汽车电子MCU的工作时钟可以选择外部晶振或者内部PLL倍频,所以要对两种情况分别测试,以便比较是否有差别。运行ADC程序后的测试结果如图11所示。

图11 PLL vs.外部晶振(10MHz)

从图11中可以看出,在频谱范围内各个峰值点的分布大致相同,整个频谱范围内没有明显差异,MCU通过外部晶振或PLL倍频两种方式测得的结果基本一致,时钟源选择上不会对芯片的电磁干扰强度带来影响。

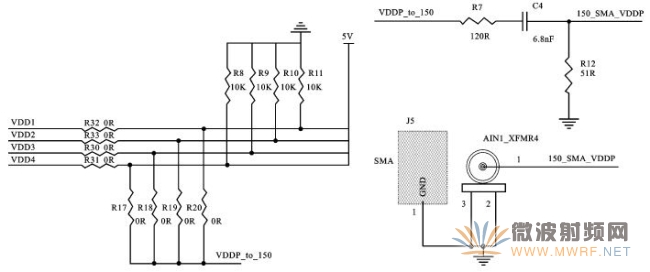

3.3 150Ω测试

(1)设备装置连接同1Ω测试法的步骤①;

(2)根据芯片电源类型,电源分为4路,分别是VDD1(数字IO 供电的5V 电源信号)、VDD2(为ADC和PLL供电的LDO 的5V 电压)、VDD3(数字逻辑LDO的5V电压输入)和VDD4(Flash的5V电压输入)。可单独对每一路电源的干扰噪声进行捕捉,连接方式与1Ω 测试法步骤②相同,如图12所示;

图12 VDD连接150Ω网络145

(3)根据汽车电子MCU应用特点,选取最为典型的PWM、CAN 程序,为了方便以后对众多引脚进行单独测量,将P0、P1、P2(P3未涉及到外设功能复用)端口共24个引脚进行了开关控制,再通过150Ω耦合网络连接到EMI接收机,图13是P0端口的电路原理图,P1和P2的原理图同P0。

图13 IO-P0连接150Ω网络

(4)重复测试多次,得到较多测试样本,经过整理,下面是各个测试情况的说明。

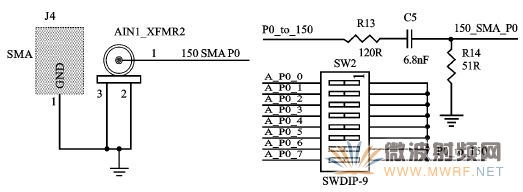

①从电源端口结果来看,区别很小,下面以VDD1为例进行分析说明。VDD1测试选取了ADC和counter(数字计数器)的程序,以比较不同类别的程序对数字供电是否有影响,测试结果如图14、图15所示。

在10MHz和20MHz时钟上对比,ADC最高峰值分别为35.827dBμV、43.517dBμV;counter的最高峰值为35.899dBμV、43.271dBμV。可以得出频率越高,干扰强度越大。但就两类程序横向对比来看,结果基本上一致。另外还发现60~300MHz和550~650MHz两处集中的干扰频谱,可见电源处的干扰在高频附近比较明显。

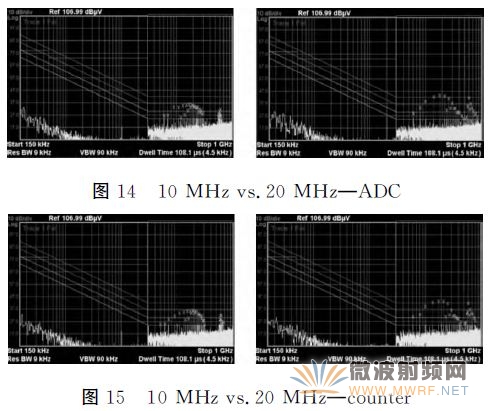

②PWM 功能测试

双通道模式下,在不同占空比和周期大小情况下,测试对应P口引脚处传导发射强度的大小,测试结果如图16、图17所示。

从图16中的干扰密度可看出时钟对电磁干扰影响程度。在图17中,由于period和duty较长,测试结果相差不大,此时时钟频率变成次要因素,主要因素取决于输出引脚处高低电平变化周期长短。

③CAN功能测试

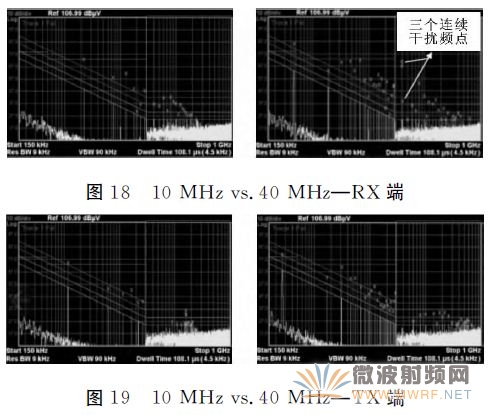

运行Loopback(回路模式)程序,在不同时钟频率下进行比较,测试结果如图18、图19所示。

从图16~19中观察,随着时钟频率变大,TX和RX端口的传导辐射强度也变大。对于RX端口,10/40MHz频点附近的干扰密度比较大,且在40MHz时候现象更明显,捕捉到连续三个频点(图18右侧标注),分别是39.060 MHz(71.063dBμV)、39.360MHz(67.447dBμV)、40.020MHz(39.171dBμV),两个时钟下的峰值都在70~85dBμV 之间,但一般都在10MHz以下,应该是受低频某一频点的影响较明显。

对于TX端口,10/40MHz频点附近的干扰密度没有RX明显,峰值也都在70~85dBμV 之间,且发生在10MHz以下,和RX的特点大致相同。

4、测试结果分析

从测试数据结果可以总结出以下几点:

①在时钟频率上,从10 MHz到40 MHz、77MHz,干扰强度或是密度在整体上都会增加,可以是一小段频谱或者是整个频谱范围内,这与测试对象关系比较大。分析原因不难发现,由于时钟电路产生的时钟信号一般都是周期信号,其频谱是离散的,离散谱的能量集中在有限的频率上,又由于系统中各个部分的时钟信号通常由同一时钟分频、倍频得到,它们的谱线之间也是倍频关系,会重叠起来进而增大辐射的幅值。

②在程序烧写方式上,外部晶振或PLL倍频两种方式测得的结果基本一致,整个频谱范围内没有明显差异,时钟源选择上不会对芯片的电磁干扰强度带来影响。

③从VDD1测试结果来看,除了得出频率越高,干扰强度越大之外,还发现出现干扰的频谱范围分别在60~300MHz和550~650MHz两处,可见电源处的干扰在高频附近比较明显。

④对于PWM 功能,通过配置输出波形周期和占空比大小,会导致在不同时钟下产生的电磁干扰强度有所差异。由于双通道模式下寄存器为16bit(原单通道模式为8bit),此时周期和占空比可配置的数值变大,PWM 波输出引脚处的高低电平翻转周期就取决于周期和占空比的设置,与时钟的关系变得没有之前如此紧密,时钟变成了次要因素。由此建议在满足功能要求的前提下,使用PWM 功能时尽量将周期和占空比数值变得大一些,这样会较好地改进EMC性能;

⑤对于CAN 总线来讲,通过10 MHz和40MHz时钟对比,当合理地降低时钟工作频率,会使一大段频谱范围内的干扰值降低,从整体上较好的控制EMI带来的影响。

5、结束语

对于微电子行业来说,芯片级电磁兼容性的设计与测试已经成为一个非常重要的主题。实际上,如果不对集成电路电磁辐射及抗扰度方面进行深入的研究,就很难满足电子设备电磁兼容性方面的需要。本文通过对设计方法的引入,并进一步通过测试方案去总结归纳影响电磁发射的因素和原因,从而间接证明了设计方法的必要性和重要性。

粤公网安备 44030902003195号

粤公网安备 44030902003195号